一种基于忆阻器的线性反馈混沌同步控制系统电路

本发明涉及混沌电路领域,尤其涉及一种基于忆阻器的线性反馈混沌同步控制系统电路。

背景技术:

1、忆阻器,全称记忆电阻器(memristor)。忆阻器是表示磁通与电荷关系的电路器件。忆阻具有电阻的量纲,但和电阻不同的是,忆阻的阻值是由流经它的电荷确定。因此,通过测定忆阻的阻值,便可知道流经它的电荷量,从而有记忆电荷的作用。1971年蔡少棠从逻辑和公理的观点指出,自然界应该还存在一个电路元件,它表示磁通与电荷的关系。2008年,惠普公司的研究人员首次做出纳米忆阻器件,掀起忆阻研究热潮。纳米忆阻器件的出现,有望实现非易失性随机存储器。并且,基于忆阻的随机存储器的集成度,功耗,读写速度都要比传统的随机存储器优越。此外,忆阻是硬件实现人工神经网络突触的最好方式。由于忆阻的非线性性质,可以产生混沌电路,从而在保密通信中也有很多应用。

2、在非线性动力学等领域,利用混沌同步实现数据保密通信引起广泛关注,传统混沌同步电路一般采用电阻耦合的方法实现,电阻耦合的混沌同步对阻抗匹配性要求较高,故较难实现在长时间及长距离的混沌数据保密通讯。而近年来提出的混沌同步系统,其中涉及的系统状态变量及其变量的微分量很难设计与公式相匹配的电路,大多数学者将所设计混沌同步系统的状态变量通过将系统模块化后再进行同步控制设计,虽可实现但增加了成本且电路干扰较大。

技术实现思路

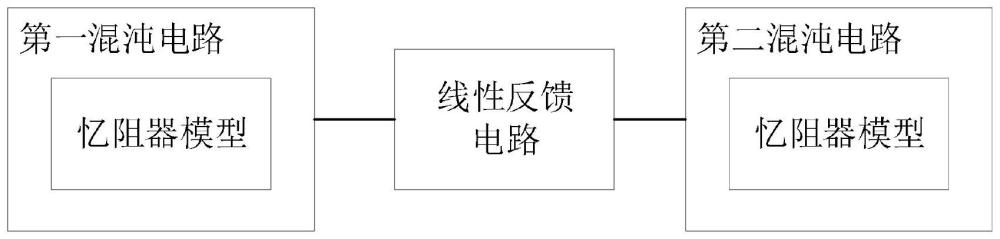

1、为了解决上述问题,本发明提出一种基于忆阻器的线性反馈混沌同步控制系统电路,包括:含有忆阻器模型的第一混沌电路、含有忆阻器模型的第二混沌电路、线性反馈电路,含有忆阻器模型的第一混沌电路和含有忆阻器模型的第二混沌电路通过线性反馈电路进行线性反馈耦合,实现两个混沌电路的同步;

2、所述第一混沌电路包括:第一求和电路、第一积分电路、第二积分电路、第三积分电路、第一反向电路、第二反向电路、第一放大电路、第二放大电路、第三放大电路、第四放大电路、第一乘法电路、第二乘法电路、第三乘法电路、第四乘法电路;

3、所述第二混沌电路包括:第二求和电路、第三求和电路、第四积分电路、第五积分电路、第六积分电路、第三反向电路、第五放大电路、第六放大电路、第七放大电路、第八放大电路、第五乘法电路、第六乘法电路、第七乘法电路、第八乘法电路;

4、线性反馈电路包括:第一差分放大电路、第二差分放大电路;

5、第一混沌电路中的忆阻器模型包括所述第三积分电路、所述第一乘法电路、所述第一放大电路、所述第二乘法电路、所述第二放大电路;第二混沌电路中的忆阻器模型包括所述第六积分电路、所述第五乘法电路、所述第五放大电路、所述第六乘法电路、所述第六放大电路;

6、第一混沌电路的输入信号xfg1经过第一求和电路,得到第一输出信号;所述第一输出信号经过第一积分电路进行积分,得到第二输出信号;所述第二输出信号经过第一反向电路进行反向,得到第三输出信号;所述第三输出信号经过第二积分电路进行积分,得到第四输出信号;所述第四输出信号经过第二反向电路进行反向,得到第五输出信号;所述第五输出信号经过第三积分电路进行积分,得到所述第六输出信号;所述第六输出信号经过第一乘法电路进行倍乘,得到第七输出信号;所述第七输出信号经过第一放大电路进行放大,得到第八输出信号;所述第八输出信号经过第二乘法电路与所述第五输出信号进行相乘,得到第九输出信号;所述第九输出信号经过第二放大电路进行放大,得到第十输出信号;所述第四输出信号经过第三乘法电路进行倍乘,得到第十一输出信号;所述第十一输出信号经过第三放大电路进行放大,得到第十二输出信号;所述第十二输出信号经过第四乘法电路与所述第三输出信号进行相乘,得到第十三输出信号;所述第十三输出信号经过第四放大电路进行放大,得到第十四输出信号;所述第二输出信号、所述第四输出信号、所述第十输出信号和所述第十四输出信号经过所述求和电路与所述信号xfg1进行反向相加;

7、第二混沌电路的输入信号xfg2经过第二求和电路,得到第十五输出信号;所述第十五输出信号经过第四积分电路进行积分,得到第十六输出信号;所述第十六输出信号经过第三求和电路,得到第十七输出信号;所述第十七输出信号经过第五积分电路进行积分,得到第十八输出信号;所述第十八输出信号经过第七反向电路进行反向,得到第十九输出信号;所述第十九输出信号经过第六积分电路进行积分,得到所述第二十输出信号;所述第二十输出信号经过第五乘法电路进行倍乘后,得到第二十一输出信号;所述第二十一输出信号经过第五放大电路进行放大后,得到第二十二输出信号;所述第二十二输出信号经过第六乘法电路与所述第十九输出信号进行相乘,得到第二十三输出信号;所述二十三输出信号经过第六放大电路进行放大后,得到第二十四输出信号;所述第十八输出信号经过第七乘法电路进行倍乘后,得到第二十五输出信号;所述第二十五输出信号经过第七放大电路进行放大后,得到第二十六输出信号;所述第二十六输出信号经过第八乘法电路与所述第十六输出信号进行相乘,得到第二十七输出信号;所述第二十七输出信号经过第八放大电路进行放大后,得到第二十八输出信号;

8、第四输出信号和第十八输出信号经过线性反馈电路的第一差分放大电路进行放大,得到第二十九输出信号;所述第二十九输出信号经过第二混沌电路的第三求和电路与所述第十六输出信号进行反向相加,得到第十七输出信号;所述第二输出信号和第十六输出信号经过线性反馈电路的第二差分放大电路进行放大后,得到第三十输出信号;

9、所述第十六输出信号、所述第十八输出信号、所述第三十输出信号、所述第二十四输出信号和所述第二十八输出信号经过所述第二求和电路与所述信号xfg2进行反向相加。

10、进一步地,第一混沌电路中,所述第一求和电路包括电阻r1、电阻r2、电阻r3、电阻r4、电阻r5、电阻r8和运算放大器u1a;所述第一积分电路包括电阻r9、电阻r10、电阻r68、电容c1、电容c2和运算放大器u1b;所述第一反向电路包括电阻r11、电阻r12和运算放大器u2a;所述第二积分电路包括电阻r13、电阻r14、电阻r16、电容c3、电容c4和运算放大器u2b;所述第二反向电路包括电阻r15、电阻r17和运算放大器u3a;所述第三积分电路包括电阻r18、电阻r19、电阻r20、电容c5、电容c6和运算放大器u3b;所述第一放大电路包括电阻r21、电阻r22和运算放大器u4a;所述第二放大电路包括电阻r23、电阻r24和运算放大器u4b;所述第三放大电路包括电阻r25、电阻r26和运算放大器u6a;所述第四放大电路包括电阻r27、电阻r28和运算放大器u6b;所述第一乘法电路包括乘法器u7;所述第二乘法电路包括乘法器u5;所述第三乘法电路包括乘法器u12;所述第四乘法电路包括乘法器u11;

11、第二混沌电路中,所述第二求和电路包括电阻r6、电阻r7、电阻r29、电阻r30、电阻r31、电阻r33、电阻r61和运算放大器u9a;所述第四积分电路包括电阻r34、电阻r37、电阻r69、电容c7、电容c8和运算放大器u9b;所述第三求和电路包括电阻r38、电阻r39、电阻r70、和运算放大器u10a;所述第五积分电路包括电阻r32、电阻r35、电阻r36、电容c9、电容c10和运算放大器u10b;所述第七反向电路包括电阻r40、电阻r41和运算放大器u13a;所述第六积分电路包括电阻r42、电阻r43、电阻r44、电容c11、电容c12和运算放大器u13b;所述第五放大电路包括电阻r45、电阻r46和运算放大器u14a;所述第六放大电路包括电阻r47、电阻r48和运算放大器u14b;所述第七放大电路包括电阻r51、电阻r52和运算放大器u15a;所述第八放大电路包括电阻r49、电阻r50和运算放大器u15b;所述第五乘法电路包括乘法器u16;所述第六乘法电路包括乘法器u17;所述第七乘法电路包括乘法器u18;所述第八乘法电路包括乘法器u19;

12、线性反馈电路中,所述第一差分放大电路包括电阻r57、电阻r58、电阻r59、电阻r60和运算放大器u8b;所述第二差分放大电路包括电阻r53、电阻r54、电阻r55、电阻r56和运算放大器u8a;

13、电阻r1的一端与运算放大器u1a的反相输入端相连,电阻r1的另一端与运算放大器u6b的输出端相连;电阻r2的一端与运算放大器u1a的反相输入端相连,电阻r2的另一端与运算放大器u1b的输出端相连;电阻r3的一端与运算放大器u1a的反相输入端相连,电阻r3的另一端与运算放大器u2b的输出端相连;电阻r4的一端与运算放大器u1的反相输入端相连,电阻r4的另一端与运算放大器u4b的输出端相连;电阻r5的一端与运算放大器u1a的反相输入端相连,电阻r5的另一端与信号源xfg1的正极相连;电阻r8的一端与运算放大器u1a的反相输入端相连,电阻r8的另一端与运算放大器u1a的输出端相连;运算放大器u1a的正相输入端接地,运算放大器u1a的输出端通过电阻r9与运算放大器u1b的反相输入端相连;

14、电阻r10与电容c1、电容c2并联形成第一并联网络,所述第一并联网络的一端与运算放大器u1b的反相输入端相连,所述第一并联网络的另一端与运算放大器u1b的输出端相连;运算放大器u1b的正相输入端通过电阻r68接地,运算放大器u1b的输出端通过电阻r11与运算放大器u2a的反相输入端相连,电阻r12的一端与运算放大器u2a的反相输入端相连,电阻r12的另一端与运算放大器u2a的输出端相连;运算放大器u2a的正相输入端接地,运算放大器u2a的输出端通过电阻r14与运算放大器u2b的反相输入端相连;

15、电阻r16与电容c3、电容c4并联形成第二并联网络,所述第二并联网络的一端与运算放大器u2b的反相输入端相连,所述第二并联网络的另一端与运算放大器u2b的输出端相连;运算放大器u2b的正相输入端通过电阻r13接地,运算放大器u2b的输出端通过电阻r15与运算放大器u3a的反相输入端相连;

16、电阻r17的一端与运算放大器u3a的反相输入端相连,电阻r17的另一端与运算放大器u3a的输出端相连;运算放大器u3a的正相输入端接地,运算放大器u3a的输出端通过电阻r18与运算放大器u3b的反相输入端相连;

17、电阻r20与电容c5、电容c6并联组成第三并联网络,所述第三并联网络的一端与运算放大器u3b的反相输入端相连,所述第三并联网络的另一端与运算放大器u3b的输出端相连;运算放大器u3b的正相输入端通过电阻r19接地,运算放大器u3b的输出端与乘法器u7的x1、y1端口相连,乘法器u7的x2、y2、z端口均接地,乘法器u7的输出端口与运算放大器u4a的正相输入端相连,电阻r22的一端与运算放大器u4a的反相输入端相连,电阻r22的另一端与运算放大器u4a的输出端相连,运算放大器u4a的反相输入端通过电阻r21接地;

18、乘法器u5的x1端口与运算放大器u4a的输出端相连,乘法器u5的y1端口与运算放大器u3a的输出端相连,乘法器u5的x2、y2、z端口均接地,乘法器u5的输出端口与运算放大器u4b的正相输入端相连,电阻r24的一端与运算放大器u4b的反相输入端相连,电阻r22的另一端与运算放大器u4b的输出端相连,运算放大器u4b的反相输入端通过电阻r23接地;

19、运算放大器u2b的输出端与乘法器u12的x1、y1端口相连,乘法器u12的x2、y2、z端口均接地,乘法器u12的输出端口与运算放大器u6a的正相输入端相连,电阻r26的一端与运算放大器u6a的反相输入端相连,电阻r26的另一端与运算放大器u6a的输出端相连,运算放大器u6a的反相输入端通过电阻r25接地;

20、乘法器u11的x1端口与运算放大器u2a的输出端相连,乘法器u11的y1端口与运算放大器u6a的输出端相连,乘法器u11的x2、y2、z端口均接地,乘法器u11的输出端口与运算放大器u6b的正相输入端相连,电阻r28的一端与运算放大器u6b的反相输入端相连,电阻r28的另一端与运算放大器u6b的输出端相连,运算放大器u6b的反相输入端通过电阻r27接地;

21、电阻r57的一端与运算放大器u2b的输出端相连,电阻r57的另一端与运算放大器u8b的正相输入端相连,电阻r58的一端与运算放大器u10b的输出端相连,电阻r58的另一端与运算放大器u8b的反相输入端相连,运算放大器u8b的正相输入端通过电阻r59接地,电阻r60的一端与运算放大器u8b的反相输入端相连,电阻r60的另一端与运算放大器u8b的输出端相连,运算放大器u8b的输出端通过电阻r70与运算放大器u10a的反相输入端相连;

22、电阻r53的一端与运算放大器u1b的输出端相连,电阻r53的另一端与运算放大器u8a的正相输入端相连,电阻r54的一端与运算放大器u9b的输出端相连,电阻r54的另一端与运算放大器u8a的反相输入端相连,运算放大器u8a的正相输入端通过电阻r55接地,电阻r56的一端与运算放大器u8a的反相输入端相连,电阻r56的另一端与运算放大器u8a的输出端相连;

23、电阻r7的一端与运算放大器u9a的反相输入端相连,电阻r7的另一端与运算放大器u9b的输出端相连;电阻r29的一端与运算放大器u9a的反相输入端相连,电阻r29的另一端与运算放大器u10b的输出端相连;电阻r31的一端与运算放大器u9a的反相输入端相连,电阻r31的另一端与运算放大器u8a的输出端相连;电阻r61的一端与运算放大器u9a的反相输入端相连,电阻r61的另一端与信号源xfg2的正极相连;电阻r6的一端与运算放大器u9a的反相输入端相连,电阻r6的另一端与运算放大器u14b的输出端相连;电阻r30的一端与运算放大器u9a的反相输入端相连,电阻r30的另一端与运算放大器u15b的输出端相连;电阻r33的一端与运算放大器u9a的反相输入端相连;电阻r33的另一端与运算放大器u9a的输出端相连,运算放大器u9a的正相输入端接地,运算放大器u9a的输出端通过电阻r34与运算放大器u9b的反相输入端相连;

24、电阻r37与电容c7、电容c8并联形成第四并联网络,所述第四并联网络的一端与运算放大器u9b的反相输入端相连,所述第四并联网络的另一端与运算放大器u9b的输出端相连;运算放大器u9b的正相输入端通过电阻r69接地,运算放大器u9b的输出端通过电阻r38与运算放大器u10a的反相输入端相连;

25、电阻r39的一端与运算放大器u10a的反相输入端相连,电阻r39的另一端与运算放大器u10a的输出端相连;运算放大器u10a的正相输入端接地,运算放大器u10a的输出端通过电阻r36与运算放大器u10b的反相输入端相连;

26、电阻r35与电容c9、电容c10并联形成第五并联网络,所述第五并联网络的一端与运算放大器u10b的反相输入端相连,所述第五并联网络的另一端与运算放大器u10b的输出端相连;运算放大器u10b的正相输入端通过电阻r32接地,运算放大器u10b的输出端通过电阻r40与运算放大器u13a的反相输入端相连;

27、电阻r41的一端与运算放大器u13a的反相输入端相连,电阻r41的另一端与运算放大器u13a的输出端相连;运算放大器u13a的正相输入端接地,运算放大器u13a的输出端通过电阻r42与运算放大器u13b的反相输入端相连;

28、电阻r44与电容c11、电容c12并联组成第六并联网络,所述第六并联网络的一端与运算放大器u13b的反相输入端相连,所述第六并联网络的另一端与运算放大器u13b的输出端相连;运算放大器u13b的正相输入端通过电阻r43接地,运算放大器u13b的输出端与乘法器u16的x1、y1端口相连,乘法器u16的x2、y2、z端口均接地,乘法器u16的输出端口与运算放大器u14a的正相输入端相连,电阻r46的一端与运算放大器u14a的反相输入端相连,电阻r46的另一端与运算放大器u14a的输出端相连,运算放大器u14a的反相输入端通过电阻r45接地;

29、乘法器u17的x1端口与运算放大器u13a的输出端相连,乘法器u17的y1端口与运算放大器u14a的输出端相连,乘法器u17的x2、y2、z端口均接地,乘法器u17的输出端口与运算放大器u14b的正相输入端相连,电阻r48的一端与运算放大器u14b的反相输入端相连,电阻r48的另一端与运算放大器u14b的输出端相连,运算放大器u14b的反相输入端通过电阻r47接地;

30、运算放大器u10b的输出端与乘法器u18的x1、y1端口相连,乘法器u18的x2、y2、z端口均接地,乘法器u18的输出端口与运算放大器u15a的正相输入端相连,电阻r52的一端与运算放大器u15a的反相输入端相连,电阻r52的另一端与运算放大器u15a的输出端相连,运算放大器u15a的反相输入端通过电阻r51接地;

31、乘法器u19的x1端口与运算放大器u9b的输出端相连,乘法器u19的y1端口与运算放大器u15a的输出端相连,乘法器u19的x2、y2、z端口均接地,乘法器u19的输出端口通过电阻r49与运算放大器u15b的反相输入端相连,电阻r50的一端与运算放大器u15b的反相输入端相连,电阻r50的另一端与运算放大器u15b的输出端相连,运算放大器u15b的正相输入端接地。

32、进一步地,运算放大器u1a、运算放大器u1b、运算放大器u2a、运算放大器u2b、运算放大器u3a、运算放大器u3b、运算放大器u4a、运算放大器u4b、运算放大器u6a、运算放大器u6b、运算放大器u8a、运算放大器u8b、运算放大器u9a、运算放大器u9b、运算放大器u10a、运算放大器u10b、运算放大器u13a、运算放大器u13b、运算放大器u14a、运算放大器u14b、运算放大器u15a、运算放大器u15b、均选用运算放大器tl082cd,电容c1=1.5nf、电容c2=91pf、电容c3=1.5nf、电容c4=91pf、电容c5=1.5nf、电容c6=91pf,电容c7=1.5nf、电容c8=91pf、电容c9=1.5nf、电容c10=91pf、电容c11=1.5nf、电容c12=91pf,乘法器u5、乘法器u7、乘法器u11、乘法器u12、乘法器u16、乘法器u17、乘法器u18、乘法器u19均选用四象限乘法器ad633an,电阻r1=20kω、电阻r2=20kω、电阻r3=10kω、电阻r4=10kω、电阻r5=10kω、电阻r6=10kω、电阻r7=20kω、电阻r8=10kω、电阻r9=100kω、电阻r10=100mω、电阻r11=10kω、电阻r12=10kω、电阻r13=100kω、电阻r14=100kω、电阻r15=10kω、电阻r16=100mω、电阻r17=10kω、电阻r18=100kω、电阻r19=100kω、电阻r20=100mω、电阻r21=1kω、电阻r22=9kω、电阻r23=1kω、电阻r24=9kω、电阻r25=1kω、电阻r26=9kω、电阻r27=1kω、电阻r28=9kω、电阻r29=10kω、电阻r30=20kω、电阻r31=10kω、电阻r32=100kω、电阻r33=10kω、电阻r34=100kω、电阻r35=100mω、电阻r36=100kω、电阻r37=100mω、电阻r38=10kω、电阻r39=10kω、电阻r40=100kω、电阻r41=100kω、电阻r42=100kω、电阻r43=100kω、电阻r44=100mω、电阻r45=1kω、电阻r46=9kω、r47=1kω、电阻r48=9kω、r49=10kω、电阻r50=100kω、r51=1kω、电阻r52=9kω、电阻r53=10kω、电阻r54=10kω、电阻r55=10kω、电阻r56=10kω、电阻r57=10kω、电阻r58=10kω、电阻r59=10kω、电阻r60=10kω、电阻r61=10kω、电阻r68=100kω、电阻r69=100kω、电阻r70=10kω。

33、进一步地,采用van derpol-duffing系统描述忆阻器模型:

34、

35、

36、

37、其中,x表示电压,a表示非线性阻尼系数,γ表示正弦信号的幅值,ω表示正弦信号的角频率,φ代表磁通量,q代表流经忆阻器的电荷量,α、β分别为忆阻器模型参数,根据α、β取值的不同,得到不同性能的忆阻器模型。

38、进一步地,所述同步控制系统电路分为驱动系统和响应系统两部分,所述第一混沌电路作为驱动系统,所述第二混沌电路作为响应系统,使用所述线性反馈电路控制响应系统,驱动系统自变量的运动轨迹不受响应系统的影响,响应系统受到驱动系统的控制,使驱动系统和响应系统同步。

39、进一步地,驱动系统表示为如下微分方程:

40、

41、其中,x1、x2、x3是驱动系统的三个状态变量,x1表示运算放大器u3b的输出端电压,x2表示运算放大器u2b的输出端电压,x3示运算放大器u1b的输出端电压。

42、进一步地,响应系统基于所述驱动系统,引入线性反馈驱动响应系统,表示为如下微分方程:

43、

44、其中,y1、y2、y3是响应系统的三个状态变量,y1表示运算放大器u13b的输出端电压,y2表示运算放大器u10b的输出端电压,y3表示运算放大器u9b的输出端电压,k表示反馈系数。

45、本发明提供的技术方案带来的有益效果是:

46、本发明涉及一种基于忆阻器的线性反馈混沌同步控制系统电路,包括:两个含有忆阻器模型的混沌电路和线性反馈电路,两个含有忆阻器模型的混沌电路通过线性反馈电路进行线性反馈耦合,采用驱动-响应同步法,根据设计的电路,设计驱动系统和响应系统,实现两个混沌系统的同步;本发明的方案对基于忆阻器的线性反馈混沌同步控制系统电路进行设计,实现了一种具有实时同步特性的混沌同步系统。

- 还没有人留言评论。精彩留言会获得点赞!