一种HART信号调制解调方法及装置与流程

本技术涉及通信,特别是涉及一种hart信号调制解调方法及装置。

背景技术:

1、hart(highway addressable remote transducer)是可寻址远程传感器高速通道的开放通信协议,hart协议采用基于bell202标准的fsk频移键控信号,在低频的4-20ma模拟信号上叠加幅度为0.5ma的音频数字信号进行双向数字通讯。由于数字fsk信号相位连续,平均值为0,不影响传送给控制系统模拟信号的大小。hart信号的逻辑“1”由1200hz的频率代表,逻辑“0”由2200hz的频率代表,信息传递速率为1200波特率。因此hart调制解调作是hart现场设备与客户其他设备交互信息的关键,使用的调制解调方法将直接影响设备使用效果。

2、目前,国内主流的hart调制解调方法是使用专用的hart调制解调芯片,但是芯片外围电路复杂,不可以多路并行调制解调。当有多路hart信号进行并行解调和调制的需求时,需要使用多片专用的hart芯片。在连接现场hart设备时,往往需要提供多路调制解调hart信号的能力,但是使用多片专用hart芯片的方案成本高,占用pcb空间大,也不利于系统的集成度。

3、由此,目前亟需一种方案,能够在对多路hart信号进行多路并行调制解调的同时,减少方案使用成本。

技术实现思路

1、基于上述问题,本技术提供了一种hatr信号调制解调方法及装置,能够在对多路hart信号进行多路并行调制解调的同时,减少方案使用成本。

2、本技术实施例公开了如下技术方案:

3、第一方面,本技术实施例提供了一种hart信号调制方法,所述方法包括:

4、在需要对n路hart信号进行调制时,根据一个整波中所包含的开关周期数s和一个开关周期中所包含的时钟周期数n获取一个开关周期中需要输出高电平的时钟周期个数d;

5、在fpga中建立对应相应通道的n个rom区域,以对d值进行存储;

6、响应于fpga对所述d值的调用,根据需要发送的数字信号选取对应的时钟周期的频率对d值进行读取;

7、将d值对应的spwm波进行rc滤波后输出,得到n路hart信号。

8、可选的,所述根据一个整波中所包含的开关周期数s和一个开关周期中所包含的时钟周期数n获取一个开关周期中需要输出高电平的时钟周期个数d,包括:

9、将一个整波分为s份,根据等面积原理计算每一份对应的占空比;s为一个整波中所包含的开关周期数;

10、根据将一个开关周期中所包含的时钟周期数n与该开关周期对应的占空比的乘积作为该开关周期中需要输出高电平的时钟周期个数d。

11、可选的,所述将一个整波分为s份,根据等面积原理计算每一份对应的占空比,包括:

12、将一个整波分为s份,计算每一份的面积;

13、将每一份的面积与1/s的比值作为该份对应的占空比。

14、可选的,所述在fpga中建立对应相应通道的n个rom区域,以对d值进行存储,包括:

15、在fpga中建立对应相应通道的n个rom区域;

16、对于每个rom区域,将对应的s个d值存储于该rom区域中;

17、每隔一个开关周期,根据所述s个d值对d值进行更新。

18、可选的,所述根据需要发送的数字信号选取对应的时钟周期的频率对d值进行读取,包括:

19、在需要发送的数字信号为1200hz时,选取时钟周期频率s·n·1200hz对d值进行读取;

20、在需要发送的数字信号为2200hz时,选取时钟周期频率s·n·2200hz对d值进行读取。

21、第二方面,本技术实施例提供了一种hart信号解调方法,所述方法包括:

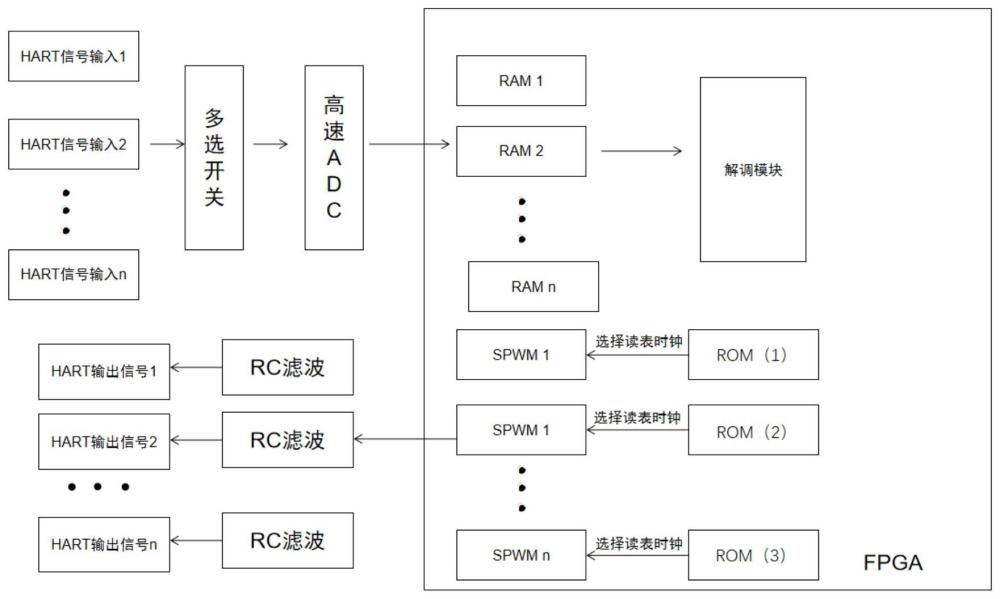

22、获取n路hart信号;

23、对于每路hart信号,利用带通滤波器将hart信号分为中心频率为1200hz的第一路信号和中心频率为2200hz的第二路信号;

24、将所述第一路信号和所述第二路信号分别进行全波整流和低通滤波;

25、将经过全波整流和低通滤波后的所述第一路信号和所述第二路信号相检;

26、利用抽样判决器对经过相检后的两路信号进行判决,以完成每路hart信号的解调。

27、可选的,所述获取n路hart信号,包括:

28、利用高速逐次逼近寄存器型模拟数字转换器sar adc和模拟开关对信号进行采样;

29、在fpga中建立对应相应通道的ram区域;

30、将对应通道的adc采样数据采用轮询的方式滚动存储至相应的ram区域;

31、利用fpga并行计算能力并行读取对应ram中的adc采样数据,得到n路hart信号。

32、第三方面,本技术实施例提供了一种hart信号调制装置,所述装置包括:

33、d值获取模块,用于在需要对n路hart信号进行调制时,根据一个整波中所包含的开关周期数s和一个开关周期中所包含的时钟周期数n获取一个开关周期中需要输出高电平的时钟周期个数d;

34、d值存储模块,用于在fpga中建立对应相应通道的n个rom区域,以对d值进行存储;

35、d值读取模块,用于响应于fpga对所述d值的调用,根据需要发送的数字信号选取对应的时钟周期的频率对d值进行读取;

36、hart信号输出模块,用于将d值对应的spwm波进行rc滤波后输出,得到n路hart信号。

37、可选的,所述d值获取模块,包括:

38、占空比计算子模块,用于将一个整波分为s份,根据等面积原理计算每一份对应的占空比;s为一个整波中所包含的开关周期数;

39、d值获取子模块,用于根据将一个开关周期中所包含的时钟周期数n与该开关周期对应的占空比的乘积作为该开关周期中需要输出高电平的时钟周期个数d。

40、第四方面,本技术实施例提供了一种hart信号解调装置,所述装置包括:

41、hart信号获取模块,用于获取n路hart信号;

42、信号分离模块,用于对于每路hart信号,利用带通滤波器将hart信号分为中心频率为1200hz的第一路信号和中心频率为2200hz的第二路信号;

43、整流滤波模块,用于将所述第一路信号和所述第二路信号分别进行全波整流和低通滤波;

44、信号相检模块,用于将经过全波整流和低通滤波后的所述第一路信号和所述第二路信号相检;

45、信号判决模块,用于利用抽样判决器对经过相检后的两路信号进行判决,以完成每路hart信号的解调。

46、相较于现有技术,本技术具有以下有益效果:

47、本技术实施例提供了一种hart信号调制解调方法,其中,hart信号调制方法包括:在需要对n路hart信号进行调制时,根据一个整波中所包含的开关周期数s和一个开关周期中所包含的时钟周期数n获取一个开关周期中需要输出高电平的时钟周期个数d;在fpga中建立对应相应通道的n个rom区域,以对d值进行存储;响应于fpga对所述d值的调用,根据需要发送的数字信号选取对应的时钟周期的频率对d值进行读取;将d值对应的spwm波进行rc滤波后输出,得到n路hart信号。hart信号解调方法包括:获取n路hart信号;对于每路hart信号,利用带通滤波器将hart信号分为中心频率为1200hz的第一路信号和中心频率为2200hz的第二路信号;将所述第一路信号和所述第二路信号分别进行全波整流和低通滤波;将经过全波整流和低通滤波后的所述第一路信号和所述第二路信号相检;利用抽样判决器对经过相检后的两路信号进行判决,以完成每路hart信号的解调。采用fpga并行输出spwm波的方式实现hart信号并行调制,相较于使用多个专用芯片进行hart信号并行调制,能够降低方案的使用成本;而采用fpga和高速adc配合的方式能够准确定位到hart信号,并且只需用到一个解调模块即可实现并行解调,能够节省了大量的逻辑资源和方案使用成本。

48、需要说明的是,本技术实施例提供的一种hart信号调制装置和一种hart信号解调装置由于能够实现上述方法的步骤,从而同样具备上述有益效果。

- 还没有人留言评论。精彩留言会获得点赞!