在陶瓷涂层中形成具有可调体积分数的纳米孪晶区

在陶瓷涂层中形成具有可调体积分数的纳米孪晶区

背景技术:

1.以下说明涉及在陶瓷薄膜中形成具有可调体积分数的纳米孪晶区。

2.轻质金属(例如钛合金)已成为汽车、航空航天、运输和许多其他行业的组成部分。它们通过提供减轻重量和成本效益性能的可能性,有助于提高这些行业的效率、性能和可持续制造。尽管轻质金属具有良好的强度重量比,但其趋于具有较低的硬度,并且对机械磨损表现出较差的抵抗力,这使得表面工程和高级涂层对于轻质金属在许多应用中的使用至关重要。

附图说明

3.图1是示出示例物理气相沉积(pvd)系统的各个方面的框图。

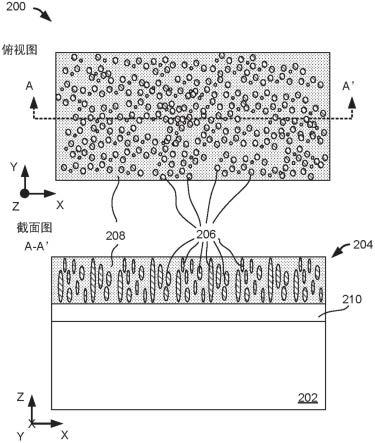

4.图2是示出示例设备的俯视图和截面图的示意图。

5.图3是示出示例工艺的各个方面的流程图。

6.图4a是示出示例陶瓷薄膜的各个方面的面内透射电子显微镜(tem)图像。

7.图4b是示出图4a所示的示例陶瓷薄膜的各个方面的截面tem图像。

8.图4c是示出图4b所示的示例陶瓷薄膜的截面高分辨率tem(hrtem)图像、示例陶瓷薄膜中纳米孪晶区的快速傅里叶变换(fft)图案以及对应的逆fft(ifft)图像。

9.图5是各种陶瓷薄膜上的表面在进行硬度测试后的光学显微图像。

10.图6a~6e是各种陶瓷薄膜的截面tem图像和相应的sad图案。

11.图7a是沉积在单晶mgo(111)衬底上的陶瓷薄膜的截面tem图像和相应的sad图案。

12.图7b是沉积在钛合金衬底上的陶瓷薄膜的截面tem图像和相应的sad图案。

具体实施方式

13.在此处描述的一些方面中,物理气相沉积(pvd)系统用于在衬底的表面上制造陶瓷薄膜。通过在pvd系统的处理室中执行两种或更多种溅射材料的共溅射处理来形成陶瓷薄膜。可在受控气体气氛中以受控压力水平执行共溅射处理。在一些实施方式中,包含钛、硼和氮的陶瓷薄膜通过在氮环境中共溅射钛金属靶和二硼化钛靶来制备。来自共溅射沉积处理的陶瓷薄膜具有异质结构,其中晶粒嵌入非晶基质中。每个晶粒包括纳米孪晶区。

14.在一些实施方式中,这里描述的系统和技术可以提供技术优势和改进。例如,使用此处介绍的方法和系统形成的陶瓷薄膜沉积在部件或组件的表面上以提高其机械属性,例如抗疲劳性、断裂韧性、硬度和其他机械属性。陶瓷薄膜中纳米孪晶区的体积分数可以通过调整沉积条件(例如功率、衬底偏压、气体成分、衬底温度等)在30%~80%的范围内调整以优化机械属性。使用此处介绍的方法和系统形成陶瓷薄膜可以在温和条件下进行,例如在室温至400摄氏度(℃)范围内的温度和0.1~0.35帕斯卡(pa)范围内的压力下进行。这里公开的低成本处理显著减少了处理时间和能量需求,并允许以工业规模在具有复杂几何形状的部件或组件的表面上形成这种陶瓷薄膜。在某些情况下,可以获得这些和潜在的其他优点和改进的组合。

15.图1是示出示例物理气相沉积(pvd)系统100的各个方面的示意图。示例物理气相沉积(pvd)系统100用于形成异质陶瓷薄膜。使用示例性pvd系统形成的异质陶瓷薄膜包括晶粒和其中嵌有晶粒的非晶基质。在一些实施方式中,使用pvd系统100制造的陶瓷薄膜中的每个晶粒包括一个或多个纳米孪晶区。纳米孪晶区在晶界中被识别为晶体的移动片段,其中每个边缘上的晶格通过镜像对称跨越假想的孪晶平面连接。陶瓷薄膜中纳米孪晶区的体积分数可以通过在制造工艺期间调整一种或多种沉积条件来调整。通过调整陶瓷薄膜中纳米孪晶区的体积分数,可以调整和优化陶瓷薄膜的机械属性(例如抗疲劳性、断裂韧性、硬度和其他属性)。

16.如图1所示,pvd系统100包括处理室102;并且处理室102包括结合在相应阴极104上的靶105。如这里的示例中所示,pvd系统100包括结合在三个相应阴极104a、104b、104c上的三个靶105a、105b、105c。在一些情况下,处理室102可以包括与更多靶105结合的更多阴极104,并且处理室102中的阴极104可以另一种方式布置。在一些实施方式中,靶104,包含溅射材料,所述溅射材料包括过渡金属(例如钛ti、钨w、钼mo、铌nb等)、金属合金、过渡金属硼化物(例如二硼化钛tib2)、过渡金属碳化物(例如一碳化钨wc)或其他溅射材料(例如碳c)。

17.如图1所示,处理室102包括衬底支架106,衬底支架106被配置为保持衬底107,衬底107在制造工艺期间面对靶105。pvd系统100中的衬底支架106位于处理室102的中心。带有衬底107的衬底支架106可以通过机械传送臂装载到pvd系统100中。在一些情况下,pvd系统100中的衬底支架106配备有温度控制元件(例如温度传感器、加热器或其他元件)。每个温度控制元件可通信地耦接到温度控制单元114。温度控制单元114可以位于处理室102内(例如封闭在法拉第屏蔽中以保护电子电路免受rf干扰),或者位于处理室102之外。在某些示例中,靶105a、105b、105c和相应的阴极104a、104b、104c可以通过由温度控制单元114控制的冷却剂来冷却。

18.在一些情况下,衬底107可以包括半导体材料(例如硅和锗)、金属(例如不锈钢)、金属合金(例如钛合金)、金属氧化物(例如氧化镁)、金属氮化物、或包括iii族、iv族和v族元素的其他材料。在一些情况下,衬底107可以是结晶的、多晶的或非晶的。在一些情况下,衬底107可以包括金属部件或组件,在所述金属部件或组件上需要进行表面处理以提高机械性能。

19.处理室102中的每个阴极104a、104b、104c都耦接到电源112。在一些实施方式中,pvd系统100是配置为阴极靶/阳极屏蔽布置的dc磁控溅射系统。在这种情况下,连接到每个阴极104a、104b的示例pvd系统100的电源112是dc放电电源。在一些情况下,电源112是射频(rf)电源和在从几十千赫(khz)到几十兆赫(mhz)的频率工作的相应匹配电路。在一些情况下,例如电感耦合等离子体、电子回旋共振、微波或螺旋波的其他技术可以与电源112集成以产生高密度放电,从而获得期望的沉积属性。通过在阴极104上施加电能,可以在处理室102中靠近靶105的空间中形成等离子体(例如包含电离原子或分子的气体)。在一些情况下,衬底支架106也可以耦接到电源112以吸引等离子体中的带电粒子,这些带电粒子被带电的处理气体分子(例如ar

+

)轰击离开靶105的表面。在一些情况下,衬底支架106可以耦接到电接地。

20.示例性pvd系统100包括一个或多个供气口110,供气口110用于从一个或多个相应

的外部气体管线接收处理气体并将处理气体供应到处理室102中。如图2所示,示例pvd系统100还包括真空口108,真空口108连接到具有一个或多个压力控制单元(例如真空泵、压力计或另一单元)的真空管线。在一些实施方式中,处理气体通过一个或多个供气口110供应到处理室102并通过真空口108泵出处理室102。一个或多个压力控制单元被配置为对处理室102进行抽气、并在处理室102中创建压力在0.1~0.35pa范围内的环境。在一些实施方式中,处理气体包括氮气(n2)、氩气(ar)或其他类型的气体。在一些其他情况下,处理气体可以包括反应气体,这取决于溅射沉积处理的类型和陶瓷薄膜的成分。例如,处理气体可以包括氧气(o2)、甲烷(ch4)、乙炔(c2h2)、氨(nh3)、硫化氢(h2s)或其他类型的反应气体。一个或多个供气口110可与靶105紧邻(例如在阴极104后面)。

21.在某些情况下,处理室102还可以配备有厚度监测系统(例如石英晶体监测仪、光谱椭偏仪、反射高能电子衍射检测器(rheed)或其他类型的系统)。在一些情况下,处理室102还包括用于各个靶105的遮挡板、旋转操纵器、观察口、传送口、感应线圈和其它组件。

22.pvd系统100可用于在衬底107上制造陶瓷薄膜。例如,可根据指定的配方在衬底107的表面上沉积陶瓷薄膜。该配方指定用于在处理室102中建立适当环境以沉积具有期望属性的陶瓷薄膜的参数。在一些实施方式中,配方指定以下参数中的一个或多个:供应到处理室102中的处理气体、沉积期间处理室102中的压力、供应给每个阴极104a、104b、104c和/或衬底支架106的电能参数(例如功率、电压、频率等)、衬底107的温度、沉积时间或其它参数。

23.如图1所示,温度控制单元114和电源112可通信地耦接到控制系统116。在一些情况下,控制系统116可以包括处理器、存储器和接收用户输入、控制温度控制单元114、电源112和pvd系统100的其他组件(例如压力控制单元)的操作以用于在制造工艺期间执行操作(例如关于图3中的示例工艺300的操作)的通信接口。

24.控制系统116的处理器可以实现为通用处理器、芯片多处理器(cmp)、专用处理器、嵌入式处理器、数字信号处理器(dsp)、网络处理器、输入/输出(i/o)处理器、媒体访问控制(mac)处理器、无线电基带处理器、协处理器、微处理器(例如复杂指令集计算机(cisc)微处理器、精简指令集计算(risc)微处理器、非常长的指令字(vliw)微处理器)、或其他处理设备。处理器还可以由控制器、微控制器、专用集成电路(asic)、现场可编程门阵列(fpga)、可编程逻辑器件(pld)或其他器件来实现。

25.控制系统116的存储器可以包括能够存储数据的机器可读或计算机可读介质,其包括易失性/非易失性存储器和可移除/不可移除存储器。存储器可以包括至少一个非易失性存储单元。非易失性存储单元能够存储一个或多个软件程序。软件程序例如可以包含应用程序、用户数据、设备数据和/或配置数据或其它类型的数据。

26.在某些示例中,存储器可以包括只读存储器(rom)、随机存取存储器(ram)、动态ram(dram)、双倍数据速率dram(ddr-ram)、同步dram(sdram)、静态ram(sram)、可编程rom(prom)、可擦可编程rom(eprom)、电可擦可编程rom(eeprom)、闪存(例如nor或nand闪存)、内容可寻址存储器(cam)、聚合物存储器(例如,铁电聚合物存储器)、相变存储器(例如奥氏(ovonic)存储器)、铁电存储器、氧化硅-氮化物-氧化-硅(sonos)存储器、盘存储器(例如软盘、硬盘、光盘、磁盘)、或卡(例如磁卡、光卡)或任何其他类型的适合存储信息的介质。在一些情况下,至少一种非暂时性计算机可读存储介质被包括在具有计算机可执行指令的存储

器中,当由处理器执行这些指令时,可以使处理器执行制造工艺(例如图3中的示例工艺300)。

27.在一些示例中,控制系统116的通信接口可以包括合适的机构或组件,以至少使用户能够向控制系统116提供输入并且使控制系统116能够向用户提供输出。例如,通信接口可以包括按钮、小键盘、键盘、点击轮、触摸屏或运动传感器。在一些情况下,通信接口可以包括用于提供对用户可见的显示的视觉外围输出设备。例如,视觉外围输出设备包括结合到pvd系统100的控制系统116中的屏幕(例如液晶显示器(lcd)屏幕)。在一些情况下,视觉外围输出设备可以包括编码器/解码器(也称为编解码器),以用于将数字媒体数据转换为模拟信号。例如,视觉外围输出设备可以包括视频编解码器、音频编解码器或任何其他合适类型的编解码器。

28.在某些示例中,通信接口可以包括能够将温度控制单元114和电源112耦接到控制系统116的任何合适的硬件、软件或硬件和软件的组合。通信接口可以被布置为使用期望的一组通信协议、服务或操作程序以控制信息信号的任何合适的技术来工作。通信接口可以包括适当的物理连接器以与相应的通信介质(例如有线或无线)连接。

29.图2是示出示例设备200的俯视图和截面图的示意图。示例设备200包括衬底202、中间层210和陶瓷薄膜204。衬底202可以实现为如图1所示的衬底107,或以另一种方式实现。在一些情况下,衬底202可以是多种工业应用中的机械组件或工具的一部分。在某些情况下,陶瓷薄膜204可用于提高衬底202的机械性能。例如,陶瓷薄膜204可用于提高衬底202的硬度、提高衬底202的寿命、提高衬底202的耐磨性、或用于其他目的。在一些实施方式中,使用pvd系统(例如图1所示的pvd系统100)或以另一种方式使得陶瓷薄膜204在衬底202上形成。如图2所示,陶瓷薄膜204具有异质结构,该异质结构包括嵌入非晶基质208中的晶粒206。陶瓷薄膜204的异质结构和机械属性可以通过调整制造工艺(例如如图3中所示的示例工艺300)的沉积条件或以其他方式来操纵。

30.在一些实施方式中,中间层210包括ti金属或另一种类型的材料。中间层210可以形成于衬底202的表面上以提高陶瓷薄膜204在衬底202上的结合或粘附性。在一些实施方式中,可以在陶瓷薄膜204的共溅射沉积之前使用pvd系统形成中间层210。中间层210可以具有10~150nm范围内的厚度。

31.在图2所示的示例设备200中,每个晶粒206沿陶瓷薄膜204的生长方向(例如沿z轴的长度方向)延伸。在一些其他情况下,每个晶粒206可以在相对于陶瓷薄膜的生长方向具有小偏移量(例如1度、5度、10度或其他值)的方向上延伸。如图2所示,每个晶粒206是一个维度(例如沿z轴)大于其他两个维度(例如x-y平面中的宽度方向)的细长颗粒。在一些情况下,陶瓷薄膜204中的晶粒206的宽度在3~30纳米(nm)、8~16nm或其他范围内。在一些实施方式中,陶瓷薄膜204的厚度在大于400nm、大于1000nm、大于2000nm或其他范围的范围内。在一些实施方式中,陶瓷薄膜204中的晶粒206和非晶基质208中的每一个包括一种或多种过渡金属、硼和氮。例如,陶瓷薄膜204中的过渡金属是钛(ti)。在一些实施方式中,陶瓷薄膜204中的硼浓度在2~18原子百分比的范围内。

32.在一些实施方式中,陶瓷膜204中的一个或多个晶粒206包括纳米孪晶区。在一些情况下,晶粒206中的纳米孪晶区在晶界中被识别为晶体的移位片段,其中每个边缘上的晶格通过镜像对称跨越假想孪晶面连接。陶瓷薄膜204中纳米孪晶区的体积分数在30~80%

的范围内。在一些实施方式中,晶粒中的一个或多个纳米孪晶区中的每一个中的孪晶间距在0.35~0.65纳米的范围内或在另一范围内。

33.图3是示出示例制造工艺300的各个方面的流程图。示例制造工艺300的各个方面可以在pvd系统(例如图1所示的pvd系统100)或在另一个系统中执行。示例制造工艺300可用于形成陶瓷薄膜(例如图2所示的陶瓷薄膜204)或用于制造设备(例如图2中所示的设备200)。示例工艺300可以包括其它的或不同的操作,并且这些操作可以按照所示的顺序或以另一种顺序来执行。在一些情况下,示例工艺300中的操作可以被合并、迭代或重复,或以另一种方式执行。

34.在302,提供两个或更多靶。在一些情况下,两个或更多靶(例如图1中的靶105)结合在pvd系统(例如图1中的pvd系统100)中的相应阴极(例如图1中的阴极104)上。在一些情况下,两个或更多靶包括一个钛金属靶和一个二硼化钛靶。在一些情况下,钛金属靶是高纯度钛靶(99.95%)。在一些情况下,各个阴极中的每一个电耦接到电源(例如图1中的电源112),该电源可以调节施加到两个或更多靶的电能。在一些实施方式中,电源是dc电源,其向pvd系统中的两个或更多靶供应dc电能。

35.在一些实施方式中,将一个或多个衬底装载到pvd系统的处理室(例如图1中的处理室102)中的衬底支架(例如图1中的衬底支架106)上。一个或多个衬底被配置在衬底支架上面对靶。一个或多个衬底中的每一个可以实施为如图1所示的衬底107。

36.在304,形成气体气氛。在一些实施方式中,在pvd系统的处理室中形成气体气氛。在一些实施方式中,气体气氛包括ar和n2的混合物。在一些实施方式中,气体气氛中的n2分数约为20%。在共溅射沉积期间,ar的流量为20sccm(标准立方厘米/分钟);n2的流量为5sccm。在共溅射沉积期间,流量在处理室中保持不变。处理室例如通过压力控制单元的操作被抽气;并且在共沉积处理期间,处理室内的气体气氛保持在0.2pa的压力。

37.在306,共溅射来自两个或更多靶的溅射材料。在一些实施方式中,可以加热衬底。例如,通过图1中的温度控制单元114的操作,可以将共溅射沉积期间的衬底的温度保持在等于或小于400摄氏度的温度。在一些实施方式中,在共溅射沉积期间不对衬底施加加热或冷却。

38.通过图1中的电源112的操作将电能施加到两个或更多靶上以导致共溅射。例如,当陶瓷薄膜含有氮化硼钛时,在高纯钛金属靶上施加450瓦的直流电,在二硼化钛靶上施加50~200瓦范围内的直流电。在一些实施方式中,在共溅射沉积期间将衬底偏置电压施加在衬底支架上。在一些情况下,衬底偏置电压在150~-50伏的范围内。在这些沉积条件下,使用0.1~0.8纳米/秒(nm s-1

)范围内的沉积速率在衬底的表面上沉积陶瓷薄膜。根据沉积速率,调整沉积时间,从而使得沉积在衬底的表面上的陶瓷薄膜的厚度等于或大于400纳米。

39.在一些实施方式中,在陶瓷薄膜的共溅射沉积之前,可以在衬底的表面上形成中间层以提高陶瓷薄膜与衬底的表面之间的粘附性。例如,钛金属中间层可以通过执行溅射沉积处理而沉积在衬底的表面上。例如,在由氩气组成的气体气氛中,在0.2pa的工作压力下,可以在衬底偏置电压为-110v的情况下将450瓦的直流电施加到高纯钛金属靶上。在衬底的表面上形成中间层后,进行共溅射沉积,在此期间陶瓷薄膜可以随后形成于中间层上。

40.图4a是示出了示例陶瓷薄膜的各个方面的面内透射电子显微镜(tem)图像400、402。图4b是示出了图4a所示的示例陶瓷薄膜的各个方面的截面tem图像410。图4c示出了图

4b所示的示例陶瓷薄膜的截面高分辨率tem(hrtem)图像420、纳米孪晶区的快速傅里叶变换(fft)图案422以及对应的逆fft(ifft)图像424。如图3中的示例制造工艺300中所述,通过在单晶硅基衬底上执行ti金属和tib2的共溅射沉积来沉积示例陶瓷薄膜。具体地,在ti靶上提供的第一电功率等于450瓦(w),在tib2靶上提供的第二电功率等于120w。在共溅射沉积期间,衬底支架上的硅基衬底加热至400摄氏度,并且-110v的衬底偏置电压施加在衬底支架上。分别以5sccm和20sccm的流量将氮气(n2)和氩气(ar)供应到处理室中。在沉积处理期间处理室中的工作压力保持在0.2pa。

41.在使用tem表征示例陶瓷薄膜之前,使用聚焦离子束(fib)在沿x-y平面和垂直于x-y平面(例如x-z平面)的方向上切割包括硅基衬底上的陶瓷薄膜的设备。如图4a中的面内tem图像400所示,陶瓷薄膜包括嵌入非晶基质中的纳米晶体。纳米晶体随机均匀地嵌入非晶基质中。x-y平面中纳米晶体的宽度在8~16nm的范围内。孪晶界垂直于膜的生长方向,并且两个孪晶相区的中间为非晶相。右上角的图是fft的结果。fft图案中的斑点表示孪晶的存在。这对应于表面tem样本的观察。纳米孪晶区可以在嵌入非晶基质中的晶粒中观察到。在一些情况下,纳米孪晶区被非晶基质包围或嵌入其中。

42.如截面hrtem图像420所示,fft图案422和对应于截面hrtem图像420中的框的逆fft图像424表示了纳米孪晶区的存在以及两个相邻纳米孪晶之间的原子排列。纳米孪晶的厚度约为2~3个原子层,或在0.35~0.65纳米的范围内。

43.图5是各种陶瓷薄膜上的表面在进行硬度测试后的光学显微图像500。使用物理气相沉积系统(例如图1中所示的物理气相沉积系统100)通过执行关于图3所示的示例制造工艺300的操作来制备陶瓷薄膜。每个示例陶瓷薄膜在以-110v的恒定衬底偏置电压沉积在400℃的单晶硅基衬底上。通过在硅基衬底上共溅射ti靶(450w的恒定dc功率)和tib2靶(各种dc功率,例如50w、80w、120w和200w)以在硅基衬底上沉积陶瓷薄膜。此处制备的所有陶瓷薄膜都具有相同的厚度(约为2微米(μm))。然后使用维氏(vickers)硬度测试方法测试陶瓷薄膜的韧性。如图5所示,在陶瓷薄膜的所有表面上都观察到残留印记。在tib2靶上施加80w和120w的dc功率时所沉积的陶瓷薄膜没有表示出在残留印记的角落处延伸的裂纹,这表明比在其他dc功率值下制备的陶瓷薄膜具有更高的韧性。

44.图6a~6e是如图5所示的各种陶瓷薄膜的截面tem图像600、610、620、630、640和对应的选择区衍射(sad)图案602、612、622、632、642。将每个示例陶瓷薄膜在以110v的恒定衬底偏置电压沉积在单晶硅基衬底上。通过共溅射ti(在恒定dc功率值450w)和tib2(在各种dc功率值,例如50w(图6a)、80w(图6b)、120w(图6c)、160w(图6d)和200w(图6e)),从而在硅基衬底上制备陶瓷薄膜。所有陶瓷薄膜的厚度约为2μm。

45.陶瓷薄膜中的原子比(ti∶b∶n)通过执行配备在tem仪器中的能量色散x射线分析(edx)来确定。具体地,在tib2靶上施加50w的dc功率所沉积的第一陶瓷薄膜的原子比(ti∶b∶n)被确定为1∶0.04∶1.06。第一陶瓷薄膜的截面形态和对应的图案如图6a所示。第一陶瓷薄膜中b的原子比约为1.9%。第一陶瓷薄膜中纳米孪晶区的体积分数约为45%。第一陶瓷薄膜的硬度约为43.2gpa。

46.在tib2靶上施加80w的dc功率所沉积的第二陶瓷薄膜的原子比(ti∶b∶n)被确定为1∶0.14∶1.16。第二陶瓷薄膜的截面形态和对应的sad图案如图6b所示。第二陶瓷薄膜中b的原子比约为6.0%。第二陶瓷薄膜中纳米孪晶区的体积分数约为65%。第二陶瓷薄膜的硬度

约为41.5gpa。

47.在tib2靶上施加120w的dc功率所沉积的第三陶瓷薄膜的原子比(ti∶b∶n)被确定为1∶0.26∶1.20。第三陶瓷薄膜的截面形态及对应的图形如图6c所示。第三陶瓷薄膜中b的原子比约为10.6%。第三陶瓷薄膜中纳米孪晶区的体积分数约为55%。第三陶瓷薄膜的硬度约为38.8gpa。

48.在tib2靶上施加160w的dc功率所沉积的第四陶瓷薄膜的原子比(ti∶b∶n)被确定为1∶0.31∶1.19。第四陶瓷薄膜的截面形态和对应的sad图形如图6d所示。第四陶瓷薄膜中b的原子比约为12.4%。第四陶瓷薄膜中纳米孪晶区的体积分数约为42%。第四陶瓷薄膜的硬度约为35.9gpa。

49.在tib2靶上施加200w的dc功率所沉积的第五陶瓷薄膜的原子比(ti∶b∶n)被确定为1∶0.40∶1.32。第五陶瓷薄膜的截面形态和对应的sad图形如图6e所示。第五陶瓷薄膜中b的原子比为14.7%。如图6e中的截面tem图像640所示,在第五陶瓷薄膜中没有观察到纳米孪晶区。第五陶瓷薄膜的硬度约为33.1gpa。

50.图7a~7b是沉积在单晶mgo(111)衬底(图7a)和钛合金衬底(图7b)上的陶瓷薄膜的截面tem图像700、710和对应的图案702、712。使用物理气相沉积(pvd)系统(例如图1中所示的物理气相沉积系统100)通过执行关于图3中所示的示例性制造工艺300的操作来制备陶瓷薄膜。具体来说,在jcp500 pvd溅射系统中使用高纯度ti靶(99.99%)和tib2靶共溅射陶瓷薄膜。所有陶瓷薄膜的沉积均在400℃的恒定衬底温度和-110v的恒定衬底偏置电压下进行。在包括ar/n2气体混合物的气体气氛中以20sccm(ar)/5sccm(n2)的流量比进行共溅射沉积。在共溅射沉积处理期间,处理室中的气体气氛保持在0.2pa的压力。施加在ti靶和tib2靶上的直流电功率分别设定为450w和80w的恒定值。钛合金衬底为ti6-al4-v衬底。

51.陶瓷薄膜中的原子比(ti∶b∶n)通过执行配备在tem仪器中的能量色散x射线分析(edx)来确定。单晶mgo(111)衬底上陶瓷薄膜的原子比(ti∶b∶n)确定为1∶0.12∶1.18。单晶mgo(111)衬底上的陶瓷薄膜中b的原子比约为5.2%。单晶mgo(111)衬底上陶瓷薄膜中的纳米孪晶区的体积分数约为60.8%。单晶mgo(111)衬底上的陶瓷薄膜的硬度约为41.9gpa。

52.钛合金衬底上陶瓷薄膜的原子比(ti∶b∶n)确定为1∶0.12∶1.18。钛合金衬底上的陶瓷薄膜中b的原子比为5.8%。钛合金衬底上陶瓷薄膜中纳米孪晶区的体积分数约为63.6%。钛合金衬底上陶瓷薄膜的硬度约为40.9gpa。

53.本说明书中描述的一些主题和操作可以在数字电子电路或计算机软件、固件或硬件(包括本说明书中公开的结构及其结构等同物,或它们中的一个或多个的组合)中实现。本说明书中描述的一些主题可以实现为在计算机存储介质上编码的一个或多个计算机程序,即一个或多个计算机程序指令模块,其由数据处理装置执行或控制数据处理装置的操作。计算机存储介质可以是或可以包含在计算机可读存储设备、计算机可读存储衬底、随机或串行存取存储器阵列或设备、或它们中的一个或多个的组合中。此外,虽然计算机存储介质不是传播信号,但计算机存储介质可以是在人工生成的传播信号中编码的计算机程序指令的源或目的地。计算机存储介质也可以是或包含在一个或多个单独的物理组件或介质中。

54.本说明书中描述的一些操作可以实现为由数据处理装置对存储在一个或多个计算机可读存储设备上或从其他源接收的数据执行的操作。

55.术语“数据处理装置”包括用于处理数据的所有类型的装置、设备和机器,例如包括可编程处理器、计算机、片上系统或前述的多个或组合。该装置可以包括专用逻辑电路,例如fpga(现场可编程门阵列)或asic(专用集成电路)。除了硬件之外,该装置还可以包括为所讨论的计算机程序创建执行环境的代码,例如包括构成处理器固件、协议栈、数据库管理系统、操作系统、跨平台运行时的代码环境、虚拟机或其中一个或多个的组合的代码。

56.计算机程序(也称为程序、软件、软件应用程序、脚本或代码)可以用任何形式的编程语言编写,编程语言包括编译或解释语言、声明或步骤语言,并且计算机程序可以任何形式(包括作为独立程序或作为模块、组件、子程序、对象或适合在计算环境中使用的其他单元)部署。计算机程序可以但不必对应于文件系统中的文件。程序可以存储在包含其他程序或数据的文件的一部分中(例如存储在标记语言文档中的一个或多个脚本)、专用于该程序的单个文件中或多个协调文件(例如存储一个或多个模块的文件、子程序或部分代码)中。计算机程序可以部署为在一台计算机上或位于一个站点或分布在多个站点并通过通信网络互连的多台计算机上执行。

57.本说明书中描述的一些步骤和逻辑流程可以由执行一个或多个计算机程序的一个或多个可编程处理器来执行,以通过对输入数据进行操作并生成输出来执行动作。步骤和逻辑流程也可以由专用逻辑电路执行,并且装置也可以实现为专用逻辑电路(例如fpga(现场可编程门阵列)或asic(专用集成电路))。

58.在上述内容的总体方面中,公开了制造具有纳米孪晶区的陶瓷薄膜。

59.在第一示例中,公开了一种用于在真空室中的衬底的表面上制造陶瓷薄膜的方法。陶瓷薄膜包括多个晶粒;每个晶粒包括一个或多个纳米孪晶区。一个或多个纳米孪晶区的体积分数在陶瓷薄膜的30~80%范围内。准备包括多种溅射材料的多个靶。形成在真空室中的气体气氛。向多个靶供应电能以引起多种溅射材料的共溅射,从而形成具有一个或多个纳米孪晶区的陶瓷薄膜。

60.第一示例的实施方式可以包括以下特征中的一个或多个。衬底包括不锈钢、金属合金、硅或氧化镁中的一种。衬底包括钛合金。多个靶包括第一靶和第二靶。第一靶包括钛金属;第二靶包括硼化钛。气体气氛包括氮气。陶瓷薄膜包括钛、氮和硼。陶瓷薄膜中的多个晶粒嵌入非晶基质中。晶粒和非晶基质包括钛、硼和氮。气体气氛还包括氩气;气体气氛中的氮分数约为20%。陶瓷薄膜的硼浓度在2~18原子百分比的范围内。每个晶粒的尺寸在8~16纳米的范围内。一个或多个纳米孪晶区中的每一个中的孪晶间距在0.35~0.65纳米的范围内。

61.第一示例的实施方式可以包括以下特征中的一个或多个。多种溅射材料以0.1~0.8纳米/秒范围内的沉积速率共溅射在衬底的表面上。陶瓷薄膜的厚度等于或大于400纳米。在衬底上施加-150~-50伏范围内的衬底偏压。在等于或小于400摄氏度的温度下,将多种溅射材料共溅射在衬底的表面上。在不对衬底施加加热或冷却的情况下共溅射多种溅射材料。当供应电能时,第一dc功率施加在第一靶上;第二dc功率施加在第二靶上。第一dc功率等于450瓦,第二dc功率在50~200瓦的范围内。在向多个靶供应电能之前,在衬底的表面上形成中间层;并且通过将多种溅射材料共溅射在中间层上形成陶瓷薄膜。

62.在第二示例中,公开了一种在真空室中的衬底的表面上制造陶瓷薄膜的方法。陶瓷薄膜包括多个晶粒。每个晶粒包括一个或多个纳米孪晶区。提供了包括多种溅射材料的

多个靶。在真空室中形成气体气氛。向多个靶供应电能以引起多种溅射材料的共溅射,从而以0.1~0.8纳米/秒的沉积速率形成包括一个或多个纳米孪晶区的陶瓷薄膜。

63.在第三个示例中,一种设备包括:具有表面的衬底;和陶瓷薄膜。陶瓷薄膜位于衬底的表面上以增强衬底的机械属性。陶瓷薄膜包括多个晶粒。每个晶粒包括一个或多个纳米孪晶区,纳米孪晶区的体积分数在陶瓷薄膜的30~80%范围内。

64.在第四示例中,陶瓷薄膜包括多个晶粒。每个晶粒包含一个或多个纳米孪晶区,纳米孪晶区的体积分数在陶瓷薄膜的30~80%范围内。

65.虽然本说明书包含许多细节,但这些不应被理解为对权利要求的范围的限制,而是对具体示例的具体特征的描述。在本说明书中描述或在单独实施方式的上下文中的附图中示出的某些特征也可以组合。相反,在单个实施方式的上下文中描述或示出的各个特征也可以单独地在多个实施例中实现或以任何合适的子组合实现。

66.类似地,虽然在附图中以特定顺序描述了各个操作,但这不应被理解为要求这些操作以所示的特定顺序或按顺序执行,或者要求执行所有图示的操作以获得期望的结果。在某些情况下,多任务和并行处理可能是有利的。此外,上述实施方式中各种系统组件的分离不应理解为在所有实施方式中都要求这种分离,而应理解为所描述的程序组件和系统通常可以集成在一个产品中或打包成多个产品。

67.已经描述了许多实施例。然而,应当理解,可以进行各种修改。因此,其他实施例在以下权利要求的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1