包括定制位的集成电路的制作方法

包括定制位的集成电路

背景技术:

1.作为流体喷射系统的一个示例,喷墨打印系统可以包括打印头、向打印头供应液体墨水的墨水供应器、以及控制打印头的电子控制器。作为流体喷射设备的一个示例,打印头通过多个喷嘴或孔口并向打印介质(如一张纸)喷射墨滴,以在打印介质上进行打印。在一些示例中,孔口被布置成至少一个列或阵列,使得当打印头和打印介质相对于彼此移动时,从孔口进行的适当顺序的墨水喷射使得字符或其他图像打印在打印介质上。

附图说明

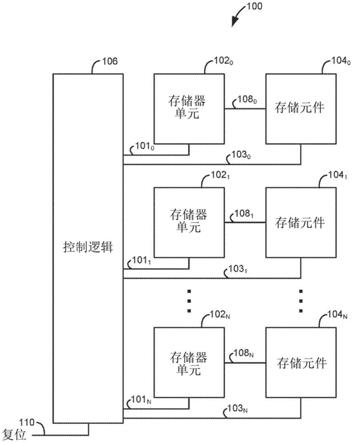

2.图1a是图示了用于驱动多个流体致动设备的集成电路的一个示例的框图。

3.图1b是图示了用于驱动多个流体致动设备的集成电路的另一个示例的框图。

4.图2是图示了用于驱动多个流体致动设备的集成电路的另一个示例的框图。

5.图3a是图示了用于访问存储有定制位的存储器单元的电路的一个示例的示意图。

6.图3b是图示了用于访问存储有锁定位的存储器单元的电路的一个示例的示意图。

7.图4a至图4c是图示了用于对用于驱动多个流体致动设备的集成电路进行复位的方法的示例的流程图。

8.图5a和图5b图示了流体喷射管芯的一个示例。

9.图6是图示了流体喷射系统的一个示例的框图。

具体实施方式

10.在以下具体实施方式中,对附图进行了参考,这些附图形成具体实施方式的一部分,并且在附图中通过说明的方式示出了可以实践本公开的具体示例。应当理解的是,在不脱离本公开的范围的情况下,可以利用其他示例并且可以做出结构或逻辑变化。因此以下具体实施方式不应当被理解为限制性的意义,并且本公开的范围由所附权利要求限定。应当理解的是,除非另外特别指出,否则本文所描述的各种示例的特征可以部分地或全部地彼此组合。

11.对于不同的地理区域、对于订阅或非订阅客户或出于其他原因,让集成电路(例如,半导体管芯)具有不同的表现可能具有优势。相比于制作被设计成具有不同表现的多个物理集成电路(这可能必须单独地跟踪或分开管理),可能更容易的是将一些非易失性存储器位写入到集成电路(例如,在制造期间)以改变集成电路的行为。

12.因此,本文公开了包括各自存储有定制位的多个存储器单元和存储有锁定位的一个存储器单元的集成电路(例如,流体喷射管芯)。所述集成电路还包括耦接到每个存储器单元的存储元件(例如,锁存器)。当复位信号被施加到集成电路时,存储器单元被内部读取并且定制位和锁定位被存储元件锁存。复位之后,锁存的定制位和锁定位可以用于控制集成电路的操作。锁存的锁定位可以允许或阻止对存储器单元的写入访问和外部读取访问和/或允许或阻止集成电路的其他操作。定制位可以用于修改输入到集成电路的地址或修改集成电路的其他操作。

13.如本文所使用的,“逻辑高”信号是逻辑“1”或“导通”信号或具有约等于供应到集成电路的逻辑电力的电压(例如,在约1.8v与15v之间,如5.6v)的信号。如本文所使用的,“逻辑低”信号是逻辑“0”或“关断”信号或具有约等于供应到集成电路的逻辑电力的逻辑电力接地回路的电压(例如,约0v)的信号。

14.图1a是图示了用于驱动多个流体致动设备的集成电路100的一个示例的框图。集成电路100包括多个第一存储器单元1020到102

n

,其中,“n”是任何合适的存储器单元数量(例如,四个存储器单元)。集成电路100还包括多个第一存储元件1040到104

n

和控制逻辑106。控制逻辑106分别通过信号路径1010到101

n

电耦接到每个第一存储器单元1020到102

n

,分别通过信号路径1030到103

n

电耦接到每个第一存储元件1040到104

n

,并且电耦接到复位信号路径110。每个第一存储器单元1020到102

n

分别通过信号路径1080到108

n

电耦接到对应的第一存储元件1040到104

n

。

15.复位信号路径110可以电耦接到复位接口,所述复位接口可以是接触焊盘、引脚、凸块、导线或用于向和/或从集成电路100传输信号的其他合适的电接口。复位接口可以电耦接到流体喷射系统(例如,主机打印装置,如下文将参考图6所描述的流体喷射系统600)。

16.每个第一存储器单元1020到102

n

存储定制位。每个第一存储器单元1020到102

n

包括非易失性存储器单元(例如,浮栅晶体管、可编程熔丝等)。每个第一存储元件1040到104

n

包括锁存器或输出可以由数字逻辑直接使用的逻辑信号(即,逻辑高信号或逻辑低信号)的另一个合适电路。控制逻辑106可以包括微处理器、专用集成电路(asic)或用于控制集成电路100的操作的其他合适的逻辑电路。

17.响应于复位信号路径110上的复位信号,控制逻辑106读取(例如,响应于复位信号的第一边沿)存储在每个第一存储器单元1020到102

n

中的定制位并且锁存(例如,响应于复位信号的第二边沿)对应的第一存储元件1040到104

n

中的每个定制位。在一个示例中,控制逻辑106基于锁存的定制位来配置集成电路100的操作。在一个示例中,所述操作可以基于锁存的定制位来修改输入到集成100的地址。在其他示例中,可以基于锁存的定制位来修改集成电路100的其他操作。

18.图1b是图示了用于驱动多个流体致动设备的集成电路120的另一个示例的框图。集成电路120包括多个第一存储器单元1020到102

n

、多个第一存储元件1040到104

n

和控制逻辑106。另外,集成电路120包括第二存储器单元122、第二存储元件124、写入电路130和读取电路132。控制逻辑106通过信号路径121电耦接到第二存储器单元122并且通过信号路径123电耦接到存储元件124。第二存储器单元122通过信号路径128电耦接到存储元件124。每个第一存储器单元1020到102

n

、第二存储器单元122、写入电路130和读取电路132电耦接到单个接口(例如,单个导线)134。读取电路132电耦接到接口(例如,感测接口)136。

19.感测接口136可以是接触焊盘、引脚、凸块、导线或用于向和/或从集成电路120传输信号的其他合适的电接口。感测接口136可以电耦接到流体喷射系统(例如,主机打印装置,如图6的流体喷射系统600)。

20.第二存储器单元122存储锁定位。第二存储器单元122包括非易失性存储器单元(例如,浮栅晶体管、可编程熔丝等)。第二存储元件124包括锁存器或输出可以由数字逻辑直接使用的逻辑信号(即,逻辑高信号或逻辑低信号)的另一个合适电路。响应于复位信号,控制逻辑106读取(例如,响应于复位信号的第一边沿)存储在第二存储器单元122中的锁定

位并且锁存(例如,响应于复位信号的第二边沿)第二存储元件124中的锁定位。另外,控制逻辑106基于锁存的锁定位允许或阻止写入到多个第一存储器单元1020到102

n

。在一个示例中,控制逻辑106还基于锁存的锁定位允许或阻止写入到第二存储器单元122。例如,如果“0”锁定位存储在第二存储器单元122中,则可以修改存储在第一存储器单元1020到102

n

中的定制位。一旦“1”锁定位被写入到第二存储器单元122,就无法修改存储在第一存储器单元1020到102

n

中的定制位并且无法修改存储在第二存储器单元122中的锁定位。

21.写入电路130通过单个接口134将对应的定制位写入到多个第一存储器单元1020到102

n

中的每一个。写入电路130还可以通过单个接口134将锁定位写入到第二存储器单元122。在一个示例中,写入电路130可以包括电压调节器和/或用于将定制位写入到第一存储器单元1020到102

n

并且将锁定位写入到第二存储器单元122的其他合适的逻辑电路。

22.读取电路132启用外部访问(例如,经由感测接口136)以通过单个接口134读取多个第一存储器单元1020到102

n

中的每一个的定制位。读取电路132还可以启用外部访问(例如,经由感测接口136)以通过单个接口134读取第二存储器单元122的锁定位。在一个示例中,读取电路132可以包括晶体管开关或用于通过感测接口136启用对第一存储器单元1020到102

n

和第二存储器单元122的外部读取访问的其他合适的逻辑电路。在一个示例中,控制逻辑106基于锁存的锁定位允许或阻止对多个第一存储器单元1020到102

n

和第二存储器单元122的外部读取访问。例如,如果“0”锁定位存储在第二存储器单元122中,则存储在第一存储器单元1020到102

n

中的定制位和存储在第二存储器单元122中的锁定位可以通过读取电路132读取。一旦“1”锁定位被写入到第二存储器单元122,存储在第一存储器单元1020到102

n

中的定制位和存储在第二存储器单元122中的锁定位就无法通过读取电路132读取。

23.图2是图示了用于驱动多个流体致动设备的集成电路200的另一个示例的框图。集成电路200包括多个第一存储器单元2020到202

n

、多个第一锁存器2040到204

n

、第二存储器单元222、第二锁存器224和控制逻辑206。控制逻辑206分别通过信号路径2010到201

n

电耦接到每个第一存储器单元2020到202

n

,分别通过信号路径2030到203

n

电耦接到每个第一锁存器2040到204

n

,通过信号路径221电耦接到第二存储器单元222,通过信号路径223电耦接到锁存器224,并且电耦接到复位信号路径210。每个第一存储器单元2020到202

n

分别通过信号路径2080到208

n

电耦接到对应的第一锁存器2040到204

n

。第二存储器单元222通过信号路径228电耦接到第二锁存器224。

24.每个第一存储器单元2020到202

n

存储有用于配置集成电路200的操作的定制位。每个第一存储器单元2020到202

n

包括非易失性存储器单元(例如,浮栅晶体管、可编程熔丝等)。每个锁存器2040到204

n

分别对应于第一存储器单元2020到202

n

,并且输出可以由数字逻辑直接使用的逻辑信号(即,逻辑高信号或逻辑低信号)。第二存储器单元222存储用于允许或阻止对多个第一存储器单元2020到202

n

的外部访问的锁定位。第二存储器单元222包括非易失性存储器单元(例如,浮栅晶体管、可编程熔丝等)。第二锁存器224对应于第二存储器单元222,并且输出可以由数字逻辑直接使用的逻辑信号(即,逻辑高信号或逻辑低信号)。控制逻辑206可以包括微处理器、专用集成电路(asic)、或用于控制集成电路200的操作的其他合适的逻辑电路。

25.响应于复位信号路径210上的复位信号,控制逻辑206(例如,响应于复位信号的第一边沿)读取存储在第二存储器单元222中的锁定位并且(例如,响应于复位信号的第二边

沿)将锁定位锁存在第二锁存器224中。还响应于复位信号,控制逻辑206(例如,响应于复位信号的第一边沿)读取存储在每个第一存储器单元2020到202

n

中的定制位并且(例如,响应于复位信号的第二边沿)将每个定制位锁存在对应的第一锁存器2040到204

n

中。在一个示例中,控制逻辑206基于锁定位允许或阻止对第一存储器单元2020到202

n

和第二存储器单元222的外部访问。

26.图3a是图示了用于对存储有定制位的存储器单元进行访问的电路300的一个示例的示意图。在一个示例中,电路300是图1a的集成电路100、图1b的集成电路120或图2的集成电路200的一部分。电路300包括存储器单元302、锁存器304、内部(复位)读取电压调节器306、写入电压调节器308、反相器310、与门312和316、或门314和318、晶体管320和322以及感测焊盘324。存储器单元302包括浮栅晶体管330和晶体管332、334和336。

27.反相器310的输入电耦接到锁定信号路径340。反相器310的输出通过信号路径311电耦接到与门312的第一输入。与门312的第二输入电耦接到定制位使能信号路径338。与门312的第三输入电耦接到选择信号(addr[x],其对应于来自喷嘴数据流的y个地址位之一,其中,“y”是任何合适的位数量(例如,4))路径342。与门312的输出通过信号路径313电耦接到或门314的第一输入。或门314的第二输入电耦接到复位信号路径344。或门314的输出通过信号路径315电耦接到存储器单元302的晶体管332的栅极和锁存器304的栅极(g)输入。

[0028]

与门316的第一输入电耦接到写入使能信号路径346。与门316的第二输入电耦接到激发信号路径348。与门316的输出通过信号路径317电耦接到存储器单元302的晶体管334的栅极。或门318的第一输入电耦接到激发信号路径348。或门318的第二输入电耦接到复位信号路径344。或门318的输出通过信号路径319电耦接到存储器单元302的晶体管336的栅极。

[0029]

内部(复位)读取电压调节器306的输入电耦接到复位信号路径344。内部(复位)读取电压调节器306的输出通过信号路径323电耦接到存储器单元302的浮栅晶体管330的源极

‑

漏极路径的一侧。写入电压调节器308的输入电耦接到存储器写入信号路径350。写入电压调节器308的输出通过信号路径323电耦接到存储器单元302的浮栅晶体管330的源极

‑

漏极路径的一侧。感测焊盘324电耦接到晶体管320的源极

‑

漏极路径的一侧。晶体管320的栅极和晶体管322的栅极电耦接到读取使能信号路径352。晶体管320的源极

‑

漏极路径的另一侧通过信号路径321电耦接到晶体管322的源极

‑

漏极路径的一侧。晶体管322的源极

‑

漏极路径的另一侧通过信号路径323电耦接到存储器单元302的浮栅晶体管330的源极

‑

漏极路径的一侧。

[0030]

浮栅晶体管330的源极

‑

漏极路径的另一侧通过信号路径331电耦接到晶体管332的源极

‑

漏极路径的一侧和锁存器304的数据(d)输入。锁存器304的另一个输入电耦接到预设信号路径354。锁存器304的输出(q)电耦接到定制位信号路径356。晶体管332的源极

‑

漏极路径的另一侧通过信号路径333电耦接到晶体管334的源极

‑

漏极路径的一侧和晶体管336的源极

‑

漏极路径的一侧。晶体管334的源极

‑

漏极路径的另一侧电耦接到公共或接地节点335。晶体管336的源极

‑

漏极路径的另一侧电耦接到公共或接地节点335。

[0031]

尽管电路300包括用于存储定制位的一个存储器单元302和一个对应的锁存器304,但是电路300可以包括用于存储期望数量的定制位的任何合适数量的存储器单元302和对应的锁存器304。对于每个定制位,每个存储器单元和对应的锁存器将以与针对存储器

单元302和锁存器304所描述的方式类似的方式进行存取。

[0032]

电路300接收定制使能信号路径338上的定制使能信号、锁定信号路径340上的锁定信号、选择信号路径342上的地址或选择信号、复位信号路径344上的复位信号、写入使能信号路径346上的写入使能信号、激发信号路径348上的激发信号、存储器写入信号路径350上的存储器写入信号、读取使能信号路径352上的读取使能信号以及预设信号路径354上的预设信号。预设信号可以用于在测试期间对锁存器304进行覆写,以从锁存器304输出期望的逻辑电平。定制使能信号和锁定信号可以用于启用或禁用对存储定制位的存储器单元的写入访问和外部读取访问。地址信号可以用于选择存储定制位的存储器单元之一。定制使能信号、写入使能信号、存储器写入信号、读取使能信号和预设信号可以基于存储在配置寄存器(未示出)中的数据,或者基于从主机打印装置接收的数据。锁定信号是从锁存器输出的内部信号,如图2的锁存器224。

[0033]

地址信号是(如通过数据接口)从主机打印装置接收的。复位信号可以通过复位接口从主机打印装置接收。激发信号可以通过激发接口从主机打印装置接收。数据接口、复位接口和激发接口中的每一个可以包括接触焊盘、引脚、凸块、导线或用于向和/或从电路300传输信号的其他合适的电接口。数据接口、复位接口、激发接口和感测焊盘324中的每一个可以电耦接到流体喷射系统(例如,主机打印装置,如图6的流体喷射系统600)。

[0034]

反相器310接收锁定信号并且在信号路径311上输出反相锁定信号。响应于逻辑高定制使能信号、逻辑高反相锁定信号、以及逻辑高选择信号,与门312在信号路径313上输出逻辑高信号。响应于逻辑低定制使能信号、逻辑低反相锁定信号、或逻辑低选择信号,与门312在信号路径313上输出逻辑低信号。

[0035]

响应于信号路径313上的逻辑高信号或逻辑高复位信号,或门314在信号路径315上输出逻辑高信号。响应于信号路径313上的逻辑低信号和逻辑低复位信号,或门314在信号路径315上输出逻辑低信号。响应于逻辑高写入使能信号和逻辑高激发信号,与门316在信号路径317上输出逻辑高信号。响应于逻辑低写入使能信号或逻辑低激发信号,与门316在信号路径317上输出逻辑低信号。响应于逻辑高激发信号或逻辑高复位信号,或门318在信号路径319上输出逻辑高信号。响应于逻辑低激发信号和逻辑低复位信号,或门318在信号路径319上输出逻辑低信号。

[0036]

响应于信号路径315上的逻辑高信号,晶体管332导通(即,传导)以启用对存储器单元302的访问。响应于信号路径315上的逻辑低信号,晶体管332关断以禁用对存储器单元302的访问。响应于信号路径317上的逻辑高信号,晶体管334导通以启用对存储器单元302的写入访问。响应于信号路径317上的逻辑低信号,晶体管334关断以禁用对存储器单元302的写入访问。响应于信号路径319上的逻辑高信号,晶体管336导通以启用对存储器单元302的读取访问。响应于信号路径319上的逻辑低信号,晶体管336关断以禁用对存储器单元302的读取访问。在一个示例中,晶体管334是较强的设备,并且晶体管336是较弱的设备。因此,较强的设备可以用于启用写入访问,并且较弱的设备可以用于启用读取访问以改善用于锁存信号路径331上的电压的裕量。

[0037]

响应于逻辑高复位信号,启用内部(复位)读取电压调节器306以将读取电压偏置输出到信号路径323。响应于逻辑低复位信号,禁用内部(复位)读取电压调节器306。因此,响应于从逻辑低转变到逻辑高的复位信号,晶体管332和336导通并且内部(复位)读取电压

调节器306被启用以读取浮栅晶体管330的状态(即,表示所存储的定制位的电阻)。浮栅晶体管330的状态被传递到锁存器304的数据(d)输入(即,作为表示所存储的定制位的电压)。响应于从逻辑高转变到逻辑低的复位信号,存储在浮栅晶体管330中的定制位被锁存器304锁存,晶体管332和336关断,并且内部(复位)读取电压调节器306被禁用。因此,定制位然后在锁存器304的输出(q)上可用,并且因此在定制位信号路径356上可用以用于于其他数字逻辑。

[0038]

响应于逻辑高读取使能信号,晶体管320和322导通以启用通过感测焊盘324对存储器单元302的外部访问。响应于逻辑低读取使能信号,晶体管320和322关断以禁用通过感测焊盘324对存储器单元302的外部访问。因此,响应于逻辑高定制使能信号、逻辑低锁定信号、逻辑高地址信号、逻辑高读取使能信号和逻辑高激发信号,晶体管320、322、332和336导通以允许浮栅晶体管330由外部电路通过感测焊盘324读取。

[0039]

响应于逻辑高存储器写入信号,启用写入电压调节器308以将写入电压施加到信号路径323。响应于逻辑低存储器写入信号,禁用写入电压调节器308。因此,响应于逻辑高定制使能信号、逻辑低锁定信号、逻辑高地址信号、逻辑高写入使能信号、逻辑高存储器写入信号和逻辑高激发信号,晶体管332、334、和336导通以允许浮栅晶体管330由写入电压调节器308写入。

[0040]

图3b是图示了用于对存储锁定位的存储器单元进行访问的电路370的一个示例的示意图。在一个示例中,电路370是图1b的集成电路120或图2的集成电路200的一部分。电路370类似于先前参考图3a所描述和图示的电路300,除了在电路370中,存储器单元302用存储器单元372替换,并且锁存器304用锁存器374替换。存储器单元372存储锁定位并且锁存器374响应于复位信号锁存锁定位。

[0041]

存储器单元372类似于先前描述的存储器单元302。锁存器374类似于先前描述的锁存器304,除了锁存器374不包括预设信号输入。锁存器374的输出(q)在锁定信号路径340上提供锁定信号,所述锁定信号是对反相器310的输入(还参见图3a的反相器310)。代替输入到与门312的选择信号,喷嘴数据锁定位信号通过喷嘴数据锁定位信号路径376输入到与门312。喷嘴数据锁定位信号可以用于选择存储器单元372。喷嘴数据锁定位信号可以基于如通过数据接口从主机打印装置接收的数据。如先前所描述的,类似于图3a的存储器单元302,可以启用存储器单元372以进行写入或读取访问。

[0042]

图4a至图4c是图示了用于对用于驱动多个流体致动设备的集成电路进行复位的方法400的示例的流程图。在一个示例中,方法400可以由图1a的集成电路100、图1b的集成电路120、图2的集成电路200、图3a的电路300和/或图3b的电路370实施。如图4a所图示的,在402处,方法400包括响应于复位信号而读取集成电路的多个第一存储器单元,每个第一存储器单元存储定制位。在404处,方法400包括将每个定制位锁存在集成电路的多个第一锁存器中的对应的第一锁存器中,每个第一锁存器对应于第一存储器单元。在406处,方法400包括基于锁存的定制位来配置集成电路的操作。在一个示例中,配置集成电路的操作可以包括基于锁存的定制位来修改输入到集成电路的地址。

[0043]

如图4b所图示的,在408处,方法400可以进一步包括响应于复位信号而读取集成电路的第二存储器单元,所述第二存储器单元存储锁定位。在410处,方法400可以进一步包括将锁定位锁存在集成电路的第二锁存器中。在412处,方法400可以进一步包括基于锁存

的锁定位而允许或阻止写入到多个第一存储器单元。如图4c所图示的,在414处,方法400可以进一步包括基于锁存的锁定位而允许或阻止写入到第二存储器单元。也可以基于锁存的锁定位来允许或阻止外部读取。

[0044]

图5a图示了流体喷射管芯500的一个示例,并且图5b图示了流体喷射管芯500的端部的放大视图。在一个示例中,流体喷射管芯500包括图1a的集成电路100、图1b的集成电路120、图2的集成电路200、图3a的电路300和/或图3b的电路370。管芯500包括第一列接触焊盘502、第二列接触焊盘504和一列506流体致动设备508。

[0045]

第二列接触焊盘504与第一列接触焊盘502对齐并且与第一列接触焊盘502相距一定距离(即,沿y轴)。所述一列506流体致动设备508相对于第一列接触焊盘502和第二列接触焊盘504纵向布置。所述一列506流体致动设备508也布置在第一列接触焊盘502与第二列接触焊盘504之间。在一个示例中,流体致动设备508是用于喷射液滴的喷嘴或流体泵。

[0046]

在一个示例中,第一列接触焊盘502包括六个接触焊盘。第一列接触焊盘502可以依次包括以下接触焊盘:数据接触焊盘510、时钟接触焊盘512、逻辑电力接地回路接触焊盘514、多用途输入/输出接触(例如,感测)焊盘516、第一高压电力供应接触焊盘518和第一高压电力接地回路接触焊盘520。因此,第一列接触焊盘502包括处于第一列502顶部的数据接触焊盘510、处于第一列502底部的第一高压电力接地回路接触焊盘520以及第一高压电力接地回路接触焊盘520正上方的第一高压电力供应接触焊盘518。尽管以特定顺序图示了接触焊盘510、512、514、516、518和520,但在其他示例中,接触焊盘可以以不同顺序布置。

[0047]

在一个示例中,第二列接触焊盘504包括六个接触焊盘。第二列接触焊盘504可以依次包括以下接触焊盘:第二高压电力接地回路接触焊盘522、第二高压电力供应接触焊盘524、逻辑复位接触焊盘526、逻辑电力供应接触焊盘528、模式接触焊盘530和激发接触焊盘532。因此,第二列接触焊盘504包括处于第二列504顶部的第二高压电力接地回路接触焊盘522、第二高压电力接地回路接触焊盘522正下方的第二高压电力供应接触焊盘524以及处于第二列504底部的激发接触焊盘532。尽管以特定顺序图示了接触焊盘522、524、526、528、530和532,但在其他示例中,接触焊盘可以以不同顺序布置。

[0048]

数据接触焊盘510可以用于将串行数据输入到管芯500以用于选择流体致动设备、存储器位、热传感器、配置模式(例如经由配置寄存器)等。数据接触焊盘510还可以用于从管芯500输出串行数据,用于读取存储器位、配置模式、状态信息(例如,经由状态寄存器)等。时钟接触焊盘512可以用于将时钟信号输入到管芯500以将数据接触焊盘510上的串行数据移位到管芯中或将串行数据移位出管芯到数据接触焊盘510。逻辑电力接地回路接触焊盘514为供应到管芯500的逻辑电力(例如,约0v)提供接地回路路径。在一个示例中,逻辑电力接地回路接触焊盘514电耦接到管芯500的半导体(例如,硅)衬底540。多用途输入/输出接触焊盘516可以用于管芯500的模拟感测和/或数字测试模式。在一个示例中,多用途输入/输出接触(例如,感测)焊盘516可以提供图1b的感测接口136或图3a和图3b的感测焊盘324。

[0049]

第一高压电力供应接触焊盘518和第二高压电力供应接触焊盘524可以用于将高压(例如,约32v)供应到管芯500。第一高压电力接地回路接触焊盘520和第二高压电力接地回路接触焊盘522可以用于为高压电力供应器提供电力接地回路(例如,约0v)。高压电力接地回路接触焊盘520和522不直接电连接到管芯500的半导体衬底540。将高压电力供应接触

焊盘518和524以及高压电力接地回路接触焊盘520和522作为最里面的接触焊盘的特定接触焊盘顺序可以改善到管芯500的电力输送。在第一列502的底部和第二列504的顶部分别具有高压电力接地回路接触焊盘520和522可以改善制造的可靠性并且可以改善墨水短路保护。

[0050]

逻辑复位接触焊盘526可以用作逻辑复位输入以控制管芯500的操作状态。在一个示例中,逻辑复位接触焊盘526可以电耦接到图1a和图1b的复位信号路径110、图2的复位信号路径210、或图3a和图3b的复位信号路径344。逻辑电力供应接触焊盘528可以用于将逻辑电力(例如,在约1.8v与15v之间,如5.6v)供应到管芯500。模式接触焊盘530可以用作逻辑输入以控制访问从而启用/禁用管芯500的配置模式(即,功能模式)。激发接触焊盘532可以用作逻辑输入以锁存来自数据接触焊盘510的经加载数据并且启用管芯500的流体致动设备或存储器元件。在一个示例中,激发接触焊盘532可以电耦接到图3a和图3b的激发信号路径348。

[0051]

管芯500包括具有长度542(沿y轴)、厚度544(沿z轴)和宽度546(沿x轴)的细长衬底540。在一个示例中,长度542是宽度546的至少二十倍。宽度546可以是1mm或更小并且厚度544可以小于500微米。流体致动设备508(例如,流体致动逻辑)和接触焊盘510至532提供在细长衬底540上并且沿细长衬底的长度542布置。流体致动设备508具有小于细长衬底540的长度542的条带长度552。在一个示例中,条带长度552为至少1.2cm。接触焊盘510到532可以电耦接到流体致动逻辑。第一列接触焊盘502可以布置在细长衬底540的第一纵向端部548附近。第二列接触焊盘504可以布置在细长衬底540的与第一纵向端部548相对的第二纵向端部550附近。

[0052]

图6是图示了流体喷射系统600的一个示例的框图。流体喷射系统600包括流体喷射组件,如打印头组件602,以及流体供应组件,如墨水供应组件610。在所图示的示例中,流体喷射系统600还包括服务站组件604、托架组件616、打印介质传输组件618和电子控制器620。尽管以下描述提供了用于关于墨水进行流体处理的系统和组件的示例,但是所公开的系统和组件也适用于处理除墨水之外的流体。

[0053]

打印头组件602包括先前参考图5a和图5b所描述和图示的至少一个打印头或流体喷射管芯500,所述至少一个打印头或流体喷射管芯通过多个孔口或喷嘴508喷射墨滴或液滴。在一个示例中,液滴被引导朝向介质,如打印介质624,以打印到打印介质624上。在一个示例中,打印介质624包括任何类型的合适的片材,如纸、卡片纸、透明胶片、聚酯薄膜、织物等。在另一个示例中,打印介质624包括用于三维(3d)打印的介质,如粉末床,或用于生物打印和/或药物发现测试的介质,如储液器或容器。在一个示例中,喷嘴508布置成至少一个列或阵列,使得当打印头组件602和打印介质624相对于彼此移动时,从喷嘴508进行的适当排序的油墨喷射使得字符、符号和/或其他图形或图像打印在打印介质624上并且。

[0054]

墨水供应组件610向打印头组件602供应墨水并且包括用于储存墨水的储液器612。因此,在一个示例中,墨水从储液器612流动到打印头组件602。在一个示例中,打印头组件602和墨水供应组件610一起容纳在喷墨或流体喷射打印墨盒或笔中。在另一个示例中,墨水供应组件610与打印头组件602分开并且通过接口连接613(如供应管和/或阀)将墨水供应到打印头组件602。

[0055]

托架组件616相对于打印介质传输组件618定位打印头组件602,并且打印介质传

输组件618相对于打印头组件602定位打印介质624。因此,打印区626被限定成在打印头组件602与打印介质624之间的区域中与喷嘴508相邻。在一个示例中,打印头组件602是扫描型打印头组件,使得托架组件616相对于打印介质传输组件618移动打印头组件602。在另一个示例中,打印头组件602是非扫描型打印头组件,使得托架组件616相对于打印介质传输组件618将打印头组件602固定在规定的位置处。

[0056]

服务站组件604提供打印头组件602的喷射、擦拭、加盖和/或灌注以维持打印头组件602——并且更具体地——喷嘴508的功能。例如,服务站组件604可以包括橡胶刀片或擦拭器,所述橡胶刀片或擦拭器周期性地经过打印头组件602以擦拭和清洁喷嘴508上的过量墨水。另外,服务站组件604可以包括覆盖打印头组件602的盖,用于在不使用时段期间保护喷嘴508免于变干。另外,服务站组件604可以包括墨盂,打印头组件602在吐出期间将墨水喷射到所述墨盂中以确保储液器612维持适当水平的压力和流动性,并且确保喷嘴508不会堵塞或渗漏。服务站组件604的功能可以包括服务站组件604与打印头组件602之间的相对运动。

[0057]

电子控制器620通过通信路径603与打印头组件602通信,通过通信路径605与服务站组件604通信,通过通信路径617与托架组件616通信,并且通过通信路径619与打印介质传输组件618通信。在一个示例中,当打印头组件602安装在托架组件616中时,电子控制器620和打印头组件602可以通过通信路径601经由托架组件616进行通信。电子控制器620还可以与墨水供应组件610通信,使得在一种实施方式中,可以检测到新的(或使用过的)墨水供应器。

[0058]

电子控制器620从如计算机等主机系统接收数据628,并且可以包括用于临时存储数据628的存储器。数据628可以沿电子、红外线、光学或其他信息传递路径发送到流体喷射系统600。数据628表示例如要打印的文档和/或文件。因此,数据628形成流体喷射系统600的打印作业并且包括至少一个打印作业命令和/或命令参数。

[0059]

在一个示例中,电子控制器620提供对打印头组件602的控制,包括用于从喷嘴508喷射墨滴的定时控制。因此,电子控制器620限定喷射的墨滴的图案,所述喷射的墨滴在打印介质624上形成字符、符号和/或其他图形或图像。定时控制以及因此喷射的墨滴的图案由打印作业命令和/或命令参数确定。在一个示例中,形成电子控制器620的一部分的逻辑和驱动电路定位于打印头组件602上。在另一个示例中,形成电子控制器620的一部分的逻辑和驱动电路定位于打印头组件602之外。

[0060]

尽管本文已经图示和描述了特定示例,但是在不脱离本公开的范围的情况下,各种各样的替代和/或等效实施方式可以代替所示出和描述的特定示例。本技术旨在覆盖本文所讨论的特定示例的任何修改或变化。因此,本公开旨在仅由权利要求及其等效物限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1