感光性导体膏体、层叠电子部件及其制造方法与流程

1.本技术基于2020年4月16日申请的日本专利申请2020

‑

73424号主张优先权,其全部内容被引用于此。

2.本公开涉及感光性导体膏体、层叠电子部件及其制造方法。

背景技术:

3.目前,已知有通过使用了感光性导体膏体的光刻法形成层叠电子部件的导体图案的技术。日本特开2001

‑

264965号公报中公开有作为无机添加成分添加了玻璃粉的感光性导体膏体。

技术实现要素:

4.发明人等对添加于感光性导体膏体的无机添加成分重复进行了研究,获得如下见解:通过添加无机添加成分,能够调整层叠电子部件的素体和导体图案之间的收缩率的差及收缩举动的不同。但是,作为无机添加成分添加了玻璃粉的感光性导体膏体中,玻璃在制造工序中的热处理之间软化,其结果,可在素体和导体图案之间产生空隙(void)。

5.根据本公开,提供一种抑制了空隙的产生的感光性导体膏体、层叠电子部件及其制造方法。

6.本公开的一个方面所涉及的感光性导体膏体包含感光性有机成分、导体粉及石英粉。

7.由于石英的熔点比制造层叠电子部件时的热处理温度高,因此,在所述感光性导体膏体中难以产生石英粉的熔融,能够在用于层叠电子部件的制造时抑制空隙的产生。

8.在另一个方面所涉及的感光性导体膏体中,石英粉的中值粒径为0.4~5.0μm。

9.在另一个方面所涉及的感光性导体膏体中,导体粉的中值粒径为石英粉的中值粒径以上。

10.在另一个方面所涉及的感光性导体膏体中,导体粉为银粉。

11.本公开的一个方面所涉及的层叠电子部件具有层叠结构,该层叠结构包含具有矩形截面的缺损部的多个素体层和向多个素体层的各自的缺损部填补的多个导体层,导体层由内包石英粉的导体构成。

12.在上述层叠电子部件中,导体层内包石英粉,抑制制造时的热处理之间的熔融,抑制在素体层和导体层之间产生空隙的情况。

13.在另一个方面所涉及的层叠电子部件中,多个导体层构成线圈。

14.在另一个方面所涉及的层叠电子部件中,素体层由包含玻璃成分的材料构成。

15.本公开的一个方面所涉及的层叠电子部件的制造方法包含:形成层叠体的工序,该形成层叠体包含层叠并且分别具有矩形截面的缺损部的多个素体图案和向多个素体图案各自的缺损部填补的多个导体图案;以及对层叠体进行热处理,使素体图案成为素体层且使导体图案成为导体层的工序,通过使用了包含感光性有机成分、导体粉及石英粉的感

光性导体膏体的光刻形成导体图案。

16.在上述层叠电子部件的制造方法中,由于添加于感光性导体膏体的石英粉在热处理工序中难以熔融,因此,抑制素体层和导体层之间的空隙的产生。

附图说明

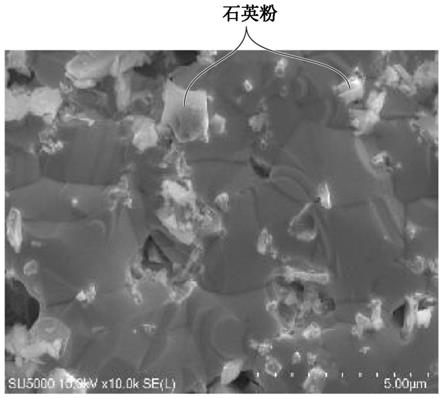

17.图1是第一实施方式所涉及的感光性导体膏体的热处理后的电子显微镜照片。

18.图2是通过第一实施方式所涉及的层叠线圈部件的制造方法制造的层叠线圈部件的立体图。

19.图3是图1所示的层叠线圈部件的分解立体图。

20.图4是表示第一实施方式所涉及的层叠线圈部件的制造方法的流程图。

21.图5a~5g是概念性地表示第一实施方式所涉及的层叠线圈部件的制造方法的截面图。

22.图6a及6b是概念性地表示第一实施方式所涉及的层叠线圈部件的制造方法的截面图。

23.图7是添加了玻璃粉的感光性导体膏体的热处理后的电子显微镜照片。

24.图8是表示第二实施方式所涉及的层叠线圈部件的制造方法的流程图。

25.图9a~9e是概念性地表示第二实施方式所涉及的层叠线圈部件的制造方法的截面图。

具体实施方式

26.以下,参照附图对本公开的实施方式进行详细地说明。在说明中,对相同要素或具有相同功能的要素使用相同符号,并省略重复的说明。

27.[第一实施方式]

[0028]

(感光性导体膏体)

[0029]

第一实施方式所涉及的感光性导体膏体在感光性有机成分中包含导体粉作为导电性成分,并且包含石英粉作为无机添加成分。更详细而言,感光性导体膏体在感光性有机成分中分散有导体粉及石英粉。感光性导体膏体作为无机添加成分不包含玻璃。

[0030]

感光性导体膏体的感光性有机成分包含有机粘合剂及有机溶剂,可还包含例如光聚合性单体或光聚合引发剂等。感光性有机成分也可以是负型及正型的任一种。

[0031]

导体粉例如为银粉等的金属粉或合金粉。在本实施方式中,导体粉为银粉。在本实施方式中,银粉具有0.5~5.0μm(作为一例,为2.5μm)的中值粒径(d50粒径)。

[0032]

石英粉是由石英构成的微粉(硅砂),例如通过粉碎获得。在本实施方式中,石英粉具有0.4~5.0μm的中值粒径(d50粒径)。在本实施方式中,银粉的中值粒径成为石英粉的中值粒径以上。石英粉也可以具有1.0~7.0μm的d95粒径。石英粉也可以具有2.0~10μm的最大粒径。作为一例,石英粉的中值粒径为1.0μm,d95粒径为2.0μm,最大粒径为5.0μm。在石英粉过细的情况下,在使感光性导体膏体干燥并膜化时,光到达而产生光聚合反应的厚度(反应膜厚)劣化,因此,对石英粉要求某种程度大的粒径。石英粉相对于银粉以0.5~2.5wt%程度的比例添加。通过调整石英粉的添加比例,从而调整对感光性导体膏体进行热处理时的收缩率。例如,通过提高石英粉的添加比例,从而降低收缩率(最终收缩率),能够降低后

述的层叠电子部件中的导体层和素体层之间的收缩率的差。另外,通过调整石英粉的添加比例,能够使素体层的从收缩开始到收缩结束为止的举动(收缩举动)接近导体层的收缩举动。通过使导体层和素体层之间的收缩率及收缩举动接近,能够抑制由收缩率及收缩举动的差引起而产生于导体层和素体层的界面附近的空隙。

[0033]

如图1所示,石英粉为具有多个角部(或尖锐部)的形状,例如具有多边形状截面。就石英粉而言,如果是比石英的熔点(1600~1700℃程度,)更低的温度进行的热处理,则不熔融而保持其形状。在石英粉未熔融的情况下,石英粉彼此不会凝聚,即使在热处理后也保持分散状态。

[0034]

此外,由于石英粉具有充分的光透射性(uv透射性),因此,在相对于感光性导体膏体的光刻法中的曝光时,石英粉不妨碍该曝光。

[0035]

(层叠线圈部件)

[0036]

参照图2及图3说明第一实施方式所涉及的层叠线圈部件。图2是通过第一实施方式所涉及的层叠线圈部件的制造方法制造的层叠线圈部件的立体图。图3是图2所示的层叠线圈部件的分解立体图。

[0037]

如图2及图3所示,第一实施方式所涉及的层叠线圈部件1具备:素体2;安装用导体3、4;多个线圈导体5c、5d、5e、5f;以及连接导体6、7。

[0038]

素体2呈现长方体形状。长方体形状中包括将角部及棱线部进行倒角的长方体的形状、以及将角部及棱线部倒圆的长方体的形状。素体2具有端面2a、2b和侧面2c、2d、2e、2f。端面2a、2b相互相对。侧面2c、2d相互相对。侧面2e、2f相互相对。以下,将端面2a、2b的相对方向设为方向d1,将侧面2c、2d的相对方向设为方向d2,以及将侧面2e、2f的相对方向设为方向d3。方向d1、方向d2、及方向d3相互大致正交。

[0039]

端面2a、2b以连结侧面2c、2d的方式沿着方向d2延伸。端面2a、2b也以连结侧面2e、2f的方式沿着方向d3延伸。侧面2c、2d以连结端面2a、2b的方式沿着方向d1延伸。侧面2c、2d也以连结侧面2e、2f的方式沿着方向d3延伸。侧面2e、2f以连结侧面2c、2d的方式沿着方向d2延伸。侧面2e、2f也以连结端面2a、2b的方式沿着方向d1延伸。

[0040]

侧面2c为安装面,例如是在将层叠线圈部件1安装于未图示的其它电子设备(例如,电路基材或电子部件)时,与其它电子设备相对的面。端面2a、2b是从安装面(即侧面2c)连续的面。

[0041]

素体2的方向d1上的长度比素体2的方向d2上的长度及素体2的方向d3上的长度长。素体2的方向d2上的长度和素体2的方向d3上的长度相互同等。即,本实施方式中,端面2a、2b呈现正方形状,侧面2c、2d、2e、2f呈现长方形状。素体2的方向d1上的长度也可以与素体2的方向d2上的长度、及素体2的方向d3上的长度同等,也可以比这些长度短。素体2的方向d2上的长度及素体2的方向d3上的长度也可以相互不同。

[0042]

此外,本实施方式中“同等”除了相等之外,也可以将包含预先设定的范围内的微差或制造误差等的值设为同等。例如,如果多个值包含于该多个值的平均值的

±

5%的范围内,则将该多个值规定为同等。

[0043]

在素体2设置有凹部21、22、23、24。凹部21、22一体地设置,与安装用导体3对应。凹部23、24一体地设置,与安装用导体4对应。

[0044]

凹部21设置于侧面2c的端面2a侧,并朝向侧面2d凹陷。凹部22设置于端面2a的侧

面2c侧,并朝向端面2b凹陷。凹部23设置于侧面2c的端面2b侧,并朝向侧面2d凹陷。凹部24设置于端面2b的侧面2c侧,并朝向端面2a凹陷。凹部21、22、23、24例如呈现相同形状。凹部21、22、23、24与侧面2d、2e、2f分开地设置。凹部21和凹部23在方向d1上相互分开地设置。

[0045]

素体2通过在方向d3上层叠多个素体层12a~12f而构成。具体的层叠结构将在之后描述。在实际的素体2中,多个素体层12a~12f一体化成不能辨识其层间的边界的程度。素体层12a~12f例如由磁性材料(ni

‑

cu

‑

zn系铁氧体材料,ni

‑

cu

‑

zn

‑

mn系铁氧体材料,或ni

‑

cu系铁氧体材料等)构成。构成素体层12a~12f的磁性材料中也可以包含fe合金等。素体层12a~12f也可以包含玻璃材料,也可以由非磁性材料(玻璃陶瓷材料、电介质材料等)构成。

[0046]

安装用导体3配置于凹部21、22内。安装用导体4配置于凹部23、24内。安装用导体3、4在方向d1上相互分开。安装用导体3、4例如呈现相同形状。安装用导体3、4例如呈现截面l字状。也可以说安装用导体3、4例如从方向d3观察呈现l字状。通过对安装用导体3、4实施电镀或非电镀,也可以在其外表面形成镀层。镀层例如包含cu、ni、sn、au等。

[0047]

安装用导体3通过将从方向d3观察呈现l字状的多个安装用导体层13在方向d3上层叠而构成。实际的安装用导体3中,多个安装用导体层13被一体化成不能辨识其层间的边界的程度。安装用导体3具有一体地形成的导体部分31、32。导体部分31、32呈现大致矩形板状。导体部分31、32例如呈现相同形状。导体部分31配置于凹部21内。导体部分32配置于凹部22内。

[0048]

安装用导体4通过将从方向d3观察呈现l字状的多个安装用导体层14在方向d3上层叠而构成。实际的安装用导体4中,多个安装用导体层14被一体化成不能辨识其层间的边界的程度。安装用导体4具有一体地形成的导体部分41、42。导体部分41、42呈现大致矩形板状。导体部分41、42例如呈现相同形状。导体部分41配置于凹部23内。导体部分42配置于凹部24内。

[0049]

多个线圈导体5c、5d、5e、5f相互连接,在素体2内构成线圈10。线圈导体5c、5d、5e、5f以从方向d3观察,至少一部分相互重合的方式配置。线圈导体5c、5d、5e、5f与端面2a、2b及侧面2c、2d、2e、2f分开地配置。

[0050]

线圈导体5c构成线圈10的一个端部。线圈导体5c的一个端部和连接导体6在方向d1上相邻且相互连接。线圈导体5c的另一个端部和线圈导体5d的一个端部在方向d3上相邻且相互连接。线圈导体5d的另一个端部和线圈导体5e的一个端部在方向d3上相邻且相互连接。线圈导体5e的另一个端部和线圈导体5f的一个端部在方向d3上相邻且相互连接。线圈导体5f的另一个端部和连接导体7在方向d1上相邻且相互连接。

[0051]

线圈导体5c、5d、5e、5f通过将多个线圈导体层15c、15d、15e、15f在方向d3上层叠而构成。即,多个线圈导体层15c、15d、15e、15f以分别从方向d3观察,全部相互重合的方式配置。线圈导体5c、5d、5e、5f也可以由一个线圈导体层15c、15d、15e、15f构成。此外,图3中仅图示有一个线圈导体层15c、15d、15e、15f。实际的线圈导体5c、5d、5e、5f中,多个线圈导体层15c、15d、15e、15f被一体化成不能辨识其层间的边界的程度。

[0052]

连接导体6沿着方向d1延伸,且与线圈10的线圈导体5c和导体部分42连接。连接导体7沿着方向d1延伸,且与线圈导体5f和导体部分32连接。连接导体6、7通过将多个连接导体层16、17在方向d3上层叠而构成。此外,图3中仅图示有一个连接导体层16、17。实际的连

接导体6、7中,多个连接导体层16、17被一体化成不能辨识其层间的边界的程度。

[0053]

上述的安装用导体层13、14、线圈导体层15c、15d、15e、15f、及连接导体层16、17由包含银及石英粉的导体构成。这些各层也可以由相同的材料构成,也可以由不同的材料构成。这些各层具有矩形截面。此外,本实施方式的“矩形截面”是指在沿着规定方向延伸的部分中,与其方向正交的面切断时的截面的形状为矩形。另外,本实施方式的“矩形”不限于被四条直线包围且四个角全部为直角的形状(长方形或正方形),如果呈现大致矩形的轮廓,则也可以是相对的直线不平行,也可以是直线的一部分或全部弯曲,也可以是角不是直角,也可以是将角倒圆。

[0054]

层叠线圈部件1具备多个层la、lb、lc、ld、le、lf。层叠线圈部件1通过例如从侧面2f侧依次层叠有两个层la、一个层lb、三个层lc、三个层ld、三个层le、三个层lf、一个层lb、及两个层la而构成。此外,图3中,三个层lc、三个层ld、三个层le、及三个层lf分别图示出一个,省略其它的两个图示。

[0055]

层la由素体层12a构成。

[0056]

层lb通过将素体层12b和安装用导体层13、14相互组合而构成。在素体层12b中设置有具有与安装用导体层13、14的形状对应的形状,且填补安装用导体层13、14的缺损部rb。素体层12b和安装用导体层13、14的整体具有相互补充的关系。

[0057]

层lc通过将素体层12c和安装用导体层13、14及线圈导体层15c相互组合而构成。在素体层12c中设置有具有与安装用导体层13、14及线圈导体层15c的形状对应的形状,且填补安装用导体层13、14、线圈导体层15c及连接导体层16的缺损部rc。素体层12c和安装用导体层13、14、线圈导体层15c及连接导体层16的整体具有相互补充的关系。

[0058]

层ld通过将素体层12d和安装用导体层13、14及线圈导体层15d相互组合而构成。在素体层12d中设置有具有与安装用导体层13、14及线圈导体层15d的形状对应的形状,且填补安装用导体层13、14及线圈导体层15d的缺损部rd。素体层12d和安装用导体层13、14及线圈导体层15d的整体具有相互补充的关系。

[0059]

层le通过将素体层12e和安装用导体层13、14及线圈导体层15e相互组合而构成。在素体层12e中设置有具有与安装用导体层13、14及线圈导体层15e的形状对应的形状,且填补安装用导体层13、14及线圈导体层15e的缺损部re。素体层12e和安装用导体层13、14及线圈导体层15e的整体具有相互补充的关系。

[0060]

层lf通过将素体层12f和安装用导体层13、14、线圈导体层15f及连接导体层17相互组合而构成。在素体层12f中设置有具有与安装用导体层13、14、线圈导体层15f及连接导体层17的形状对应的形状,且填补安装用导体层13、14、线圈导体层15f及连接导体层17的缺损部rf。素体层12f和安装用导体层13、14、线圈导体层15f及连接导体层17的整体具有相互补充的关系。

[0061]

缺损部rb、rc、rd、re、rf被一体化而构成上述的凹部21、22、23、24。缺损部rb、rc、rd、re、rf的宽度(以下,缺损部的宽度)以基本上比安装用导体层13、14、线圈导体层15c、15d、15e、15f、及连接导体层16、17的宽度(以下,导体部的宽度)宽的方式设定。为了提高素体层12b、12c、12d、12e、12f、安装用导体层13、14、线圈导体层15c、15d、15e、15f、及连接导体层16、17的粘接性,缺损部的宽度也可以以特意比导体部的宽度窄的方式设定。缺损部的宽度减去导体部的宽度的值例如也可以为

‑

3μm以上且10μm以下,也可以为0μm以上且10μm

以下。

[0062]

(层叠线圈部件的制造方法)

[0063]

参照图4、图5a~5g、图6a及6b说明实施方式的层叠线圈部件1的制造方法。图4是表示第一实施方式的层叠线圈部件的制造方法的流程图。图5a~5g、图6a及6b是概念性地表示第一实施方式的层叠线圈部件的制造方法的截面图。图5a~5g、图6a及6b的截面图是概念性地表示的,未必一定与实际的层叠线圈部件1的截面图一致。

[0064]

首先,如图5a所示,在基材20上形成素体形成层21(工序s1)。基材20例如为pet薄膜。素体形成层21例如通过将包含添加了上述的素体层12a~12f的构成材料的感光性有机成分的素体膏体涂布于基材20上而形成。素体膏体中包含的感光性有机成分也可以是负型及正型中的任一种,能够使用公知的成分。

[0065]

接着,如图5b所示,通过使用了例如cr掩模的光刻法对素体形成层21进行曝光及显影,在基材20上形成除去了与后述的导体图案32的形状对应的形状的素体图案22(工序s2)。素体图案22是在热处理后成为素体层12b~12f的层。即,工序s2中,形成设置有成为缺损部rc、rd、re、rf的缺损部23的素体图案22。此外,本实施方式的“光刻法”只要是通过对包含感光性有机成分的加工对象的层进行曝光及显影,从而加工成期望的图案的方法即可,对掩模的种类等没有限定。

[0066]

另一方面,如图5c所示,在基材30上形成导体形成层31(工序s3)。基材30例如为pet薄膜。导体形成层31通过在基材30上涂布上述的感光性导体膏体而形成。接着,如图5d所示,例如通过使用了cr掩模的光刻法对导体形成层31进行曝光及显影,在基材30上形成导体图案32(工序s4)。导体图案32是在热处理后成为安装用导体层13、14、线圈导体层15c、15d、15e、15f及连接导体层16、17的层。

[0067]

接着,如图5e所示,将上述工序s1中形成的素体形成层21从基材20转印至支撑体40上(工序s5)。通过将工序s5反复进行多次,也可以在支撑体40上层叠多个素体形成层21。本实施方式中,通过将工序s5反复进行两次,在支撑体40上层叠两层素体形成层21。这些素体形成层21是在热处理后成为层la的层。

[0068]

接着,通过将导体图案32及素体图案22反复转印至支撑体40上,在方向d3上层叠导体图案32及素体图案22。具体而言,首先,如图5f所示,将上述工序s4中形成的导体图案32从基材30转印至在上述工序s5中转印的素体形成层21上(工序s6)。接着,如图5g所示,将上述工序s2中形成的素体图案22从基材20转印至在上述工序s5中转印的素体形成层21上(工序s7)。向素体图案22的缺损部23填补上述工序s6中转印至素体形成层21上的导体图案32,素体图案22及导体图案32成为同一层。

[0069]

另外,如图6a所示,反复实施上述工序s6及上述工序s7,将素体图案22及导体图案32在相互组合的状态下层叠(工序s8)。由此,层叠在热处理后成为层lb、lc、ld、le、lf的层。此外,在上述工序s8中,未必一定需要一对一反复进行上述工序s6及上述工序s7,例如,也可以比上述工序s7多地反复进行上述工序s6。由此,例如,也可以将仅与安装用导体层13、14对应的导体图案32相对于素体图案22额外地转印。接着,如图6b所示,将上述工序s1中形成的素体形成层21从基材20转印至上述工序s8中层叠的层上(工序s9)。通过将工序s9反复进行多次,可以在该层上层叠多个素体形成层21。本实施方式中,通过反复进行两次,将素体形成层21从基材20在该层上层叠两层。这些素体形成层21是在热处理后成为层la的层。

[0070]

通过以上,将热处理后构成层叠线圈部件1的层叠体50形成于支撑体40上。此外,例如,也可以将设置有切割标记或表示芯片(层叠线圈部件1)的方向性的标记的层或着色层根据需要进一步层叠,成为层叠体50。

[0071]

接着,将获得的层叠体50切割成规定的大小(工序s10)。

[0072]

然后,相对于切割的层叠体50进行脱粘合剂处理之后,进行热处理(工序s11)。热处理温度例如为850~900℃程度。由此,获得层叠线圈部件1。也可以根据需要对安装用导体3、4实施电镀或非电镀。

[0073]

通过热处理工序s11,感光性导体膏体成为由内包石英粉的银构成的导体图案。未必一定需要石英粉全部存在于导体图案的内部,石英粉的一部分也可以从导体图案的表面局部地露出。如图1的电子显微镜照片所示,由于热处理工序s11中的热处理温度比石英的熔点低,因此,感光性导体膏体中的石英粉未熔融,可保持其形状。另外,不但石英粉彼此未熔合,而且即使经由热处理工序s11之后,也可保持感光性导体膏体中的石英粉的分散状态。

[0074]

另一方面,在感光性导体膏体包含玻璃粉作为无机添加成分的情况下,由于玻璃的软化点(例如800℃程度)比石英的熔点低,存在热处理工序s11中的热处理温度比玻璃的软化点高的风险,在该情况下,如图7所示,感光性导体膏体中的玻璃粉软化。在图7中,玻璃周边的黑色区域是玻璃成分固溶于导电性成分中的相(异相)。玻璃粉在热处理工序后未保持其形状,而成为球状。另外,作为玻璃粉软化的结果,也产生玻璃粉彼此的凝聚,未保持感光性导体膏体中的玻璃粉的分散状态。此外,在感光性导体膏体包含石英粉作为无机添加成分的情况下,与导电性成分的界面的异相的厚度窄,为10μm以下,也可以为6μm以下。

[0075]

接着,根据需要,对安装用导体3、4实施电镀或非电镀,在安装用导体3、4的外表面上形成镀层。由此,获得层叠线圈部件1。

[0076]

如以上所说明的那样,在本实施方式所涉及的感光性导体膏体中,在热处理工序s11中未产生或极其难以产生石英粉的熔融,在热处理工序s11中以使导体层及素体层收缩时的两者的收缩率及收缩举动接近的方式充分发挥作用,因此,能够在用于层叠线圈部件1的制造时抑制空隙的产生。

[0077]

本实施方式中,均通过光刻法形成素体图案及导体图案,因此,与例如由印刷法进行的情况相比,能够高精度地形成素体图案及导体图案。

[0078]

[第二实施方式]

[0079]

参照图8及图9a~9e说明第二实施方式所涉及的层叠线圈部件1的制造方法。图8是表示第二实施方式的层叠线圈部件的制造方法的流程图。图9a~9e是概念性地表示第二实施方式的层叠线圈部件的制造方法的截面图。图9a~9e的截面图是概念性地表示的,未必一定与实际的层叠线圈部件1的截面图一致。此外,通过第二实施方式所涉及的制造方法制造的层叠线圈部件1和通过第一实施方式所涉及的制造方法制造的层叠线圈部件1为相互相同的结构。

[0080]

第二实施方式所涉及的制造方法中,首先,如图9a所示,在支撑体40上形成素体形成层21(工序s21)。素体形成层21通过例如将素体膏体涂布于支撑体40的表面而形成。本实施方式中,通过将工序s21进行两次,将素体形成层21层叠两层。这些素体形成层21是在热处理后成为层la的层。

[0081]

接着,如图9b所示,在素体形成层21上形成导体形成层31(工序s22)。导体形成层31通过将上述的感光性导体膏体涂布于素体形成层21上而形成。而且,如图9c所示,例如通过使用了cr掩模的光刻法对导体形成层31进行曝光及显影,在素体形成层21上形成导体图案32(工序s23)。导体图案32是在热处理后成为安装用导体层13、14、线圈导体层15c、15d、15e、15f及连接导体层16、17的层。

[0082]

接着,如图9d所示,以覆盖设置于素体形成层21上的导体图案32的方式,在素体形成层21上形成新的素体形成层21(工序s24)。重新形成的素体形成层21以填埋导体图案32的周围的方式形成。

[0083]

然后,如图9e所示,例如通过使用了cr掩模的光刻法,将重新形成的素体形成层21图案化(工序s25)。向素体图案22的缺损部23填补上述工序s23中形成的导体图案32,素体图案22及导体图案32成为同一层。

[0084]

接着,反复实施上述的工序s22、s23和工序s24、s25,如图6a所示的结构那样,素体图案22及导体图案32在相互组合的状态下层叠。(工序s26)此外,在上述工序s26中,工序s22、s23和工序s24、s25未必一定需要一对一反复进行,例如,也可以比上述工序s24、s25多地反复进行上述工序s22、s23。由此,例如,也可以将仅与安装用导体层13、14对应的导体图案32相对于素体图案22额外地转印。接着,由于设为图6b所示的结构,因此,将新的素体形成层21形成于上述工序s26中层叠的层上。(工序s27)通过将工序s27反复进行多次,可以在该层上层叠多层素体形成层21。本实施方式中,通过反复进行两次,将素体形成层21从基材20在该层上层叠两层。这些素体形成层21是在热处理后成为层la的层。

[0085]

通过以上,将热处理后构成层叠线圈部件1的层叠体50形成于支撑体40上。接着,与第一实施方式一样,将获得的层叠体50切割成规定的大小(工序s28),然后,相对于切割的层叠体50进行脱粘合剂处理之后,进行热处理(工序s29)。由此,获得层叠线圈部件1。

[0086]

如以上所说明的那样,第二实施方式中也与第一实施方式一样,使用感光性导体膏体,因此,在热处理工序s29中未产生或极其难以产生石英粉的熔融,在热处理工序s29中以使导体层及素体层收缩时的两者的收缩率及收缩举动接近的方式充分发挥作用,因此,能够在用于层叠线圈部件1的制造时抑制空隙的产生。

[0087]

本公开不限定于上述的实施方式,可进行各种各样的变形。

[0088]

素体图案及导体图案也可以不通过光刻法,而通过例如印刷法形成。素体图案及导体图案未必一定需要形成于不同的基材上,如果素体图案及导体图案为相互分开的状态,则也可以形成于共同的基材上。

[0089]

上述的第一实施方式及第二实施方式中,作为层叠电子部件以层叠线圈部件1为例进行了说明,但本公开不限于此,也能够适用于层叠陶瓷电容器、层叠变阻器、层叠压电致动器、层叠热敏电阻、或层叠复合部件等其它的电子部件的制造方法。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1