核斜坡检测电路的制作方法

[0001]

本公开的实施例涉及一种核斜坡检测电路。

背景技术:

[0002]

本部分旨在提供与理解本文所述的各种技术相关的信息。正如本部分的标题所暗示的,这是对相关技术的讨论,而绝不暗示它是现有技术。通常,相关技术可以被认为是现有技术或者可以不被认为是现有技术。因此,应当理解,本部分中的任何陈述应按照这种方式解读,而不是对现有技术的任何承认。

[0003]

一些常规的电路设计试图以低功率工作。为了实现低功率方案,输入/输出(io)电路可以适合于支持多个电源域(power domain)。然而,使用多个电源域通常会引起对这些多个域进行电源排序,其中电源排序是指一种策略,通过该策略确定多个电源的斜升或斜降的顺序或序列。此外,不正确的电源排序可能会引起io电路不必要的泄漏和/或引起输出处的不确定状态。因此,存在减少泄漏以便改善电路性能和效率的需求。

技术实现要素:

[0004]

本公开的第一方面,提供了一种设备,可以包括:输出焊盘,提供来自输入输出io电源的io电压;核斜坡检测电路,检测来自核电源的核电压的第一斜坡并提供核斜坡感测信号;以及输出逻辑电路,在接收到所述核斜坡感测信号之后将所述输出焊盘耦合到地,以便减少所述io电源的泄漏。

[0005]

本公开的第二方面,提供了一种系统,包括:第一芯片,具有感测电路和带有第一输出焊盘的第一输入/输出io单元,所述第一输出焊盘提供来自io电源的输入输出电压和来自核电源的核电压中的至少一个;以及第二芯片,具有带有第二输出焊盘的第二io单元,所述第二输出焊盘从所述第一输出焊盘接收所述io电压和所述核电压中的至少一个,其中,所述感测电路检测所述核电压的第一斜坡并将所述第一输出焊盘耦合到地,直到核电源开始第一次斜升,以减少所述io电压和所述核电压中的至少一个到所述第二输出焊盘的泄漏。

[0006]

本公开的第三方面,提供了一种方法,包括:经由输出焊盘提供输入输出io电压;检测核电压的第一斜坡;在检测所述核电压的所述第一斜坡期间生成斜坡感测信号;以及在接收到所述斜坡感测信号之后,将所述输出焊盘耦合到地,以便减少io电压和所述核电压中的至少一个的泄漏。

附图说明

[0007]

本文参考附图描述了各种技术的实施方式。然而,应当理解,附图仅示出了本文所描述的各种实施方式,并不意味着限制本文所描述的各种技术的实施例。

[0008]

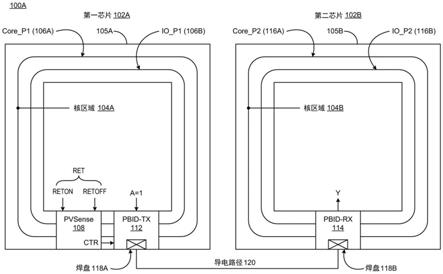

图1a示出了根据本文所述的各种实施方式的多个芯片、核电路(core circuitrv)和输入输出(io)电路的图。

[0009]

图1b示出了根据本文所述的各种实施方式的电源排序的波形图。

[0010]

图2a至图2d示出了根据本文所述的各种实施方式的与核斜坡检测(core ramp detection)相关的电路的图。

[0011]

图3示出了根据本文所述的各种实施方式的核检测电路的图。

[0012]

图4a至图4b示出了根据本文所述的各种实施方式的核斜坡检测电路的图。

[0013]

图5a至图5b示出了根据本文所述的各种实施方式的保持逻辑电路的图。

具体实施方式

[0014]

本文所述的各种实施方式涉及核斜坡检测电路,其包括用于参考针对各种低功率应用的输入/输出(io)电路来改善泄漏效率的方案和技术。本文所述的各种方案和技术可以提供一种创新的方法,以有效地减少或最小化由于低功率专用片上系统(soc)中不同电源域的独立电源排序(即,多个电源的斜升或斜降的顺序)而引起的泄漏电流。例如,本文所述的各种方案和技术可以提供给一种集成电路(ic),以避免在多个电源域的加电或掉电期间的错误或不确定的逻辑状态,并且还通过在电源排序操作期间在输出处定义稳定状态来避免来自电源的不必要的泄漏电流。

[0015]

本文所述的各种实施方式通过使用pvsense单元作为电源管理解决方案的一部分来支持电源排序。pvsense单元基于核电路的各种参数来检测核电源和io电源两者的可用性和任一项的三态,或将pbid-tx的输出保持为某个预定义值。例如,当在第一电压域中操作的第一io单元驱动在第二电压域中操作的第二io单元时,则第一io单元的输出在第一电压域的电源关闭期间保持预定义的值(0或1)。该技术可以确保第二io单元具有稳定的电源,该稳定的电源不会由于其输入的不确定状态而泄漏,并且第二io单元的输出可以具有确定状态,而不是不确定状态。当在第一输入输出(io)单元处有一些先前的数据要保持时,该保持处理可能会很好地工作,但是,如果没有有效的先前数据可用(例如,在核电压的第一次斜升期间),则保持可能无法保持有效。当核电路第一次斜升时,然后第一io单元的输出可能不确定,并且在这种情况下,保持操作可能引起第一io单元的输出处的不确定状态。因此,本文所述的各种方案和技术试图通过检测第一核斜坡操作来解决与第一斜坡相关联的问题。当检测到核的第一次斜坡时,本文所述的各种方案和技术启用设置在第一io单元中的弱下拉逻辑电路(直到核电源开始第一次斜升)。因此,通过启用弱下拉逻辑,输出处的状态可以接地,并且因此使逻辑为零,而不是将输出焊盘保持在浮动(x)的不确定状态,并且因此可以避免通过第二io单元的电源泄漏。

[0016]

本文将参考图1a至图5b详细描述核斜坡检测电路的各种实施方式。

[0017]

图1a示出了根据本文所述的各种实施方式的多个芯片和核电路100a的图。在一些情况下,核电路100a可以被实现为具有各种电路组件的系统或设备,该各种电路组件布置并耦合在一起作为提供封装或板型结构的系统的部件的集合或组合。此外,在一些情况下,检测核斜坡的方法可以涉及使用本文所述的各种电路组件来实现改善的性能方案和技术。

[0018]

如图1a所示,核电路100a可以包括各种组件,该各种组件包括一个或多个半导体芯片(或管芯),例如经由导电路径120耦合在一起的第一芯片(或管芯)102a和第二芯片(或管芯)102b。在各种情况下,导电路径120可以由导线或类似物形成。在下文中将更详细地描述与核电路100a及其相关联的各种组件相关的进一步描述。

[0019]

可以使用各种类型的存储器(例如,随机存取存储器(ram)(包括静态ram(sram))和/或任何其他类型的易失性存储器)和其他逻辑电路将核电路100a实现为一个或多个集成电路(ic)。在一些情况下,核电路100a的管芯102a、管芯102b中的每一个可以被实现为具有存储器架构和相关电路的ic。在其他情况下,核电路100a的管芯102a、管芯102b中的每一个可以与各种类型的计算电路和相关组件集成在单个芯片上。此外,核电路100a的管芯102a、管芯102b中的每一个可以被实现在用于各种电子、移动和物联网(iot)应用(包括低功率传感器节点)的各种嵌入式系统中。

[0020]

如图1a所示,第一芯片102a可以具有感测电路(pvsense 108)和带有第一输出焊盘118a的第一输入/输出(io)单元(pbid-tx 112),第一输出焊盘118a可以适合于提供输入输出(io)信号。感测电路(pvsense 108)可以被配置为从第一核区域104a接收保持信号(例如,ret:reton/retoff),并基于保持信号(例如,ret:reton/retoff)向第一io单元(pbid-tx 112)提供核斜坡感测信号(ctr)。在一些情况下,第一io单元(pbid-tx 112)可以从第一核区域104a接收核数据输入信号(a),并且核数据输入信号(a)可以具有逻辑值1(例如,a=1),其有助于第一io单元(pbid-tx 112)的激活。在一些实施方式中,保持信号(ret)是指到感测电路(pvsense 108)的输入信号,核斜坡感测信号(ctr)是指感测电路(pvsense 108)的输出,并且ctr信号可以指sns信号和rto信号的组合。

[0021]

同样如图1a所示,第二芯片102b可以具有带有第二输出焊盘118b的第二io单元(pbid_rx 114),该第二输出焊盘118b从第一输出焊盘118a接收io信号。在一些情况下,第二io单元(pbid-rx 114)可以向第二核区域104b提供核数据输出信号(y)。

[0022]

在一些实施方式中,感测电路(pvsense 108)可以被配置为检测核电压(core_p1)的第一斜坡,然后将第一输出焊盘118a耦合到地(gnd或vss),直到核电源(core_p1)开始第一次斜升,从而减少核电压(core_p1/core_p2)和/或io电压(io_p1/io_p2)到第二输出焊盘118b的泄漏。在一些情况下,第一io单元(pbid-tx 112)可以适合于经由导电路径120向第二芯片102b发送(tx)io信号,并且第二io单元(pbid_rx 114)可以适合于经由导电路径120从第一io单元(pbid-tx 112)接收(rx)io信号。

[0023]

参考图1a,可以使用适合于执行各种操作的各种功能组件来单独实现第一芯片102a和第二芯片102b。例如,如图所示,第一芯片102a可以是在第一电源总线106a(核电源)上提供核电压(core_p1)的设备,并且第一芯片102a可以在第二电源总线106b(io电源)上提供io电压(io_p1)。因此,第一芯片102a可以在多个电压域下操作,该多个电压域包括例如第一总线106a(核电源)上的核电压(core_p1)和第二总线106b(io电源)上的(io)电压(io_p1)。第一芯片102a可以包括感测电路(pvsense 108),该感测电路检测核电压(core_p1)的第一斜坡并且向第一io单元(pbid-tx 112)的输出逻辑提供核斜坡感测信号(ctr)。在一些情况下,第一芯片102a可以包括第一io单元(pbid-tx 112),该第一io单元(pbid-tx 112)在接收到核斜坡感测信号(ctr)之后将第一输出焊盘118a耦合到地(gnd或vss)以减少核电压(core_p1)和/或io电压(io_p1)的泄漏。此外,第一io单元(pbid-tx 112)可以经由导电路径120向第二芯片102b发送(tx)io电压(io_p1)。

[0024]

在一些情况下,第一总线106a上的核电压(core_p1)可以指核电压域(vdd),并且第二总线106b上的io电压(io_p1)可以指io电压域(dvdd)。此外,核电压域(vdd)可以与对应的核基准(gnd或vss)相关,并且io电压域(dvdd)可以与对应的io基准(dvss)相关。此外,

在一些情况下,核电源经由第一总线106a提供核电压(core_p1),并且io电源经由第二总线106b提供io电压(io_p1)。

[0025]

第二芯片102b也可以是具有第二输出焊盘118b作为在第一总线116a(核电源)上提供另一个核电压(core_p2)的结构的设备,并且第二芯片102b可以在第二总线116b(io电源)上提供另一个io电压(io_p2)。因此,第二芯片102b也可以在多个电压域下操作,该多个电压域包括例如第一总线116a(核电源)上的核电压(core_p2)和第二总线116b(io电源)上的io电压(io_p2)。第二芯片102b可以包括第二io单元(pbid_rx 114)中的输出逻辑,并且因此,第二芯片102b可以包括第二io单元(pbid_rx 114),该第二io单元(pbid_rx 114)可以适合于经由导电路径120从第一芯片102a接收(rx)io信号。

[0026]

在一些实施方式中,第一io单元(pbid-tx 112)和第二io单元(pbid_rx 114)可以被称为双向io单元。此外,第一总线116a可以被称为耦合到核电源的核电压环,并且第二总线116b可以被称为耦合到io电源的io电压环。此外,感测电路(pvsense 108)可以被称为电源管理单元,其可以用于在电源排序期间减小与核电压环和io电压环相关联的不想要的电流。此外,在一些情况下,核电压(core_p1)是指p1域中的核电源,io电压(io_p1)是指p1域中的io电源。核电压(core_p2)是指p2域中的核电源,io电压(io_p2)是指p2域中的io电源。通常,标记(x)可以表示不确定状态。

[0027]

如图1a所示,第一芯片102a可以包括经由第一总线106a耦合到核电压(core_p1)的核区域104a。此外,第一芯片102a可以包括经由第二总线106b耦合到io电压(io_p1)的外围区域105a。外围区域105a可以包括以io电压(io_p1)操作的一个或多个io端口。此外,如图1a所示,第二芯片102b可以包括经由第一总线116a耦合到核电压(core_p2)的核区域104b,并且第二芯片102b可以包括经由第二总线116b耦合到io电压(io_p2)的外围区域105b。外围区域105b可以包括以io电压(io_p2)操作的一个或多个io端口。

[0028]

在一些情况下,输出焊盘结构118a、118b可以被称为共享总线结构(或pad结构),其可以由多个设备(例如第一芯片102a和第二芯片102b)共享。此外,第一总线106a、116a(或核电压总线或环)在核电压域(vdd)中提供对应的核电压(core_p1,core_p2)。第一输出焊盘118a经由第一io单元(pbid-tx 112)耦合到核电压总线106a,并且第二输出焊盘118b经由第二io单元(pbid-rx 114)耦合到核电压总线116a。第二总线106b、116b(或io电压总线或环)在与核电压域(vdd)不同的io电压域(dvdd)中提供对应的io电压(io_p1,io_p2)。第一输出焊盘118a可以经由第一io单元(pbid-tx 112)耦合到io电压总线106b,并且第二输出焊盘118b也可以经由第二io单元(pbid-rx 114)耦合到io电压总线116b。此外,核电源经由第一总线116a提供核电压(core_p2),并且io电源经由第二总线116b提供io电压(io_p2)。

[0029]

有利地,由于在一些低功率应用中核电压(core_p1)和io电压(io_p1)的独立电源排序,核电路100a(或设备/系统)可以抑制核电压(core_p1)和/或io电压(io_p1)的泄漏。此外,在一些情况下,由于在一些类似低功率应用中另一个核电压(core_p1)和另一个io电压(io_p1)的独立电源排序,核电路100a(或设备/系统)可以类似地抑制另一个核电压(core_p2)和/或另一个io电压(io_p1)的泄漏。

[0030]

根据本文所述的各种实施方式,存储器类型结构可以包括具有存储器单元阵列的核阵列电路,其中每个存储器单元可以被称为位单元。此外,每个存储器单元可以被配置为

存储至少一个数据比特值(例如,与逻辑“0”或“1”相关的数据值)。在各种情况下,存储器单元阵列可以包括以各种适用配置布置的任意数量的存储器单元(或位单元),例如具有任意数量个列(n列)的二维(2d)存储器阵列、以及以2d网格图案布置的任意数量个行(n行)的多个存储器单元。在各种情况下,可以使用任何类型的核电路,包括例如标准单元、存储器单元、触发器、锁存器、电平位移器等。

[0031]

图1b示出了根据本文所述的各种实施方式的电源序列定时102c的波形图100b。

[0032]

在图1b中,波形图100b示出了多个信号的电源序列定时102c,该多个信号包括io_p1、core_p1、reton、retoff和pad以及io_p2和core_p2。在时间ti0与ti1之间,信号(io_p1、core_p1、reton、retoff和pad)处于零伏(0v)。在时间ti1处,io_p1信号开始斜坡,然后正好在时间ti2之前,core_p1信号开始斜坡。在时间ti0与ti1之间的信号(io_p1,core_p1)的这种斜坡期间,pad电压保持零电压(0v)状态。在这种情况下,io_p2和core_p2的泄漏为零。此外,在时间ti1至ti2期间,pad保持零电压状态(0v)。在时间ti2处,随着core_p1信号开始斜坡并且retoff信号开始斜坡,pad上升到逻辑1状态(逻辑1),并且在大于ti2的时间处,pad电压可以保持在逻辑1状态(逻辑1)。

[0033]

参考图1a的pvsense单元108,在图1b中示出了在电源排序102c期间pvsense单元108的操作。在时间ti1至ti2期间,pvsense单元108检测core_p1的第一斜坡条件,并使pbid-tx单元112将pad 118a弱下拉到逻辑0状态(逻辑0),直到核电源(core_p1)开始第一次斜升。因此,可以避免通过pbid-rx单元114的泄漏。此外,当核电源在时间ti2至ti4期间斜升时,则可以自动禁用核斜坡检测,并且此外,随后进行正常pvsense单元108操作以用于随后的电源斜坡。

[0034]

在一些实施方式中,本文所述的各种方案和技术解决了核斜坡泄漏问题。独特的pvsense电路108检测在io电压环中发生的初始或第一核斜坡条件,直到核电源(core_p1)开始第一次斜升为止,pvsense电路108向第一io单元112输出sns=0、rto=0(参考保留状态)。如本文所述,以如下这样的方式设计第一io单元112:当在其输入处接收到输入sns/rto=00时,则第一io单元112启用弱下拉逻辑电路,以便将输出焊盘118a耦合到地(gnd/vss=0v),而不是将输出焊盘118a保持在浮动状态或不确定(x)状态。在一些情况下,在第一io单元112可以与现有电路设计一起使用的意义上,第io单元112可以是向后兼容的,因为现有电路设计可能不能生成sns/rto=00条件。

[0035]

图2a至图2d示出了根据本文所述的实施方式的与核斜坡检测相关的电路的图。特别地,图2a示出了感测电路200a的图,图2b示出了核斜坡检测电路200b的图,图2c示出了输出逻辑电路200c的图,以及图2d示出了输出逻辑电路200d的另一部分的图。

[0036]

参考图2a,感测电路200a是指图1a的感测电路(pvsense 108)。在一些实施方式中,感测电路200a可以被实现为具有各种电路组件(或块)的系统或设备,该各种电路组件(或块)布置并耦合在一起,作为提供核斜坡检测的部件的集合或某种组合。此外,核斜坡检测的方法可以涉及使用本文所述的各种电路组件,以便实现改善的性能方案和技术。

[0037]

如图2a所示,感测电路200a(pvsense 108)可以包括各种组件,包括核检测电路210、核斜坡检测电路212、保持逻辑电路214和输出逻辑电路228。在一些情况下,输出逻辑电路228可以指图1a的第一io单元(pbid_tx 112)的弱上拉。

[0038]

感测电路200a(pvsense 108)可以包括提供io信号的输出焊盘结构118a。核斜坡

检测电路212可以检测核电压(core_p1)的斜坡并提供核斜坡感测信号(ctr或其一部分,例如,sns)。输出逻辑电路228可以在接收到核斜坡感测信号(ctr:sns)之后将输出焊盘结构118a耦合到地(gnd或vss)以减少核电压(core_p1)和/或io电压(io_p1)的泄漏。在一些情况下,核斜坡检测电路212可以被称为第一核斜坡检测电路,其操作以避免在第一核电源斜升期间核电压(core_p1)和/或io电压(io_p1)上的泄漏。

[0039]

核检测电路210可以感测核电压(core_p1),并且向核斜坡检测电路212提供核检测信号(core_p1_det)。在一些情况下,核斜坡检测电路212可以从核检测210接收核检测信号(core_p1_det),接收保持信号(ret:reton/retoff),并且基于核检测信号(core_p1_det)和/或保持信号(ret:reton/retoff)向输出逻辑电路228提供核斜坡感测信号(ctr:sns)。

[0040]

保持逻辑电路214可以从核检测电路210接收核检测信号(core_p1_det),接收保持信号(ret:reton/retoff),并向输出逻辑电路228提供输出保持信号(rto)。在一些情况下,输出保持信号(rto)可以是核斜坡感测信号(ctr)的一部分。因此,ctr信号可以包括sns信号和/或rto信号。输出逻辑电路228可以从核斜坡检测电路212接收核斜坡感测信号(ctr:sns),从保持逻辑电路214接收输出保持信号(ctr:rto),并且在接收到核斜坡感测信号(ctr:sns)之后和在接收到输出保持信号(ctr:rto)之后将输出焊盘结构118a耦合到地(gnd或vss),以便减少核电压(core_p1)和/或io电压(io_p1)的泄漏。

[0041]

输出逻辑电路228在接收到处于逻辑0状态(逻辑0)的核斜坡感测信号(ctr:sns)之后并且在接收到处于逻辑0状态(逻辑0)的输出保持信号(ctr:rto)之后,可以将输出焊盘结构118a耦合到地(gnd或vss),从而减少核电压(core_p1)和/或io电压(io_p1)的泄漏。

[0042]

参考图2b,核斜坡检测电路200b是指图2a的核斜坡检测电路212。如图2b所示,核斜坡检测电路212可以包括各种组件,包括核斜坡逻辑电路216、反相器电路220和感测(sns)逻辑电路224。

[0043]

如图2b所示,核斜坡检测电路212可以包括核斜坡逻辑电路216,其从(图2a的)核检测电路210接收核检测信号(core_p1_det),接收保持信号(ret:reton/retoff),并向感测(sns)逻辑电路224提供核斜坡信号(core_ramp)。此外,核斜坡检测电路212可以包括反相器电路220,其从(图2a的)核检测电路210接收核检测信号(core_p1_det)并提供反相核检测信号(core_p1_detb)。此外,核斜坡检测电路212可以包括感测(sns)逻辑电路224,其从核斜坡逻辑电路216接收核斜坡信号(core_ramp),从反相器电路220接收反相核检测信号(core_p1_detb),并且向(图2a的)输出逻辑电路228提供核斜坡感测信号(sns)。

[0044]

参考图2c,输出逻辑电路200c是指图2c的输出逻辑电路228。如图2c所示,输出逻辑电路228可以包括各种组件,包括或非(nor)逻辑电路230和开关232。

[0045]

如图2c所示,输出逻辑电路228可以被实现为具有逻辑门(例如,或非(nor)逻辑电路230)的弱下拉电路,该逻辑门从(图2a的)核斜坡检测电路212接收核斜坡感测信号(sns),从(图2a的)保持逻辑电路214接收输出保持信号(rto),并提供激活信号(out)。在一些情况下,在接收到处于第一逻辑状态(例如,逻辑0状态)的核斜坡感测信号(sns)之后并且在接收到处于第二逻辑状态(例如,逻辑0状态)的输出保持信号(rto)之后,激活信号(out)可以用于激活开关232,开关232将输出焊盘结构118a耦合到地(gnd或vss)。

[0046]

开关232可以在节点(out1)处耦合在输出焊盘结构118a与地(gnd或vss)之间。在

一些情况下,输出焊盘结构118a可以具有至少大于10k(即,rwk_pd>10kω)的弱下拉电阻(rwk_pd)。此外,输出焊盘结构118a可以用于提供输出io信号。

[0047]

在一些实施方式中,激活信号(out)可以被称为weak_pull_enable信号,其可以向开关232提供逻辑1状态(逻辑1)或逻辑0状态(逻辑0)。例如,具有逻辑1状态(out=1)的weak_pull_enable信号可以参考处于导通(on)状态的有效弱下拉(weak pulldown)而提供给闭合的开关232。此外,在这种情况下,具有逻辑0状态(out=0)的weak_pull_enable信号可以参考处于断开(off)状态的有效弱下拉而提供给断开的开关232。

[0048]

参考图2d,输出逻辑电路200d是指可以在输出焊盘结构118a处耦合到图2c的输出弱拉逻辑电路228的输出逻辑电路248。如图2d所示,输出逻辑电路248可以包括各种组件,包括晶体管(m1,m2)、预驱动器电路250以及核逻辑和电平位移器电路252。

[0049]

如图2d所示,晶体管(m1、m2)可以耦合在io电压(io_p1)与地(vss)之间。输出焊盘结构118a可以耦合在节点(out1)与晶体管(m1,m2)之间。在一些情况下,晶体管(m1)可以是pmos晶体管,并且晶体管(m2)可以是nmos晶体管。此外,预驱动器电路250可以耦合在io电压(io_p1)与地(vss)之间,并且预驱动器电路250可以耦合到晶体管(m1,m2)的栅极。此外,核逻辑和电平位移器电路252可以耦合在io电压(io_p1)与地(vss)之间,并且核逻辑和电平位移器电路252可以耦合到预驱动器电路250。此外,核逻辑和电平位移器电路252可以耦合在核电压(core_p1)与地(vss)之间。核逻辑和电平位移器电路252可以接收数据输入信号(data_in),并且向预驱动器电路250提供电平位移的数据输入信号。

[0050]

图3示出了根据本文所述的各种实施方式的核检测电路300的图。

[0051]

如图3所示,核检测电路300可以包括一个或多个晶体管(t1,t2,...,t10)和一个或多个电阻器(r1,r2),其布置并耦合在一起以接收输入信号(core_p1,io_p1_det)并提供输出信号(core_p1_det,core_p1_detb)。

[0052]

在图3中,电阻器(r1)可以耦合在输入节点(core_p1)与节点(n1)处的晶体管(t2)的栅极之间,并且晶体管(t1)可以耦合在节点(n1)处的晶体管(t2)的栅极与地(gnd或vss)之间。晶体管(t1)可以耦合为栅极接地的nmos晶体管。此外,电阻器(r2)可以耦合在电源(vdd)与节点(n2)处的晶体管(t2)之间,并且晶体管(t2)可以耦合在节点(n2)处的电阻器(r2)与地(gnd或vss)之间。晶体管(t3)可以耦合在电源(vdd)与节点(n2)之间,并且输入信号(io_p1)可以耦合到晶体管(t3)的栅极。晶体管(t4)可以具有一起耦合到电源(vdd)的源极和漏极,并且节点(n2)可以耦合到晶体管(t4)的栅极。晶体管(t5,t6)可以耦合为电源(vdd)与地(gnd或vss)之间的反相器。此外,节点(n2)可以耦合到晶体管(t5,t6)的栅极,并且节点(n3)可以耦合在晶体管(t5,t6)之间。在一些情况下,节点(n3)可以具有节点电压(core_p1_detb),其可以被称为用于核电压(core_p1)的反相核检测信号。晶体管(t7)可以具有一起耦合到地(gnd或vss)的源极和漏极,并且节点(n3)可以耦合到晶体管(t7)的栅极。晶体管(t8)可以耦合在节点(n3)与地(gnd或vss)之间,并且晶体管(t8)可以耦合为栅极接地的nmos晶体管。晶体管(t9,t10)可以耦合为io电压(io_p1)与地(gnd或vss)之间的反相器。此外,节点(n3)可以耦合到晶体管(t9,t10)的栅极,并且节点(n4)可以耦合在晶体管(t9,t10)之间。在一些情况下,节点(n4)可以具有节点电压(core_p1_det),其可以被称为用于核电压(core_p1)的核检测信号。

[0053]

在一些实施方式中,一个或多个晶体管(t1,t2,...,t10)可以包括使用互补金属

氧化物半导体(cmos)型晶体管。例如,一些晶体管(t1,t2,t5,t7,t8,t9)可以包括nmos晶体管,而一些晶体管(t3,t4,t6,t10)可以包括pmos晶体管。然而,可以使用各种其他实施方式。

[0054]

图4a至图4b示出了根据本文所述的各种实施方式的核斜坡检测电路的图。特别地,图4a示出了(图2a的)核斜坡检测电路212的第一部分212a的示意图400a,并且图4b示出了(图2a的)核斜坡检测电路212的第二部分212b(在被圈住的元件a处耦合到第一部分212a)的示意图400b。

[0055]

如图4a所示,核检测电路212a可以包括一个或多个晶体管(t11,t12,...,t27)和一个或多个电阻器(r3),其布置并耦合在一起以接收输入信号(core_p1_det,io_p1_det,reton),并在节点(n7)处提供输出信号,该节点(n7)是指被圈住的元件a。

[0056]

在图4a中,晶体管(t11)可以耦合在节点(n5)与地(gnd或vss)之间,并且晶体管(t11)可以耦合为栅极接地的nmos晶体管。晶体管(t15)可以耦合在节点(n5)与节点(n6)之间,并且电阻器(r3)可以耦合在电源(vdd)与晶体管(t15)的栅极之间。晶体管(t12)可以耦合在晶体管(t13)的栅极与地(gnd或vss)之间,并且晶体管(t12)可以耦合为栅极接地的nmos晶体管。此外,retoff信号可以耦合到晶体管(t13)的栅极。晶体管(t13,t14)可以串联耦合在节点(n5)与地(gnd或vss)之间。此外,输入信号(core_p1_det)可以耦合到晶体管(t14)的栅极。晶体管(t16,t17)可以耦合为电源(vdd)与地(gnd或vss)之间的反相器。此外,节点(n7)可以耦合到晶体管(t16,t17)的栅极,并且节点(n6)可以耦合在晶体管(t16,t17)之间。晶体管(t18)可以具有一起耦合到地(gnd或vss)的源极和漏极,并且节点(n6)可以耦合到晶体管(t18)的栅极。晶体管(t19)可以耦合在节点(n6)与地(gnd或vss)之间,并且晶体管(t19)可以耦合为栅极接地的nmos晶体管。晶体管(t20,t21)可以耦合为电源(vdd)与地(gnd或vss)之间的反相器。此外,节点(n6)可以耦合到晶体管(t20,t21)的栅极,并且节点(n7)可以耦合在晶体管(t20,t21)之间。

[0057]

此外,在图4a中,晶体管(t22)可以耦合在节点(n7)与节点(n8)之间,并且输入信号(io_p1_det)可以耦合到晶体管(t22)的栅极。晶体管(t25)可以耦合在晶体管(t23)的栅极与地(gnd或vss)之间,并且晶体管(t25)可以耦合为栅极接地的nmos晶体管。此外,在一些情况下,输入信号(reton)可以耦合到晶体管(t23)的栅极。晶体管(t23,t24)可以串联耦合在节点(n8)与地(gnd或vss)之间,并且输入信号(core_p1_det)可以耦合到晶体管(t24)的栅极。晶体管(t27)可以耦合在节点(n8)与地(gnd或vss)之间,并且晶体管(t27)可以耦合为栅极接地的nmos晶体管。晶体管(t26)可以耦合在电源(vdd)和节点(n7)之间,并且输入信号(io_p1_det)可以耦合到晶体管(t26)的栅极。晶体管(t28)可以具有一起耦合到电源(vdd)的源极和漏极,并且节点(n7)可以耦合到晶体管(t28)的栅极。此外,核斜坡检测电路212(如图2a所示)的第一部分212a可以在被圈住的元件a(指节点(n7))处耦合到核斜坡检测电路212(如图2b所示)的第二部分212b。

[0058]

在一些实施方式中,一个或多个晶体管(t11,t12,...,t28)可以包括使用cmos型晶体管。例如,一些晶体管(t11,t12,t13,t14,t15,t16,t18,t19,t20,t22,t23,t24,t25,t27)可以包括nmos晶体管,而一些晶体管(t17,t21,t26,t28)可以包括pmos晶体管。然而,可以使用各种其他实施方式。

[0059]

在图4b中,晶体管(t29)可以耦合在节点(n7)和地(gnd或vss)之间,并且晶体管

(t29)可以耦合为栅极接地的nmos晶体管。晶体管(t30,t31)可以耦合为电源(vdd)与地(gnd或vss)之间的反相器。此外,节点(n7)可以耦合到晶体管(t30,t31)的栅极,并且节点(n9)可以耦合在晶体管(t30,t31)之间。晶体管(t32)可以具有一起耦合到地(gnd或vss)的源极和漏极,并且节点(n9)可以耦合到晶体管(t32)的栅极。晶体管(t33,t34)可以耦合为电源(vdd)与地(gnd或vss)之间的反相器。此外,节点(n9)可以耦合到晶体管(t33,t34)的栅极,并且节点(n10)可以耦合在晶体管(t33,t34)之间。在一些情况下,节点(n10)可以具有节点电压(core_ramp),其可以被称为用于核电压(core_p1)的核斜坡信号。此外,在一些情况下,逻辑门404(例如,与非(nand)门)可以耦合在作为电源输入的io电压(io_p1)与地(gnd或vss)之间。逻辑门404(例如,与非门)可以具有多个输入,包括耦合到输入电压(core_p1_detb)的第一输入和耦合到节点(n10)的第二输入。逻辑门404(例如,与非门)可以提供核斜坡感测信号(sns)作为输出。在一些情况下,参考图4b,逻辑门404(例如,与非门)可以指图2b中的感测(sns)逻辑电路224。

[0060]

在一些实施方式中,一个或多个晶体管(t29,t30,...,t34)可以包括使用cmos型晶体管。例如,一些晶体管(t29,t30,t32,t33)可以包括nmos晶体管,而一些晶体管(t31,t34)可以包括pmos晶体管。然而,可以使用各种其他实施方式。

[0061]

图5a至图5b示出了根据本文所述的各种实施方式的保持逻辑电路的图。特别地,图5a示出了(图2a的)保持逻辑电路214的第一部分214a的示意图500a,并且图5b示出了(图2a的)保持逻辑电路214的第二部分214b(在被圈住的元件b处耦合到第一部分214a)的示意图500b。

[0062]

如图5a所示,核斜坡检测电路214a可以包括一个或多个晶体管(t40,t41,...,t54)和一个或多个电阻器(r4),其布置并耦合在一起以接收输入信号(core_p1_det,io_p1_det,reton,retoff),并在节点(n13)处提供至少一个输出信号,该节点(n13)可以指被圈住的元件b。

[0063]

在图5a中,晶体管(t40)可以耦合在节点(n11)处的晶体管(t41)的栅极与地(gnd或vss)之间,并且晶体管(t40)可以耦合为栅极接地的nmos晶体管。晶体管(t41,t42)可以串联耦合在节点(n12)与地(gnd或vss)之间。此外,输入信号(core_p1_det)可以耦合到晶体管(t42)的栅极,并且输入信号(retoff)可以耦合到晶体管(t41)的栅极。晶体管(t43)可以耦合在电源(vdd)与节点(n12)之间,并且输入信号(io_p1_det)可以耦合到晶体管(t43)的栅极。晶体管(t44)可以具有一起耦合到电源(vdd)的源极和漏极,并且节点(n12)可以耦合到晶体管(t44)的栅极。晶体管(t45,t46)可以耦合为电源(vdd)与地(gnd或vss)之间的反相器。此外,节点(n13)可以耦合到晶体管(t45,t46)的栅极,并且节点(n12)可以耦合在晶体管(t45,t46)之间。晶体管(t47)可以具有一起耦合到地(gnd或vss)的源极和漏极,并且节点(n13)可以耦合到晶体管(t47)的栅极。晶体管(t48)可以耦合在节点(n13)与地(gnd或vss)之间,并且晶体管(t48)可以耦合为栅极接地的nmos晶体管。晶体管(t49,t50)可以耦合为电源(vdd)与地(gnd或vss)之间的反相器。此外,节点(n12)可以耦合到晶体管(t49,t50)的栅极,并且节点(n13)可以耦合在晶体管(t49,t50)之间。

[0064]

此外,在图5a中,晶体管(t51)可以耦合在节点(n13)与节点(n14)之间,并且输入信号(reton)可以经由电阻器(r4)耦合到晶体管(t51)的栅极。晶体管(t54)可以耦合在晶体管(t52)的栅极与地(gnd或vss)之间,并且晶体管(t54)可以耦合为栅极接地的nmos晶体

管。此外,在一些情况下,输入信号(reton)可以耦合到晶体管(t52)的栅极。晶体管(t52,t53)可以串联耦合在节点(n14)与地(gnd或vss)之间,并且输入信号(core_p1_det)可以耦合到晶体管(t53)的栅极。晶体管(t55)可以耦合在节点(n14)与地(gnd或vss)之间,并且晶体管(t55)可以耦合为栅极接地的nmos晶体管。此外,核斜坡检测电路214(如图2a所示)的第一部分214a可以在被圈住的元件b(指节点(n13))处耦合到核斜坡检测电路214(如图2b所示)的第二部分214b。

[0065]

在一些实施方式中,一个或多个晶体管(t40,t41,...,t55)可以包括使用cmos型晶体管。例如,一些晶体管(t40,t41,t42,t45,t47,t48,t49,t51,t52,t53,t54,t55)可以包括nmos晶体管,而一些晶体管(t43,t44,t46,t50)可以包括pmos晶体管。然而,可以使用各种其他实施方式。

[0066]

在图5b中,晶体管(t56)可以耦合在节点(n13)与地(gnd或vss)之间,并且晶体管(t56)可以耦合为栅极接地的nmos晶体管。晶体管(t57,t58)可以耦合为电源(vdd)与地(gnd或vss)之间的反相器。此外,节点(n13)可以耦合到晶体管(t57,t58)的栅极,并且节点(n15)可以耦合在晶体管(t57,t58)之间。晶体管(t59)可以具有一起耦合到地(gnd或vss)的源极和漏极,并且节点(n15)可以耦合到晶体管(t59)的栅极。晶体管(t60,t61)可以耦合为电源(vdd)与地(gnd或vss)之间的反相器。此外,节点(n15)可以耦合到晶体管(t60,t61)的栅极,并且节点(n16)可以耦合在晶体管(t60,t61)之间。晶体管(t62)可以具有一起耦合到电源(vdd)的源极和漏极,并且节点(n16)可以耦合到晶体管(t62)的栅极。在一些情况下,节点(n15)提供反相输出保持信号(rto_inv),并且节点(n16)提供输出保持信号(rto)。

[0067]

在一些实施方式中,一个或多个晶体管(t56,t57,...,t62)可以包括使用cmos型晶体管。例如,一些晶体管(t56,t57,t59,t60)可以包括nmos晶体管,而一些晶体管(t58,t61,t62)可以包括pmos晶体管。然而,可以使用各种其他实施方式。

[0068]

在一些实施方式中,pvsense单元108可以结合并组合使用与图3的核检测电路210、图2a至图2b的核斜坡检测电路212a、212b以及图5a至图5b的保持逻辑电路214a、214b相关联的多个电路。因此,参考图3至图5b,pvsense单元108可以结合与电路210、212a、212b、214a、214b的组合相关联的操作特性和行为,其可以如下操作。

[0069]

在第一核电源斜坡期间,core_p1=0,因此,core_p1_det=0以及core_p1_detb=1。因此,sns可以取决于第一核斜坡检测块212a、212b的输出。由于core_p1_det为“0”,因此nmos晶体管t14和t24处于关断状态。因此,输入reton和retoff被禁用,并且对输出core_ramp无控制。在这种情况下,当io_p1开始斜升时,则pmos晶体管t28将电荷耦合到设置在第一核斜坡检测块212a、212b中的锁存器的右侧。同时,nmos晶体管t11(指像泄漏器件一样操作的栅极接地的nmos)开始使锁存器的左节点放电。该操作将锁存器的右分支转为“1”,并将锁存器的左侧接地为“0”。此外,core_ramp被设置为“1”,并且sns被设置为“0”。

[0070]

保持块214a、214b可以以类似的方式操作,尽管一些连接是不同的。例如,由于core_p1_det为“0”,则nmos晶体管t42和t53被禁用。当io_p1开始斜升时,则额外的电荷可以通过pmos晶体管t44耦合到保持块214a、214b中的锁存器的左侧,并且右侧可以通过泄漏器件t55放电。因此,锁存器的左侧可以被转为“1”,并且锁存器的右侧可以被转为“0”。此外,rto最终变为“0”。

[0071]

在这种情况下,可以将sns=0和rto=0传送到第一io单元112,以便启用第一io单

元112中的弱下拉逻辑,其使得pad=0。在正常操作的情况下,core_p1=1,因此,core_p1_det变为“1”,并且然后最终sns变为“1”。在这种情况下,或者即当core_p1稳定且为“1”时,sns可以不取决于第一核斜坡逻辑,然后可以禁用第一核斜坡检测块212a、212b。在保持块214a、214b中,当core_p1_det为“1”时,可以启用nmos晶体管t52和t41。因此,分支接受输入reton和retoff并根据reton和retoff的值进行操作。

[0072]

在一些实施方式中,本文所述的各种方案和技术提供了参考io电压环在核掉电模式期间大量节电。本文所述的各种方案和技术可以用于通常需要节电的许多iot特定应用(例如,可穿戴设备、常开设备等)中。本文所述的各种方案和技术基于应用允许核参考维持或三态化逻辑状态来利用焊盘操作条件。此外,本文所述的各种方案和技术通过利用附加的检测电路来解决第一核斜坡保持问题,其中,针对其他核掉电模式禁用附加检测电路,并且参考第一核斜坡实例,附加检测电路变为活动状态。因此,这些方案和技术可能不需要使用额外的电流,这可以保持针对其使用的焊盘操作条件。

[0073]

本文描述了设备的各种实施方式。该设备可以包括输出焊盘,该输出焊盘提供来自io电源的输入输出(io)电压。该设备可以包括核斜坡检测电路,其检测来自核电源的核电压的第一斜坡并且提供核斜坡感测信号。该设备可以包括输出逻辑电路,其在接收到核斜坡感测信号之后将输出焊盘耦合到地,以便减少io电源的泄漏。

[0074]

本文描述了系统的各种实施方式。该系统可以包括第一芯片,第一芯片具有感测电路和具有第一输出焊盘的第一输入/输出(io)单元,该第一输出焊盘提供来自io电源的输入输出电压和来自核电源的核电压中的至少一个。该系统可以包括具有第二io单元的第二芯片,该第二io单元具有第二输出焊盘,该第二输出焊盘从第一输出焊盘接收io电压和核电压中的至少一个。感测电路可以检测核电压的第一斜坡并且将第一输出焊盘耦合到地,直到核电源开始第一次斜升,以减少io电压和核电压中的至少一个到第二输出焊盘的泄漏。

[0075]

本文描述了方法的各种实施方式。该方法可以包括经由输出焊盘提供输入输出(io)电压。该方法可以包括检测核电压的第一斜坡。该方法可以包括在检测核电压的第一斜坡期间生成斜坡感测信号。该方法可以包括在接收到斜坡感测信号之后将输出焊盘耦合到地,以便减少io电压和核电压中的至少一个的泄漏。

[0076]

应当意图的是,权利要求的主题不限于本文提供的实施方式和说明,而是包括那些实施方式的修改形式,其包括根据权利要求的实施方式的部分以及不同实施方式的元素的组合。应当理解,在任何这种实施方式的开发中,如在任何工程或设计项目中,应做出许多特定于实施方式的决定以实现开发者的特定目标,例如服从系统相关和业务相关的约束,这可能在实施方式之间不同。此外,应当理解,这种开发尝试可能是复杂且耗时的,但依然是具有本公开的益处的本领域普通技术人员惯用的设计、制作和制造。

[0077]

已经详细参考了各种实施方式,其示例在附图和图中示出。在下面的详细描述中,阐述了许多具体细节以提供对本文提供的公开的透彻理解。然而,本文提供的公开可以在没有这些具体细节的情况下实施。在一些其他情况下,没有详细描述公知的方法、过程、组件、电路和网络,以避免不必要地使实施例的细节模糊不清。

[0078]

还应当理解,尽管本文可以使用术语第一、第二等来描述各种元件,但是这些元件不应被这些术语限制。这些术语仅用来将元件彼此区分。例如,第一元件可以被称为第二元

件,并且类似地,第二元件可以被称为第一元件。第一元件和第二元件二者分别是元件,但是它们不被认为是相同的元件。

[0079]

本文提供的本公开的描述中使用的术语是为了描述特定实施方式,并不旨在限制本文提供的公开。除非上下文另外明确指示,否则如本文提供的公开的描述和所附权利要求中使用的单数形式“一”、“一个”和“所述”也旨在包括复数形式。如本文所使用的术语“和/或”是指并且包括一个或多个关联列出项目的任何和所有可能的组合。当在本说明书中使用时,术语“包括”、“包含”、“含有”和/或“具有”指定所陈述的特征、整数、步骤、操作、元件和/或组件的存在,但是并没有排除一个或多个其它特征、整数、步骤、操作、元件、组件和/或其组合的存在或附加。

[0080]

如本文所使用的,取决于上下文,术语“如果”可以被解释为意指“当

……

时”或“在

……

时”或“响应于确定”或“响应于检测到”。类似地,取决于上下文,短语“如果确定”或“如果检测到[所陈述的条件或事件]”可以被解释为意指“在确定时”或“响应于确定”或“在检测到[所陈述的条件或事件]时”或“响应于检测到[所陈述的条件或事件]”。术语“上”和“下”;“更高”和“更低”;“向上”和“向下”;“下面”和“上面”;以及指示在给定点或元件上方或下方的相对位置的其他类似术语可以结合本文所述的各种技术的一些实施方式来使用。

[0081]

尽管前述内容针对本文所描述的各种技术的实施方式,但可以根据本文的公开设计其他及进一步的实施方式,其可以由所附权利要求确定。

[0082]

尽管已经以对结构特征和/或方法动作特定的语言描述了主题,但是应当理解,在所附权利要求中限定的主题不必受限于上面描述的特定特征或动作。相反,上面描述的特定特征和动作是作为实现权利要求的示例形式而公开的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1