一种脉宽可调整的无级延时电路及多通道探地雷达的制作方法

[0001]

本实用新型涉及探地雷达技术领域,特别是涉及一种脉宽可调整的无级延时电路及多通道探地雷达。

背景技术:

[0002]

超宽带雷达技术是利用宽频带的窄脉冲电磁波探测介质分层情况或者障碍物后、介质层中所掩藏的目标信息的一种无损探测方法,具有穿透能力强、抗干扰能力强、分辨率高、结构简单等特点,在地质勘探、道路质量检测评估、穿墙成像、反恐等多种民用及军事领域具有非常广泛的应用。其中多通道探地雷达在探测效率方面具有无可比拟的优势,尤其在城市道路病害探测方面,可以大幅度提高作业效率。触发信号延时器是超宽带雷达系统的重要组成部分,在一定程度上,不同通道之间的触发信号的延时量的不同影响了不同通道信号之间的一致性,故触发信号延时器的选取与设计对于多通道探地雷达系统至关重要。

[0003]

当前,利用半导体器件产生触发脉冲信号延时的方法大概分为几类:一种是利用mcu或者fpga等数字芯片产生不同延时量的窄脉冲触发信号;另一种是基于高精度精密延时芯片实现触发信号的延时量的调整;另一种是基于模拟芯片利用电容或者电感的充放电时间的不同产生不同延时量的窄脉冲触发信号,这种电路是是利用其不同rc或者rl组合所产生的时间常数不同,从而实现触发信号的延时。

[0004]

现有的多通道探地雷达不同通道的触发信号延时大多依靠数字芯片产生的窄脉冲信号延时来实现,通过提高数字芯片的工作时钟可以产生更精细的时钟信号,从而提高触发信号延时的精度,但是数字芯片工作时钟的提高一方面会加大系统的功耗,另一方面数字芯片工作时钟的提高也会有一个极限,一般数字芯片产生的触发信号的延时精度基本都在纳秒量级,都用来进行粗延时调整;而通过高精度精密延时芯片产生不同延时量的触发信号虽然会提高延时的精度,一般会精确到5皮秒量级,但这会增加系统的复杂度,且需要高精度精密延时芯片实现不同的延时量需要数字芯片配合来产生控制延时量的控制字,且有一个极限分辨率,高精密延时芯片的功耗一般都比较高。不同通道之间由于走线长度不一致、器件参数不同导致的产生发射信号的时间点不一致,这些因素都会导致不同通道接收到的回波信号的直达波信号到达的时间不一致,从而影响不同通道之间的信号的一致性。

技术实现要素:

[0005]

本实用新型要解决的技术问题是提供一种脉宽可调整的无级延时电路及多通道探地雷达,能够克服现有以数字芯片为基础制作的延时电路精度过低、复杂度过高、功耗过高的问题。

[0006]

为解决上述技术问题,本实用新型提供了一种脉宽可调整的无级延时电路,所述电路包括:脉冲信号无级延时调整电路,其中,脉冲信号无级延时调整电路包括:耦合电容

c6、第一高速d触发器u3、第五电阻r5、第一可调电阻rp1、第七电容c7,耦合电容c6连接至第一高速d触发器u3 的时钟输入端,第一高速d触发器u3的数据输入端及置位输入端连接至电源vcc,第一高速d触发器u3的反相输出端连接至第五电阻r5的一端,第五电阻r5的另一端连接第一可调电阻rp1的一个定片引脚,第一可调电阻 rp1的另一个定片引脚连接至第一可调电阻rp1的动片引脚及第一高速d触发器u3的复位输入端,另一个定片引脚还连接至第七电容c7的一端,第七电容c7的另一端接地。

[0007]

在一些实施方式中,还包括:脉宽无级调整电路,脉宽无级调整电路包括:第二高速d触发器u4、第六电阻r6、第二可调电阻rp2、第八电容 c8、第九电容c9及第一电感l1,第二高速d触发器u4的时钟输入端连接至第一高速d触发器u3的反相输出端,第二高速d触发器u4的数据输入端及置位输入端连接至电源vcc,第二高速d触发器u4的正相输出端连接第九电容c9的一端,第九电容c9的另一端连接第一电感l1的一端,第一电感l1的另一端连接至高压电源hv,第二高速d触发器u4的反相输出端连接至第六电阻r6的一端,第六电阻r6的另一端连接第二可调电阻rp2 的一个定片引脚,第二可调电阻rp2的另一个定片引脚连接至第二可调电阻rp2的动片引脚及第二高速d触发器u4的复位输入端,另一个定片引脚还连接至第八电容c8的一端,第八电容c8的另一端接地。

[0008]

在一些实施方式中,还包括:脉冲信号整形电路,脉冲信号整形电路包括:第一反相器u1、第一高速二极管d3、第二反相器u2、第四电阻r4、第四电容c4、第五电容c5、第四二极管d4、第五二极管d5,其中,第一反相器u1的输出端连接至第一高速二极管d3的负极,第一高速二极管d3 的正极连接至第二反相器u2的输入端,第二反相器u2的输出端分别连接至第四二极管d4的正极、第五二极管d5的负极及耦合电容c6,第四二极管d4的负极连接至第五电容c5及第四电阻r4的一端,第五电容c5的另一端接地,第四电阻r4的另一端连接至电源vcc,并与第四电容c4的一端连接,第四电容c4的另一端接地,第五二极管d5的正极接地。

[0009]

在一些实施方式中,还包括:滤波与保护电路,滤波与保护电路包括:第一电阻r1、第二电阻r2、第三电阻r3、第一电容c1、第二电容c2、第三电容c3、第一二极管d1及第二二极管d2,其中,第一电容c1的一端连接输入信号,另一端与第一电阻r1及第二电阻r2的一端连接,第一电阻r1的另一端接地,第二电阻r2的另一端与第一二极管d1的正极及第二二极管d2的负极连接,第一二极管d1的负极连接至第三电容c3及第三电阻 r3的一端,第三电容c3的另一端接地,第三电阻r3的另一端连接至电源 vcc,并且与第二电容c2的一端连接,第二电容c2的另一端接地,第二二极管d2的正极接地,第二电阻r2的另一端还与第一反相器u1的输入端连接。

[0010]

在一些实施方式中,第一反相器u1与第二反相器u2均为施密特反相器。

[0011]

在一些实施方式中,输入触发信号的幅度介于1.8v~5v之间,脉冲宽度介于50ns~500ns之间,信号重复频率介于20khz~400khz之间。

[0012]

此外,本实用新型还提供了一种多通道探地雷达,该多通道探地雷达包括:根据前文所述的脉宽可调整的无级延时电路。

[0013]

采用这样的设计后,本实用新型至少具有以下优点:

[0014]

(1)利用高速d触发器构建的脉冲信号无级延时调整电路,与普通的数字芯片或者延时芯片构建的电路相比,该脉冲信号无级延时调整电路可以实现延时量的无级调整,结

构简单,实现不同通道之间延时量的精确调整,提高了道间一致性。

[0015]

(2)利用高速d触发器构建的脉冲信号整形电路,与普通的数字芯片构建的脉宽调整电路相比,该脉宽调整电路调整的精度更高,可以实现脉冲信号占空比的无级调整,且结构简单、可靠性更高。

[0016]

(3)通过高速二极管和施密特反相器的整形,输出信号的上升沿和下降沿更加陡峭,抖动更小,使触发信号质量更高。

附图说明

[0017]

上述仅是本实用新型技术方案的概述,为了能够更清楚了解本实用新型的技术手段,以下结合附图与具体实施方式对本实用新型作进一步的详细说明。

[0018]

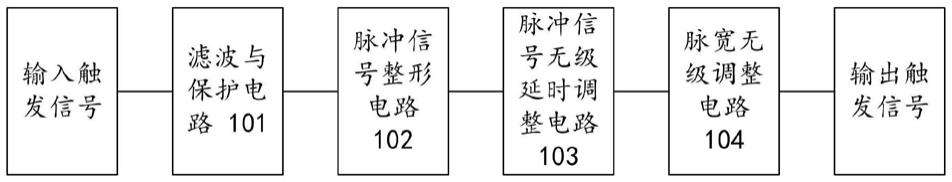

图1是本实用新型实施例提供的适用多通道探地雷达的脉宽可调整的无级延时电路的电路结构框图;

[0019]

图2是本实用新型实施例提供的适用多通道探地雷达的脉宽可调整的无级延时电路的电路原理图。

具体实施方式

[0020]

以下结合附图对本实用新型的优选实施例进行说明,应当理解,此处所描述的优选实施例仅用于说明和解释本实用新型,并不用于限定本实用新型。

[0021]

请参照图1和图2,本实施例一种适用多通道探地雷达的脉宽可调整的无级延时电路包括:

[0022]

滤波与保护电路101,用于输入信号滤波与后端电路保护,防止输入信号过大导致后端电路损坏;脉冲信号整形电路102,其前端电性连接至输入信号滤波与保护电路,用于对脉冲信号的边沿进行整形处理;脉冲信号无级延时调整电路103,其前端电性连接至脉冲信号整形电路,用于对脉冲信号的延时实现无级调整,实现不同通道触发延时的精确调整,保证道间一致性;脉宽无级调整电路104,其前端电性连接至脉冲信号无级延时调整电路,用于对脉冲信号的宽度(占空比)进行无级的调整,适应不同发射机或接收机的触发要求。

[0023]

以下分别对本实施例一种适用多通道探地雷达的脉宽可调整的无级延时电路的各个组成部分进行详细说明。

[0024]

首先说明滤波与保护电路101的电路结构。

[0025]

本实施例中,输入的触发脉冲信号是幅度为3.3v、脉冲宽度为200ns、信号重复频率为200khz的方波信号,本实用新型并不以此为局限,触发信号的幅度可以介于1.8v~5v之间,脉冲宽度可以介于50ns~500ns之间,信号重复频率可以介于20khz~400khz之间。

[0026]

请参考图2,滤波与保护电路101包括:第一电阻r1、第二电阻r2、第三电阻r3、第一电容c1、第二电容c2、第三电容c3、第一二极管d1和第二二极管d2,其中第一电容c1的第一端连接至触发脉冲信号输入端,第一电容c1的第二端连接至第一电阻r1的第一端与第二电阻r2的第一端,第一电阻r1的第二端接地,第二电阻r2的第二端连接至第一二极管d1的第一端和第二二极管d2的第二端,第二二极管d2的第一端接地,第一二极管d1的第二端连接至第三电阻r3的第一端和第二电容c2的第一端,第二电容c2的第二段接地,第三电阻r3的第二端连接至电源vcc和第三电容c3的第一端,第三电容c3的第二端接地。

[0027]

该滤波与保护电路101中,第一电阻r1与第一电容c1共同组成的高通滤波网络对输入的信号进行初步的滤波,隔离直流分量等干扰信号,让设计重复频率范围内(20khz~400khz)的信号通过,第二电阻r2作为脉冲整形电路的匹配输入电阻,第一二极管d1、第二二极管d2、第三电阻r3、第二电容c2、第三电容c3共同组成输入保护电路,将输入信号钳位在0~ vcc之间,防止输入信号过大导致后端电路损坏。

[0028]

其次,说明脉冲信号整形电路102的电路结构。

[0029]

请参照图2,脉冲信号整形电路102包括:第一反相器u1、第一高速二极管d3、第二反相器u2、第四电阻r4、第四电容c4、第五电容c5、第四二极管d4、第五二极管d5,其中第一反相器u1的第一端连接至输入信号滤波与保护电路的第二电阻r2的第二端,第一反相器u1的第二端连接至第一高速二极管d3的第二端,第一高速二极管d3的第一端连接至第二反相器u2的第一端,第二反相器u2的第二端连接至第四二极管d4的第一端和第五二极管d5的第二端,第五二极管d5的第一端接地,第四二极管 d4的第二端连接至第四电阻r4的第一端和第五电容的第一端、第四电阻 r4的第二端和第四电容c4的第一端共同连接至电源vcc,第四电容c4第二端和第五电容c5的第二端共同接地。

[0030]

该脉冲信号整形电路102中,第一和第二反相器u1、u2对脉冲信号的边沿进行整形,将边沿变化缓慢的脉冲信号变换为边沿很陡的矩形脉冲信号,并阻止由于输入电压出现微小变化(低于某一阈值)而引起的输出信号的改变,第一高速二极管d3对u1输出的负脉冲信号进行整形,使脉冲信号的边沿更加陡峭,提高触发脉冲信号的质量,第一高速二极管d3、第四二极管d4、第四电阻r4、第四电容c4和第五电容c5共同组成脉冲整形电路的输出保护装置,将输出信号钳位在0~vcc之间,防止输出信号过大导致后端电路损坏。

[0031]

再次,说明脉冲信号无级延时调整电路103的电路结构。

[0032]

请参照图2,脉冲信号无级延时调整电路103包括:耦合电容c6、第一高速d触发器u3、第五电阻r5、第一可调电阻rp1、第7电容c7,其中耦合电容c6的第一端连接至整形电路的输出端即第二反相器的第二端,第六电容c6的第二段连接至第一高速d触发器u3的时钟输入端即第三端,第一高速d触发器的数据输入端第二端和置位输入端第四段连接至电源 vcc,第一高速d触发器u3的正相输出端第五输出端不接,第一高速d触发器u3的反相输出端第六端连接至第五电阻r5的第一端,第五电阻r5的第二端连接至可调电阻rp1的第二端,可调电阻rp1的第一端连接至第一高速d触发器u3的复位输入端和自身的第三端,第一可调电阻rp1的第三端连接至第七电容c7的第一端,第七电容c7的第二端连接至地。

[0033]

该脉冲信号无级延时调整电路103中,耦合电容c6对输入的触发方波信号整形,利用电容对方波信号的微分作用,锐化触发信号并作为第一高速d触发器u3的输入时钟信号,第一高速d触发器u3的输入信号和置位端都连接至高电平vcc,使触发器的输出信号只由时钟的上升沿和复位(清零)端决定,第一高速d触发器u3的正相输出端不使用,本实用新型只使用到了第一高速d触发器u3的负相输出端,第一高速d触发器u3的负相输出端连接至第五电阻r5、第一可调电阻rp1和第七电容c7组成rc网络,并通过第一可调电阻rp1的第一端将输出信号反馈至第一高速d触发器u3 的复位端,通过调整第五电阻r5、第一可调电阻rp1和第七电容c7的参数的数值来调整其所组成的rc网络的时间常数,从而使反馈至复位端的反馈信号的低电平到来的时间的长短来实现脉冲信号延时的长短,通过调整五电阻r5和第七电容c7的参数数值可确定脉冲信号延时的一个大致长短,再通过调整第一可调电阻rp1(精

密可调电阻)参数的数值则可实现脉冲信号延时的精密无级调整。

[0034]

最后,说明脉宽无级调整电路104的电路结构。

[0035]

请参照图2,脉冲信号无级延时调整电路104包括:第二高速d触发器 u4、第六电阻r6、第二可调电阻rp2、第8电容c8、第九电容c9、第一电感l1,其中第一高速d触发器u3的时钟输入端即第三端连接至脉冲信号无级延时调整电路的输出端即第一高速d触发器的反相输出端第六端,第二高速d触发器的数据输入端第二端和置位输入端第四段连接至电源vcc,第二高速d触发器的反相输出端第六端连接至第六电阻r6的第一端,第六电阻r6的第二端连接至可调电阻rp2的第二端,可调电阻rp2的第一端连接至第二高速d触发器u4的复位输入端和自身的第三端,可调电阻rp2的第三端连接至第八电容c8的第一端,第八电容c8的第二端连接至地,第二高速d触发器u4的正相输出端第五端连接至第九电容c9的第一端,第九电容c9的第二端连接第一电感l1的第一端共同作为整个电路的输出端,第一电感l1的第二端连接至高压电源(100v~500v)。

[0036]

该脉宽无级调整电路104中,上一级电路的输出信号作为第二高速d 触发器u4的输入时钟信号,第二高速d触发器u4的输入信号和置位端都连接至高电平vcc,使触发器的输出信号只由时钟的上升沿和复位(清零) 端决定,第二高速d触发器u4的负相输出端连接至第六电阻r6、第二可调电阻rp2和第八电容c8组成rc网络,并通过第二可调电阻rp2的第一端将输出信号反馈至第二高速d触发器u4的复位端,通过调整第六电阻r6、第二可调电阻rp2和第八电容c8的参数的数值来调整其所组成的rc网络的时间常数,从而使反馈至复位端的反馈信号的低电平到来的时间的长短来调整输出脉冲信号的宽度,通过调整六电阻r6和第八电容c8的参数数值可确定脉冲信号的大致宽度,再通过调整第二可调电阻rp2(精密可调电阻)参数的数值则可实现脉冲信号宽度的精密无级调整,并通过第二高速d 触发器u4的正相输出端输出,耦合电容c9将最终调整好的信号耦合到输出端,如果作为某些发射机触发信号,可通过第一电感l1将高压电源一起作为输出送给发射机,此时耦合电容c9就需要采用耐高压电容,防止直流高压将第二高速d触发器击穿损坏。

[0037]

本实施例一种适用多通道探地雷达的脉宽可调整的无级延时电路的工作过程如下:

[0038]

步骤一:当触发信号处于低电平状态时,第一二极管d1、第二二极管 d2、第一高速二极管d3、第四二极管d4、第五二极管d5处于反向截止状态,第一高速d触发器u3的第六端反相输出端处于高电平状态,第一端复位端处于高电平状态,第二高速d触发器u4的第六端反相输出端处于高电平状态,第一端复位端处于高电平状态,第五电阻r5和第一可调电阻rp1 对第七充放电电容c7进行充电,第六电阻r6和第二可调电阻rp2对第八充放电电容c8进行充电。

[0039]

步骤二:当触发信号上升沿到来时,触发信号变为高电平,通过第一电容c1的作用,使脉冲锐化,配合第一电阻r1的作用,隔离触发信号中的直流分量,进行高通滤波,并通过输入匹配电阻第二电阻r2输入到脉冲整形电路。第三电阻r3、第二电容c2与第三电容c3组成电源滤波网络为vcc滤波,滤除一些杂波,并通过第一二极管d1与第二二极管d2将输入的脉冲信号钳位在0~vcc之间,如果输入的信号的幅度高于vcc+uth则第一二极管d1导通,将电压稳定在vcc+uth,如果输入信号的电压幅度低于-uth,则第二二极管d2导通,将电压稳定在-uth,一般uth都比较小,介于0.2~ 0.7v之间,这样就可以将输入电压钳位在一个

安全的范围,保证后级电路的安全。

[0040]

步骤三:滤波后的触发信号经过第一反相器u1进行第一次整形,由上升沿转换为下降沿,并且锐化边沿信号,第一反相器u1的输出端状态有高电平转换为低电平,此时第一高速二极管d3导通,将第二反相器u2的输入端由高电平状态转换为低电平状态,并且第一高速二极管d3的快速导通也会对触发信号的边沿进行锐化整形,之后将触发信号输入第二反相器u2 进行第三次整形,由下降沿转换为上升沿,锐化边沿信号,第二反相器u2 的输出端状态也由低电平快速转换为高电平,第四电阻r4、第四电容c4、第五电容c5、第四二极管d4和第五二极管d5共同组成保护网络将输出信号钳位在安全范围内,保证后级电路的安全运行。

[0041]

步骤四:经过整形后的触发信号通过耦合电容c6输出到第一高速d触发器u3的时钟输入端,当时钟输入端的触发信号的上升沿到来后,第六端反相输出端的状态由高电平变换为低电平,第七电容c7通过第五电阻r5 和第一可调电阻rp1开始放电,第七电容c7第一端的电压不能马上突变为低电平,而是通过放电缓慢的降低为低电平(0v),同时第一可调电阻rp1 的第一端的电压也会缓慢地由高电平降低为低电平,并反馈给第一高速d 触发器u3的复位端,当降低为低电平的时候第一高速d触发器u3被复位,其第六端反相输出端变为高电平,并通过第五电阻r5和第一可调电阻rp1 对第七电容c7进行充电,使复位端的输入电压为高电平,其中复位端输入电平由高电平变为低电平的时间和第五电阻r5、第一可调电阻rp1、第七电容c7三者组成的rc网络的时间常数τ1有关系,如果τ1比较大则电平变化的比较缓慢,第一高速d触发器u3的复位时间变长,输出的触发信号的延迟时间变长,相反,如果时间常数τ1比较小较小则电平变化的比较快速,第一高速d触发器u3的复位时间变短,输出的触发信号的延迟时间变短,通过第五电阻r5和第七电容c7的数值可以初步确定延迟时间的一个大概长短,通过对精密可调电阻rp1的数值的调整可以精密地对触发信号的延时进行精密无级调整。

[0042]

步骤五:经延时后的触发信号作为第二高速d触发器u4的时钟输入,此时经延时后的触发信号的相位发生变化,上升沿变为下降沿,下降沿变为上升沿,第一高速d触发器u3经复位输出的延迟信号的上升沿作为第二高速d触发器u4的输入触发信号,当其状态由低电平变为高电平时,第二高速d触发器u4的第六端反相输出端的状态由高电平变换为低电平,第八电容c7通过第六电阻r6和第二可调电阻rp2开始放电,第八电容c8第一端的电压不能马上突变为低电平,而是通过放电缓慢的降低为低电平(0v),同时第二可调电阻rp2的第一端的电压也会缓慢地由高电平降低为低电平,并反馈给第二高速d触发器u4的复位端,当降低为低电平的时候第二高速 d触发器u4被复位,其第六端反相输出端变为高电平,并通过第六电阻r6 和第二可调电阻rp2对第八电容c8进行充电,使复位端的输入电压为高电平,其中复位端输入电平由高电平变为低电平的时间和第六电阻r6、第一可调电阻rp2、第八电容c8三者组成的rc网络的时间常数τ2有关系,如果τ2比较大则电平变化的比较缓慢,第二高速d触发器u4的复位时间变长,第五端输出的触发信号的高电平维持的时间变长,脉宽变宽,相反,如果时间常数τ2比较小较小则电平变化的比较快速,第二高速d触发器 u4的复位时间变短,第五端输出的触发信号的高电平维持的时间变短,脉宽变窄,通过第六电阻r6和第八电容c8的数值可以初步确定一个大概的脉宽宽度,通过对精密可调电阻rp2的数值的调整可以精密地对输出触发信号脉宽行精密无级调整,从而适应不同的发射机或者接

收机对触发脉冲宽度的不同要求。

[0043]

步骤六:经过延时与脉宽调整的触发信号从第二高速d触发器u4的第五端正相输出端通过耦合电容第九电容c9输出到输出端,如果作为某些发射机触发信号,还需要通过第一电感l1将高压直流电源hv(100~500v) 耦合进输出触发信号,同时第一电感l1还可以起到滤除高频交流信号的作用,能够有效滤除高压hv中纹波及部分谐波交流噪声分量,减少噪声对后端电路的影响,如果触发信号不需要高压直流分量,则第一电感l1和高压电源则不需要。

[0044]

经实际测试证明,经本实施例延迟调整过后的脉冲触发信号可以在0~ 1000ps之间进行无级延时,脉宽可以在脉冲宽度可以介于1ns~500ns之间无级调整,信号重复频率可以介于20khz~400khz之间,经处理后的信号上升沿陡峭、抖动小、触发质量高,可以适合不同的发射机与接收机的触发要求,并可以将多通道探地雷达中不同通道的雷达回波信号精确调整到延时一致,充分保证道间一致性。

[0045]

以上所述,仅是本实用新型的较佳实施例而已,并非对本实用新型作任何形式上的限制,本领域技术人员利用上述揭示的技术内容做出些许简单修改、等同变化或修饰,均落在本实用新型的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1