一种用于写入三态内容可寻址存储器的装置及方法与流程

1.本发明涉及存储技术,以及更特别地,涉及用于写入三态内容可寻址存储器的方法及装置。

背景技术:

2.内容可寻址存储器(content-addressable memory,cam)是一种专门为查找密集型应用设计的计算机存储器。由于其并行特性,cam在查找(search)方面比随机存取存储器(random access memory,ram)架构快得多。cam通常用在互联网络由器和交换机中,它们可以提高路由查找、数据报(packet)分类和数据包转发的速度。

3.三元/三态(ternary)cam,或tcam,被设计为使用三种不同的输入(0、1和x)来存储和查询数据。“x”输入,通常被称为“不关心(don't care)”或“通配符(wildcard)”状态,使得tcam能够基于模式匹配执行更广泛的查找,这与二元cam截然不同,后者仅使用0和1执行精确的匹配查找。

技术实现要素:

4.本发明提供一种用于写入三态内容可寻址存储器(tcam)的方法及装置,其在单个的时钟周期中执行包括写入数据输入和写入掩码的写入操作,从而,通过增加执行写入操作的速度显著增强存储器的适用性。

5.一些实施例涉及一种用于写入三态内容可寻址存储器(tcam)的装置,该装置包括三态内容可寻址存储器(tcam)和控制电路,该三态内容可寻址存储器(tcam)包括第一多行存储单元(first plurality of rows of memory cells)和第二多行存储单元(second plurality of rows of memory cells),第一多行存储单元被配置为存储多个相应的数据输入;以及,第二多行存储单元被配置为存储多个相应的掩码(mask);控制电路被配置为:在第一时钟周期中将数据输入写入第一多行存储单元的行(row)中,以及,在该第一时钟周期中将掩码写入第二多行存储单元的行中。

6.在一些实施例中,该控制电路被配置为:响应于该第一时钟周期的第一边沿而将该数据输入写入该第一多行存储单元的行中,以及,还被配置为:响应于该第一时钟周期的第二边沿而将该掩码写入该第二多行存储单元的行中。

7.在一些实施例中,该第一多行存储单元的行和该第二多行存储单元的行共享公共的地址。

8.在一些实施例中,该第一多行存储单元的行和该第二多行存储单元的行彼此相邻。

9.在一些实施例中,该tcam还包括第一总线和第二总线,以及,该控制电路被配置为:使用该第一总线将该数据输入写入该第一多行存储单元的行中;以及,使用该第二总线将该掩码写入该第二多行存储单元的行中。

10.在一些实施例中,该控制电路还被配置为使用该第一总线在该第一多行存储单元

中查找关键词(key)。

11.在一些实施例中,该控制电路还被配置为使用该第二总线在查找操作的期间掩码该tcam的一列或多列。

12.在一些实施例中,该tcam还包括第一总线、第二总线和第三总线,以及,该控制电路被配置为:使用该第一总线将该数据输入写入该第一多行存储单元的行中;使用该第二总线将该掩码写入该第二多行存储单元的行中;以及,在查找操作的期间使用该第三总线掩码该tcam的一列或多列(column)。

13.在一些实施例中,该控制电路还被配置为使用该第二总线在该第一多行存储单元中查找关键词。

14.在一些实施例中,该控制电路还被配置为利用该第一总线在查找操作的期间掩码该tcam的一个或多个列。

15.一些实施例涉及一种用于写入三态内容可寻址存储器(tcam)的方法,包括:在第一时钟周期中,将数据输入写入第一多行存储单元的行中,其中,该第一多行存储单元被配置为存储多个相应的数据输入;以及,

16.在该第一时钟周期中,将掩码写入第二多行存储单元的行中,其中,该第二多行存储单元被配置为存储多个相应的掩码。

17.在一些实施例中,写入该数据输入包括:响应于该第一时钟周期的第一边沿写入该数据输入;以及,写入该掩码包括:响应于该第一时钟周期的第二边沿写入该掩码。

18.在一些实施例中,该第一多行存储单元的行和该第二多行存储单元的行彼此相邻。

19.在一些实施例中,写入该数据输入包括:利用第一总线写入该数据输入;以及,写入该掩码扩:利用第二总线写入该掩码。

20.在一些实施例中,该方法还包括:利用该第一总线在该第一多行存储单元中中查找关键词。

21.在一些实施例中,该方法还包括:利用该第二总线在查找操作的期间掩码该tcam的一个或多个列。

22.在一些实施例中,写入该数据输入包括:响应于该第一时钟周期的第一边沿写入该数据输入,以及,写入该掩码包括:在该第一边沿的预定时间间隔后写入该掩码。

23.本发明内容是通过示例的方式提供的,并非旨在限定本发明。在下面的详细描述中描述其它实施例和优点。本领域技术人员在阅读附图所示优选实施例的下述详细描述之后,可以毫无疑义地理解本发明的这些目的及其它目的。详细的描述将参考附图在下面的实施例中给出。

附图说明

24.通过阅读后续的详细描述以及参考附图所给的示例,可以更全面地理解本发明,其中:

25.图1a是根据一些实施例示出的一种三态内容可寻址存储器(tcam)的方框示意图。

26.图1b是根据一些实施例的示意表,其可用于确定图1a的tcam的状态。

27.图2a是根据一些实施例示出的tcam架构的方框示意图。

28.图2b是根据一些实施例示出的说明图2a的tcam架构的非限制性实现的方框示意图。

29.图2c是根据一些实施例说明结合图2a的tcam架构使用的控制信号的示意图。

30.图3a是根据一些实施例说明另一tcam架构的方框示意图。

31.图3b是根据一些实施例说明图3a的tcam架构的非限制性实现的方框示意图。

32.图3c是根据一些实施例说明结合图3a的tcam架构使用的控制信号的示意图。

33.图4a是根据一些实施例说明耦接到解码器的tcam阵列的方框示意图。

34.图4b是根据一些实施例说明结合图4a的tcam使用的控制信号的示意图。

35.在下面的详细描述中,为了说明的目的,阐述了许多具体细节,以便本领域技术人员能够更透彻地理解本发明实施例。然而,显而易见的是,可以在没有这些具体细节的情况下实施一个或多个实施例,不同的实施例可根据需求相结合,而并不应当仅限于附图所列举的实施例。

具体实施方式

36.以下描述为本发明实施的较佳实施例,其仅用来例举阐释本发明的技术特征,而并非用来限制本发明的范畴。在通篇说明书及权利要求书当中使用了某些词汇来指称特定的元件,所属领域技术人员应当理解,制造商可能会使用不同的名称来称呼同样的元件。因此,本说明书及权利要求书并不以名称的差异作为区别元件的方式,而是以元件在功能上的差异作为区别的基准。本发明中使用的术语“元件”、“系统”和“装置”可以是与计算机相关的实体,其中,该计算机可以是硬件、软件、或硬件和软件的结合。在以下描述和权利要求书当中所提及的术语“包含”和“包括”为开放式用语,故应解释成“包含,但不限定于

…”

的意思。此外,术语“耦接”意指间接或直接的电气连接。因此,若文中描述一个装置耦接于另一装置,则代表该装置可直接电气连接于该另一装置,或者透过其它装置或连接手段间接地电气连接至该另一装置。

37.其中,除非另有指示,各附图的不同附图中对应的数字和符号通常涉及相应的部分。所绘制的附图清楚地说明了实施例的相关部分且并不一定是按比例绘制。

38.文中所用术语“基本”或“大致”是指在可接受的范围内,本领域技术人员能够解决所要解决的技术问题,基本达到所要达到的技术效果。举例而言,“大致等于”是指在不影响结果正确性时,技术人员能够接受的与“完全等于”有一定误差的方式。

39.随着诸如人工智能、数据库和网络交换之类的现代应用驱动对网络带宽的不断增加的需求,对高速存储器的需求不断增加,特别地,对高速tcam的需求增加。tcam的架构使其特别适用于计算机网络设备,例如,交换机和路由器。虽然近年来tcam的运行速度有了显著提高,但仍然不足以满足某些网络应用的要求。

40.申请人认识到,在tcam处增加执行写入操作(write operation)的速度将显著增强这些类型的存储器的适用性。因此,本发明提出了一种tcam架构,其被设计为提高(increase)写入操作的速度。本发明提出的tcam架构被设计为在单个的时钟周期(single clock cycle)中执行写入操作,该写入操作包括数据(data)写入和掩码(mask)写入。在一些实施例中,例如,在时钟周期的第一部分的期间,数据输入(data input)被写入到tcam条目(entry)的数据行(data row)中,以及,在同一时钟周期的第二部分的期间,掩码被写入

到tcam条目的掩码行(mask row)中。

41.本发明的一些实施例涉及一种tcam架构,在该架构中,第一总线同时用于数据写入(data write)和关键词查找(key search)的操作,以及,第二总线同时用于掩码写入(mask write)和查找掩码(search masking)的操作。在写入操作的期间,第一总线将数据输入传送到tcam条目的数据行(data row),以及,在该相同时钟周期的期间,第二总线将掩码(称为“局部掩码(local mask)”)传送到tcam条目的相应掩码行(mask row)。在查找操作的期间,第一总线将要被查找的关键词(key)传送至tcam,以及,第二总线传送用于掩码该关键词查找的位(这些位称为“列掩码(column mask)”)。对关键词查找进行掩码涉及结果返回(以匹配或不匹配的形式),其独立于被掩码的列(column)的值。例如,当掩码的特定位被断言(asserted)时,tcam的相应列被掩码,这意味着无论该特定列是否产生匹配,存储器都能够返回匹配结果。

42.可选地,其它的配置也是可行的,例如,第一总线用于数据写入和查找掩码操作,以及,第二总线用于掩码写入和关键词查找操作。具体地,本发明不做限制。

43.其它实施例涉及一种tcam架构,在该tcam架构中,第一总线用于数据写入和关键词查找操作,第二总线用于掩码写入操作,以及,第三总线用于查找掩码操作。在写入操作的期间,第一总线将数据输入传送到tcam条目的数据行,以及,在该相同时钟周期的期间,第二总线将掩码(被称为“局部掩码”)传送到tcam条目的相应掩码行。在查找操作的期间,第一总线将要被查找的关键词传送到tcam,以及,第三总线传送用于掩码关键词查找的位(这些位可以称为“列掩码(column mask)”)。其它配置也是可行的。例如,可以利用第二总线代替第一总线进行关键词查找操作。

44.图1a根据一些实施例示出了tcam。tcam包括按行(row)和列(column)排列的存储单元阵列。每个单元包括静态随机存取存储器(static random access memory,sram),替代地或附加地,可以使用其它类型的存储器。tcam具有多个列(0、1、2、3、

…

、n-1、n)和多个行(0、1

…

、2

m-1

)。每行包括一对子行(其包括第一子行和第二子行)。第一子行(“数据行(data row)”)用于存储数据,以及,第二子行(“掩码行(mask row)”)用于存储掩码。数据位(data bit)由字母“x”标识,以及,掩码位(mask bit)由字母“y”标识。公共(common)tcam条目的数据行和掩码行在tcam中彼此相邻。例如,对于第一tcam条目,其包括第一数据行(如数据行0)和与第一资料行相邻的第一掩码行(掩码行0),第二tcam条目包括第二数据行(如数据行1)和与第二资料行相邻的第二掩码行(掩码行1)。在一些实施例中,公共tcam条目(common tcam entry)的资料行和掩码行共享公共的(common)存储器地址,从而将寻址整个存储器所需的位数量减少了一个单位。例如,单个tcam条目的数据行和与该数据行相对应的掩码行共享公共的存储器地址,举例来说,该公共的存储器地址可指向该tcam条目中的数据行,以及,在该公共的存储器地址的基础上偏移预设量的地址可指向该tcam条目中的相应掩码行。

45.每个局部掩码包含多个位。每个局部掩码位的值决定了相应的数据位是否被掩码。根据一些实施例,局部掩码操作的代表性逻辑在图1b的表中示出。在本示例中,当资料被设置为1且局部掩码被设置为0时,特定位的状态为1。相反,当数据被设置为0且局部掩码被设置为1时,特定位的状态为0。当该局部掩码和数据都被设置为1时,对应数据位的状态为“不关心(don't care)”。最后,局部掩码和数据都被设置为0的组合是不受支持的。应当

理解,除图1b中描绘的逻辑之外的其他逻辑也可以被使用,因为位掩码不限于任何特定的逻辑。

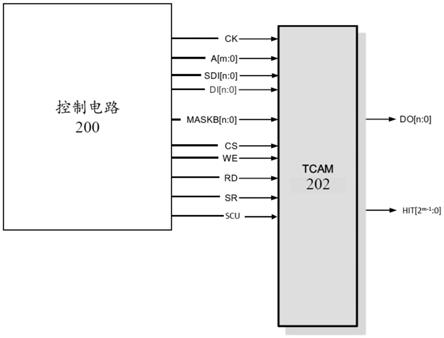

46.图2a是根据一些实施例示出的tcam架构的方框示意图。该架构包括控制电路200和tcam 202。tcam 202可以根据图1a中所示的示意图来布置。该架构旨在提高相对于先前实现的写入tcam操作的速度。更具体地说,该架构旨在在单个的时钟周期中写入数据输入和局部掩码。例如,在同一个时钟周期中,数据输入可以被写入至资料行0,以及,局部掩码被写入至掩码行0。tcam的总线被设置为支持单个时钟周期中的数据输入和掩码的写入操作。如图2a所示,控制电路200使用以下总线与tcam 202进行通信:clk、a、sdi、di、maskb、cs、we、rd、sr和scu。

47.控制电路200经由总线clk向tcam 202提供时钟(clock)。总线a(memory address,存储器地址)被用来提供用于写入和读取操作的地址。例如,在写入操作的期间,如果总线a指示第5行,则对第5行执行写入操作。类似地,在读取操作的期间,如果总线a指示第5行,则tcam返回第5行的内容。

48.总线sdi用于写入和查找操作这两者。在写入操作的期间,总线di携带要被写入至总线a标识的数据行的数据输入,以及,总线sdi携带要被写入至总线a标识的掩码行的局部掩码。在查找操作的期间,总线sdi携带要被在整个tcam中查找的关键词。

49.总线maskb用在查找操作的期间。特别地,总线maskb包括列掩码位(column mask bits),其标识在查找期间要被掩码的那些列以及不被掩码的那些列。

50.总线scu(single cyle update,单周期更新)用于启用(enable)单时钟周期操作,例如,当scu设置为1时,存储器以单时钟周期模式进行操作(可以理解地,相反的逻辑也是可行的)。总线cs(chip select,芯片选择)被用来从一组多个tcam芯片中选择特定的tcam芯片。当其设置为1时,总线cs启用在特定tcam芯片上的操作(可以理解地,相反的逻辑也是可能的)。总线we(memory write,存储器写入)用于启用写入操作(在一些实施例中,具有相对于scu的相反值)。例如,当we为0时,单时钟周期写入操作被启用,当we为1时,单时钟周期写入操作被禁用(相反的逻辑也是可行的,具体地,本发明对此不做限制)。总线sr被用来启用查找操作。例如,当sr为1时,启用查找操作,当sr为0时,禁用查找操作(相反的逻辑也是可行的,本发明对此不做限制)。总线rd用于启用读取操作。例如,当rd为1时,读取操作被启用,当rd为0时,读取操作被禁用(相反的逻辑也是可行的,本发明对此不做限制)。

51.输出总线do用于在读取操作的期间返回总线a标识的行的内容。输出总线hit用于在查找操作的期间返回已识别出匹配项的行的地址。

52.图2b根据一些实施例示出了tcam 202的非限制性实现的示意图。在该实施方式中,tcam 202包括触发器(flip-flop)250(如di输入锁存器)、252(如sdi输入触发器)和254(如maskb输入锁存器)、逻辑单元(logic unit)256和258、多工器(multiplexer)260和262、控制单元264和tcam列270(特别地,tcam阵列中的其中一列),其包括如图1a所示布置的sram(或其它类型的存储器)。tcam 202通过总线di、sdi、maskb、clk、we、scu和a(如结合图2a所讨论的)接收信号。

53.触发器250接收总线di的信号(例如,数据,图中示意为“data(x-word)”)作为输入,触发器252接收总线sdi的信号(例如,掩码,图中示意为“mask(y-word)”)作为输入,以及,触发器254接收总线maskb的信号(例如,在查找操作(during search)期间的全局掩码

(global mask))作为输入。时钟clk定时(time)触发器的操作。触发器250的输出作为输入分别提供给多工器260和262。触发器252的输出作为输入分别提供给逻辑单元256和258。逻辑单元的状态由触发器254的输出控制。总线scu的信号指示是否要进行单时钟写入操作(single-clock write operation),从而,在指示单时钟写入操作的情形中(例如,如果总线scu被断言),在同一时钟周期中写入数据输入和掩码这两者。然而,如果总线scu未被断言,则根据常规方案执行写入操作,从而,在单独的时钟周期中写入数据输入和相应的掩码。在这种情况下,scu启用多工器260和262。总线a的信号指示将被写入或读取的tcam条目的地址。对于常规写入,当we为1时,多工器260和262在整个时钟周期间选择di总在线的数据(多工器上的输入s1被选择)。在单时钟周期写入的过程中,多工器上的enb信号在同一时钟周期中根据定时信号切换,从而在相同周期内选择s1或s2作为多工器上的输入。逻辑单元256和258仅在查找操作的期间被使用。在写入操作的期间,逻辑单元256和258馈通触发器252的输出。总线maskb用于在查找操作的期间掩码特定列上的数据。

54.图2c根据一些实施例示出了代表写入操作的序列。该图示出了总线clk、scu(single cyle update,单周期更新)、cs(chip select,芯片选择)、we(memory write,存储器写入)、a(memory address,存储器地址)、di、sdi和maskb的信号之间的关系。当信号cs设置为1时,信号cs表示该tcam芯片已被选中。当信号scu设置为1且信号we设置为0时,将执行单时钟写入。相反,当信号scu设置为0且信号we设置为1时,将执行多时钟写入。

55.信号a提供将被写入的行的地址(图中标注为“tcam address”)。在本示例中,地址(以十六进制表示)为“000”。信号di的内容代表将被写入至寻址tcam数据行的数据输入(图中标注为“data/x”)。在这个例子中,di的内容是“aaaaa”。信号sdi的内容代表将被写入至寻址tcam掩码行的掩码(图中标注为“mask/y”)。在本示例中,sdi的内容为“55555”。在这个序列中,di的内容和sdi的内容都是在同一个时钟周期中写入的(即单时钟写入)。在写入操作的期间,不考虑信号maskb(本示例中为“fffff”)的内容。

56.图3a是根据一些实施例说明另一tcam架构的方框示意图。类似于图2a的架构,该架构还设计为在单个时钟周期中写入数据输入和掩码。然而,该架构比图2a的架构涉及更少的总线,从而降低了电路复杂度。

57.该架构包括控制电路300和tcam 302。tcam 302可以根据图1a中所示的示意图进行布置。tcam的总线被安排为支持单个时钟周期中的数据输入和掩码的写入操作。如图3a所示,控制电路300使用以下总线与tcam 302通信:clk、a、sdi、maskb、cs、we、rd、scu和sr。应该注意的是,与图2a的例子不同,该架构不包括总线di。在这种架构中,总线sdi和maskb都具有双重功能(dual function)。在单时钟周期写入操作的期间,总线sdi携带(carry)将被写入的数据输入,以及,maskb携带将被写入的局部掩码。在查找操作的期间,总线sdi携带要被查找的关键词,而maskb携带列掩码位,其标识哪些列将被掩码(可选地,总线maskb可以携带要被查找的关键词,以及,sdi携带标识哪些列被掩码的掩码位,具体地,本发明不做限制)。本质上,sdi和maskb都被以时分复用方式使用。总线clk、a、cs、we、rd、scu和sr具有如图2a描述的相同功能。输出总线do和hit也具有如图2a描述的相同功能。

58.图3b根据一些实施例示出了tcam 302的非限制性实现的示意图。在该实施方式中,tcam 302包括触发器350、352和354、逻辑单元346、348、356和358、多工器360和362、控制单元364和tcam列370。例如,tcam阵列370可以包括如图1a所示排列的sram(或其它类型

的存储器)。tcam 302通过总线sdi、maskb、clk、we、scu和a(如结合图3a所讨论的)接收信号。

59.逻辑单元346接收总线sdi的信号作为输入,以及,逻辑单元348接收总线maskb的信号作为输入。总线scu的信号指示是否在单个时钟周期中执行包括写入数据输入和掩码的写入操作。在此示例中,scu控制逻辑单元346和348的状态。

60.触发器350接收总线sdi的信号作为输入,触发器352接收逻辑单元346的输出作为输入,以及,触发器354接收逻辑单元348的输出作为输入。时钟clk定时(time)触发器的操作。触发器350的输出分别提供给多工器360和362作为输入。触发器352的输出分别提供给逻辑单元356和358作为输入。逻辑单元356和358的状态由触发器354的输出控制。总线a的信号指示将被写入或读取的tcam的行的地址。在写入操作的期间,总线we的信号被断言(asserted),这使得多工器360和362能够用于写入操作。在写入操作的期间,控制单元364使能写入至tcam阵列370,以及,触发器的输出通过晶体管366和368写入至tcam阵列。总线a的信号确定将被写入的行的地址。在查找操作的期间,逻辑单元356和358根据maskb的相应掩码位的值掩码特定行的查找。

61.图3c根据一些实施例说明与图3a的架构有关的代表写入操作的序列。该图说明了总线clk、scu、we、a、sdi和maskb的信号之间的关系。当scu设置为1,cs设置为1,以及,we设置为0时,将在该tcam芯片中执行单时钟周期的写入操作。

62.信号a提供将被写入的行的地址。信号sdi的内容表示将被写入至寻址tcam数据行的数据输入。信号maskb的内容表示将被写入至寻址tcam掩码行的局部掩码。在这个序列中,sdi的内容和maskb的内容都在单个的时钟周期中被写入。

63.如上所述,根据本技术,可以使用不同的架构来实现tcam。不管使用的具体架构如何,这里描述的tcam被配置为在相同的时钟周期中执行数据写入和掩码写入。在一些实施例中,在时钟周期的第一部分中执行数据写入,以及,在相同时钟周期的第二部分中执行掩码写入(可以理解地,相反的顺序也是可行的,本发明对此不做任何限制)。例如,数据写入可由时钟周期的第一边沿(上升沿或下降沿)触发,而掩码写入可由相同时钟周期的第二边沿触发。在一些实施例中,解码器被用来以这种方式启用写入操作。

64.图4a根据一些实施例描绘了示例性的解码器。在该示例中,tcam阵列如图1a所讨论的那样布置。每行(无论是数据行还是掩码行)都耦接到输入寄存器(图中标记为“wldrv”)。控制信号xpz_en_even和xpz_en_odd用于控制寄存器将其各自内容传送到tcam的行的时序。解码器(图中标记为“xdecoder”),用于选择将被更新的tcam条目。根据地址总线a的值,选择适当的wldrv,然后,根据xpz_en_odd或xpz_en_even的状态,使用该wldrv启用奇数或偶数wl总线。在输入总线sdi和maskb中接收到的数据通过信号bl/blb发送。根据一些实施例,这些控制信号的例子示于图4b中。在这个例子中,控制信号xpz_en_even和xpz_en_odd具有与时钟clk相同的频率。此外,控制信号xpz_en_even和xpz_en_odd相对于彼此是相位偏移的(phase-shifted)。控制信号xpz_en_even的边沿(例如,上升沿)触发数据写入至特定数据行。类似地,控制信号xpz_en_odd的边沿(例如,紧跟在xpz_en_even的触发上升沿之后的上升沿)触发局部掩码写入至相应的(例如,相邻)掩码行。

65.在权利要求书中使用诸如“第一”,“第二”,“第三”等序数术语来修改专利要素,其本身并不表示一个专利要素相对于另一个专利要素的任何优先权、优先级或顺序,或执行

方法动作的时间顺序,但仅用作标记,以使用序数词来区分具有相同名称的一个申请专利要素与具有相同名称的另一个元素要素。

66.虽然本发明已经通过示例的方式以及依据优选实施例进行了描述,但是,应当理解的是,本发明并不限于公开的实施例。相反,它旨在覆盖各种变型和类似的结构(如对于本领域技术人员将是显而易见的),例如,不同实施例中的不同特征的组合或替换。因此,所附权利要求的范围应被赋予最宽的解释,以涵盖所有的这些变型和类似的结构。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1