半导体装置用基板的制作方法

1.本发明涉及半导体装置用基板。

背景技术:

2.作为用于功率晶体管模块等的半导体装置用基板,已知在陶瓷烧结体的表背面具备电路板的dboc基板(direct bonding of copper substrate,直接覆铜基板)、在陶瓷烧结体的表背面具备铝板的dboa基板(direct bonding of aluminum substrate,直接覆铜铝板)。

3.在专利文献1中,公开了具备包含氧化铝、部分稳定化氧化锆和氧化镁的陶瓷烧结体的半导体装置用基板。在专利文献1记载的陶瓷烧结体中,部分稳定化氧化锆的含量为1~30wt%,氧化镁的含量为0.05~0.50wt%,部分稳定化氧化锆中的三氧化二钇的摩尔分数为0.015~0.035,陶瓷烧结体中包含的氧化锆晶体之中的80~100%为正方晶相。根据专利文献1记载的陶瓷烧结体,能够抑制在陶瓷烧结体与电路板或铝板的接合界面产生裂纹,并且能够使热传导率提高。

4.在专利文献2中公开了具备包含氧化铝、氧化锆和三氧化二钇的陶瓷烧结体的半导体装置用基板。在专利文献2记载的陶瓷烧结体中,氧化锆的含量为2~15重量%,氧化铝的平均粒径为2~8μm。根据专利文献2记载的陶瓷烧结体,能够使热传导率提高。在先技术文献专利文献

5.专利文献1:日本专利4717960号公报专利文献2:日本特表2015-534280号公报

技术实现要素:

发明要解决的课题

6.但是,在专利文献1中,虽然对于陶瓷烧结体单体下的热传导率进行了研究,但是对于作为包含电路板(电路板或铝板)的半导体装置用基板整体的热电阻率没有进行研究。

7.同样地,在专利文献2中,对于作为半导体装置用基板整体的热电阻率没有进行研究,此外,对于接合界面处的裂纹也没有进行研究。

8.因此,本发明的发明者进行了潜心研究,结果得到了如下新的见解,即,陶瓷烧结体的组成和各结构构件的厚度的组合对半导体装置用基板的热电阻率以及接合界面处的裂纹产生影响。

9.本发明的目的在于,提供一种能够兼顾热电阻率的降低和裂纹的抑制的半导体装置用基板。用于解决课题的手段

10.本发明涉及的半导体装置用基板具备陶瓷烧结体、第1电路板和第2电路板。陶瓷烧结体形成为板状,具有第1主面和第2主面。第1电路板配置在第1主面上,由铜或铝构成。

第2电路板配置在第2主面上,由铜或铝构成。陶瓷烧结体包含al、zr、y以及mg。在陶瓷烧结体中,将mg的以mgo换算的含量设为s1质量%,并将zr的以zro2换算的含量设为s2质量%的情况下,下述的式(1)成立。将第1电路板的厚度设为t1mm,将第2电路板的厚度设为t2mm,并将陶瓷烧结体的厚度设为t3mm的情况下,下述的式(2)、(3)、(4)成立。

11.-0.004

×

s2+0.171<s1<-0.032

×

s2+1.427

···

(1)1.7<(t1+t2)/t3<3.5

···

(2)t1≥t2

···

(3)t3≥0.25

···

(4)发明效果

12.根据本发明,能够提供一种能兼顾热电阻率的降低和裂纹的抑制的半导体装置用基板。

附图说明

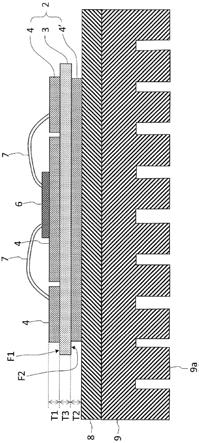

13.图1是示出实施方式涉及的半导体装置的结构的立体图。图2是图1的a-a剖视图。图3是用于说明实施方式涉及的半导体装置用基板的制造方法的流程图。

具体实施方式

14.以下,参照附图对本发明涉及的半导体装置的结构进行说明。

15.(半导体装置1的结构)图1是实施方式涉及的半导体装置1的剖视图。图2是图1的a-a剖视图。

16.半导体装置1在汽车、空调机、工业用机器人、商用电梯、家庭用微波炉、ih电饭煲、发电(风力发电、太阳光发电、燃料电池等)、电力铁道、ups(不间断电源)等各种各样的电子设备中用作功率模块。

17.半导体装置1具备半导体装置用基板2、半导体芯片6、接合线7、散热器8以及散热部9。

18.半导体装置用基板2是所谓的dboc基板(direct bonding of copper substrate,直接覆铜基板)或dboa基板(direct bonding of aluminum substrate,直接覆铝基板)。

19.半导体装置用基板2的尺寸以及平面形状没有特别限制,例如,可以设为纵向长度p1为25~40mm、横向长度q1为35~50mm的正方形或长方形。关于构成半导体装置用基板2的各结构构件的厚度在后面叙述。

20.半导体装置用基板2具备陶瓷烧结体3、第1电路板4以及第2电路板4’。

21.陶瓷烧结体3是半导体装置用基板2用的绝缘体。陶瓷烧结体3形成为平板状。陶瓷烧结体3具有第1主面f1和第1主面的相反侧的第2主面f2。关于陶瓷烧结体3的构成元素在后面叙述。

22.第1电路板4配置在陶瓷烧结体3的第1主面f1上。第1电路板4由铜或铝构成。第1电路板4形成为平板状。第1电路板4与陶瓷烧结体3的第1主面f1直接接合。本实施方式涉及的第1电路板4由3片板构件构成,由此形成了输电电路。不过,第1电路板4的平面形状没有特别限制,只要由多个板构件形成希望的输电电路即可。

23.第1电路板4对第1主面f1的被覆率没有特别限制,例如可以设为85%以上且95%以下。第1电路板4对第1主面f1的被覆率在第1主面f1的俯视下通过将第1电路板4的合计面积除以第1主面f1的总面积而求出。

24.第2电路板4’配置在陶瓷烧结体3的第2主面f2上。第2电路板4’由铜或铝构成。第2电路板4’形成为平板状。第2电路板4’与陶瓷烧结体3的第2主面f2直接接合。第2电路板4’是单一的板构件。

25.第2电路板4’对第2主面f2的被覆率没有特别限制,例如可以设为90%以上且96%以下。第2电路板4’对第2主面f2的被覆率在半导体装置用基板2的俯视下通过将第2电路板4’的总面积除以第2主面f2的总面积而求出。第2电路板4’对第2主面f2的被覆率既可以与第1电路板4对第1主面f1的被覆率同样,也可以大于第1电路板4对第1主面f1的被覆率。第2电路板4’的总面积既可以与第1电路板4的总面积同样,也可以大于第1电路板4的总面积。

26.半导体装置用基板2的制作方法没有特别限制,例如可以如下这样制作。首先,形成在陶瓷烧结体3的第1主面f1侧配置了第1电路板4并在陶瓷烧结体3的第2主面f2侧配置了第2电路板4’的层叠体。接着,将层叠体在1070℃~1075℃的氮气氛条件下加热10分钟程度。由此,在陶瓷烧结体3和第1以及第2电路板4、4’接合的界面(以下,总称为“接合界面”。)生成cu-o共晶液相,陶瓷烧结体3的第1以及第2主面f1、f2润湿。接着,通过将层叠体冷却从而cu-o共晶液相被固化,第1以及第2电路板4、4’接合于陶瓷烧结体3。

27.另外,在半导体装置用基板2中,形成了输电电路的第1铜板4与陶瓷烧结体3的表面接合,但输电电路也可以通过减成法或加成法而形成。

28.半导体芯片6与第1电路板4接合。接合线7将半导体芯片6与第1电路板4连接。

29.散热器8与第2电路板4’接合。散热器8吸收经由半导体装置用基板2而传递的半导体芯片6的热。散热器8例如可以由铜等构成。散热器8的尺寸以及形状没有特别限制。

30.散热部9安装于散热器8。散热部9将经由半导体装置用基板2以及散热器8而传递的半导体芯片6的热散热到外部空气中。散热部9例如可以由铝等构成。散热部9的尺寸以及形状没有特别限制。散热部9优选具有多个鳍片部9a。由此,能够使散热部9的散热效率提高。

31.散热器8以及散热部9的平面尺寸以及平面形状没有特别限制,例如,可以设为纵向长度p2为25~40mm、横向长度q2为35~50mm的正方形或长方形。

32.(陶瓷烧结体3的构成元素)陶瓷烧结体3包含al(铝)、zr(锆)、y(钇)和mg(镁)。

33.陶瓷烧结体3中的al的含量以al2o3换算可以设为75质量%以上且92.5质量%以下。陶瓷烧结体3中的al的含量以al2o3换算优选为75质量%以上且85质量%以下。

34.陶瓷烧结体3中的zr的含量(后述的s2)以zro2换算可以设为5%以上且27.5质量%以下,以zro2换算优选为7.5质量%以上且25质量%以下,以zro2换算更优选为17.5质量%以上且23.5质量%以下。

35.可以认为,通过将zr的含量以zro2换算设为7.5质量%以上,从而能够抑制陶瓷烧结体3的线热膨胀系数α变得过小,能够减小陶瓷烧结体3与第1以及第2电路板4、4’的线热膨胀系数差。可以认为,其结果是,能够减小在接合界面产生的热应力,有助于抑制在接合界面产生裂纹。通过将zr的含量以zro2换算设为17.5质量%以上,能够使该效果进一步提

高。

36.可以认为,通过将zr的含量以zro2换算设为25质量%以下,从而能够抑制电路板接合时的接合界面处的反应变得过剩,能够抑制在接合界面产生空隙。可以认为,其结果是,有助于抑制在接合界面产生裂纹。通过将zr的含量以zro2换算设为23.5质量%以下,能够使该效果进一步提高。

37.陶瓷烧结体3中的y的含量以y2o3换算可以设为0.3质量%以上且2.0质量%以下。陶瓷烧结体3中的y的含量以y2o3换算优选为0.7质量%以上且2.0质量%以下。

38.可以认为,通过将y的含量以y2o3换算设为0.3质量%以上,从而能够抑制陶瓷烧结体3作为晶相而包含的zro2晶相中的单斜晶相的峰值强度比变得过大。可以认为,其结果是,能够提高陶瓷烧结体3的机械强度,有助于抑制在接合界面产生裂纹。

39.可以认为,通过将y的含量以y2o3换算设为2.0质量%以下,从而能够抑制陶瓷烧结体3作为晶相而包含的zro2晶相中的单斜晶相的峰值强度比变得过小。可以认为,其结果是,能够提高陶瓷烧结体3的机械强度,有助于抑制在接合界面产生裂纹。

40.陶瓷烧结体3中的mg的含量(后述的s1)以mgo换算可以设为大于0.08质量%且小于1.18质量%。

41.可以认为,通过使mg的含量以mgo换算大于0.08质量%,从而即使不过度地提高烧成温度也能使陶瓷烧结体3烧结,能够抑制al2o3粒子以及zro2粒子的粗大化。可以认为,其结果是,能够提高陶瓷烧结体3的机械强度,有助于抑制在接合界面产生裂纹。此外,可以认为能够在陶瓷烧结体3中生成充分的量的mgal2o4(尖晶石)晶体,能够使电路板接合时的与cu-o共晶液相的润湿性提高。可以认为,其结果是,有助于抑制在接合界面产生空隙。

42.可以认为,通过使mg的含量以mgo换算小于1.18质量%,从而能够抑制氧化铝以及氧化锆晶体的过剩的生长,能够提高陶瓷烧结体3的机械强度。可以认为,其结果是,有助于抑制在接合界面产生裂纹。此外,可以认为,能够抑制在陶瓷烧结体3中过剩地生成mgal2o4晶体,能够抑制电路板接合时的接合界面处的反应变得过剩。可以认为,其结果是,有助于抑制在接合界面产生空隙。

43.陶瓷烧结体3也可以包含hf(铪)、si(硅)、ca(钙)、na(钠)以及k(钾)的至少一方和除它们以外的剩余部分。剩余部分中包含的元素既可以是有意地添加的元素,也可以是不可避免地混入的元素。剩余部分中包含的元素没有特别限制,例如,可以列举fe(铁)、ti(钛)、mn(锰)等。

44.在本实施方式中,陶瓷烧结体3的构成元素的含量如上述那样以氧化物换算而算出,但陶瓷烧结体3的构成元素既可以以氧化物的形态存在,也可以不以氧化物的形态存在。例如,y、mg以及ca中的至少1种也可以不以氧化物的形态存在,而固溶于zro2中。

45.陶瓷烧结体3的构成元素的以氧化物换算的含量如以下这样算出。首先,利用荧光x射线分析装置(xrf)或者附设于扫描型电子显微镜(sem)的能量分散型分析器(eds),对陶瓷烧结体3的构成元素进行定性分析。接着,针对通过该定性分析而检测出的各元素,利用icp发光分光分析装置进行定量分析。接着,将通过该定量分析而测定出的各元素的含量换算为氧化物。

46.(陶瓷烧结体3的组成和各结构构件的厚度)接着,对陶瓷烧结体3的组成和陶瓷烧结体3、第1电路板4以及第2电路板4’各自的

厚度的组合进行说明。

47.将陶瓷烧结体3中的mg的以mgo换算的含量设为s1质量%、且将zr的以zro2换算的含量设为s2质量%的情况下,下述的式(1)成立。

48.-0.004

×

s2+0.171<s1<-0.032

×

s2+1.427

···

(1)

49.将第1电路板的厚度设为t1mm,将第2电路板的厚度设为t2mm,将所述陶瓷烧结体的厚度设为t3mm的情况下,下述的式(2)、(3)、(4)成立。

50.1.7<(t1+t2)/t3<3.5

···

(2)t1≥t2

···

(3)t3≥0.25

···

(4)

51.通过以上的式(1)~(4)成立,从而即使对陶瓷烧结体3施加了热循环也能够抑制在接合界面产生裂纹,并且能够使作为半导体装置用基板2整体的热电阻率降低。能得到这样的效果的机制虽然未必明确,但可以认为是通过满足式(1)、式(2)的上限值以及式(4)从而陶瓷烧结体3的机械强度提高、和通过式(2)的下限值以及式(3)成立从而热传导率低的陶瓷烧结体3与热传导率高的第1以及第2电路板4、4’的相对厚度被最优化的协同效应。

52.如式(3)所示,第1电路板的厚度t1mm既可以与第2电路板的厚度t2mm相同,也可以大于第2电路板的厚度t2mm。不过,在第2电路板4’的总面积大于第1电路板4的总面积的情况下,有可能在电路板接合时陶瓷烧结体3朝向第2电路板4’侧变形为凹状。因此,在第2电路板4’的总面积大于第1电路板4的总面积的情况下,第1电路板的厚度t1mm优选大于第2电路板的厚度t2mm。

53.关于陶瓷烧结体3中的zr的以zro2换算的含量s2,优选下述的式(5)成立。

54.7.5≤s2≤25

···

(5)

55.通过式(5)成立,从而如上述那样,能够进一步提高陶瓷烧结体3的机械强度,因此能够进一步抑制在接合界面产生裂纹。

56.关于陶瓷烧结体3中的zr的以zro2换算的含量s2,更优选下述的式(6)成立。

57.17.5≤s2≤23.5

···

(6)

58.通过式(6)成立,从而能够进一步提高陶瓷烧结体3的机械强度,能够进一步抑制在接合界面产生裂纹。

59.关于陶瓷烧结体3中的mg的以mgo换算的含量s1,更优选下述的式(7)成立。

60.0.08<s1<1.18

···

(7)

61.通过式(7)成立,从而如上述那样,能够进一步提高陶瓷烧结体3的机械强度,因此能够进一步抑制在接合界面产生裂纹。

62.(陶瓷烧结体3的制造方法)参照图2对陶瓷烧结体3的制造方法进行说明。图2是示出陶瓷烧结体3的制造方法的流程图。

63.在步骤s1中,除了al2o3、zro2、y2o3以及mgo之外,还根据希望而调配hfo2、sio2、cao、na2o以及k2o等粉体材料。

64.另外,zro2以及y2o3各自可以为单独的粉体材料,但也可以使用以y2o3部分稳定化的zro2的粉体材料。此外,mg、ca、以及碱金属(na以及k)可以为碳酸盐粉体。

65.在步骤s2中,将调配后的粉体材料例如通过球磨机等进行粉碎混合。

66.在步骤s3中,在粉碎混合后的粉体材料中添加有机质粘合剂(例如,聚乙烯醇缩丁醛)、溶剂(二甲苯、甲苯等)以及增塑剂(邻苯二甲酸二辛酯)而形成浆料状物质。

67.在步骤s4中,通过希望的成型手段(例如,模具压制、冷等静压、注塑成型、刮板法、挤压成型法等),将浆料状物质成型为希望的形状来制作陶瓷成型体。此时,考虑步骤s5中的烧成收缩率来调整陶瓷成型体的厚度,使得陶瓷烧结体3的厚度t3在与第1电路板的厚度t1以及第2电路板的厚度t2的关系中上述(2)~(4)成立。

68.在步骤s5中,将陶瓷成型体在氧气氛或大气气氛中进行烧成(150~1620℃,0.7~1.0小时)。实施例

69.作为样本no.1~72,制作具有图1以及图2所示的结构的半导体装置1,并测定了半导体装置1的热电阻和产生裂纹的热循环数。

70.(半导体装置1的制作)首先,调配al2o3、zro2、y2o3以及mgo的粉体材料,并利用球磨机进行了粉碎混合。此时,如表1所示按每个样本对zro2的含量s2和mgo的含量s1进行变更,其余设为al2o3。

71.接着,在粉碎混合后的粉体材料中添加作为有机质粘合剂的聚乙烯醇缩丁醛、作为溶剂的二甲苯、和作为增塑剂的邻苯二甲酸二辛酯而形成了浆料状物质。

72.接着,通过刮板法,将浆料状物质成型为片状而制作了陶瓷成型体。此时,通过变更刮板的浇口高度,从而按每个样本调整了陶瓷成型体的厚度,使得陶瓷烧结体3的厚度t3成为表1所示的值。

73.接着,将陶瓷成型体在大气气氛中进行烧成(1600℃,0.8小时)而制作了陶瓷烧结体3。陶瓷烧结体3的纵向长度p1为40mm,横向长度q1为40mm。

74.接着,准备由遵循jis c1020的无氧铜构成的第1电路板4(纵向长度37.4mm

×

横向长度19.8mm为1片,纵向长度37.4mm

×

横向长度7.8mm为2片)和第2电路板4’(纵向长度37.4mm

×

横向长度37.4mm为1片)。第1电路板4的厚度t1和第2电路板4’的厚度t2如表1所示按每个样本而不同。

75.接着,通过在大气中加热至300℃,从而使第1以及第2电路板4、4’各自的外表面氧化。

76.接着,将由第1以及第2电路板4、4’夹着陶瓷烧结体3的层叠体在氮(n2)气氛中以1070℃加热了10分钟。

77.接着,通过将层叠体冷却,从而将第1以及第2电路板4、4’接合于陶瓷烧结体3。第1电路板4对第1主面f1的被覆率为82.7%,第2电路板4’对第2主面f2的被覆率为87.4%。

78.接着,利用焊料,将安装了铝制的散热部9(纵向长度60mm

×

横向长度60mm

×

厚度6.5mm)的铜制的散热器8(纵向长度60mm

×

横向长度60mm

×

厚度3mm)接合于第2电路板4’。

79.接着,利用焊料,将si半导体芯片6接合于第1电路板4,并且在si半导体芯片6(纵向长度10mm

×

横向长度10mm

×

厚度0.35mm)和第1电路板4安装了接合线7。

80.(热电阻的测定)针对样本no.1~72,通过对si半导体芯片6通电使其发热,从而根据下述的式(8)测定了半导体装置1的热电阻r

j-a

(℃/w)。其中,在式(8)中,t

j

为si半导体芯片6的元件温度(℃),t

a

为si半导体芯片6的周围温度(℃),q为对si半导体芯片6供给的电力(w)。

81.r

j-a

=(t

j

-t

a

)/q

···

(8)

82.在表1中,针对样本no.1~72分别记载了10片热电阻率的平均值。在表1中,热电阻率(℃/w)为0.805以上的样本被评价为

“×”

,0.790以上且小于0.805的样本被评价为

“△”

,小于0.790的样本被评价为

“○”

。

83.(裂纹产生率)针对样本no.1~72,重复了“-40℃

×

30分钟

→

25℃

×

5分钟

→

125℃

×

30分钟

→

25℃

×

5分钟”的循环,直到在陶瓷烧结体3产生裂纹为止。

84.在表1中,针对样本no.1~72分别将在10片中的任意一片产生了裂纹的循环数记载为裂纹产生循环数。在表1中,裂纹产生循环数(次)为51以上的样本被评价为

“○”

,31以上且50以下的样本被评价为

“△”

,30以下的样本被评价为

“×”

。

85.[表1]

[0086]

如表1所示,在上述的式(1)~(4)全部成立的样本中,即使对陶瓷烧结体3施加了热循环也能够抑制在接合界面产生裂纹,并且能够使作为半导体装置用基板2整体的热电阻率降低。

[0087]

另一方面,在不满足式(1)的样本no.2、5、12、15、22、25、32、35、42、45、52、55、62、65中,由于陶瓷烧结体3的机械强度不充分,因此容易在接合界面产生裂纹。此外,在不满足式(2)的上限值的样本no.10、20、30、40、50、60、70中,陶瓷烧结体3的机械强度也不充分,因此也容易在接合界面产生裂纹。此外,在不满足式(2)的下限值的样本no.6、11、16、21、26、31、36、41、46、51、56、61、77、71中,热传导率低的陶瓷烧结体3与热传导率高的第1以及第2电路板4、4’的相对厚度未被最优化,因此作为半导体装置用基板2整体的热电阻率高。

[0088]

此外,对样本no.1和样本no.8、18进行比较可知,在上述的式(5)成立的样本中,能够进一步抑制在陶瓷烧结体3和第1以及第2电路板4、4’的接合界面产生裂纹。

[0089]

进而,在上述的式(6)成立的样本中,能够进一步抑制在陶瓷烧结体3与第1以及第2电路板4、4’的接合界面产生裂纹。另外,在将zr的以zro2换算的含量设为17.5质量%以上且23.5质量%以下的样本中尤其能够使该效果提高。工业实用性

[0090]

根据本发明,能够兼顾半导体装置用基板中的热电阻率的降低和裂纹的抑制,因此本发明涉及的半导体装置用基板能够在各种各样的电子设备中利用。符号说明

[0091]1…

半导体装置2

…

半导体装置用基板3

…

陶瓷烧结体4、4

’…

电路板6

…

半导体芯片7

…

接合线8

…

散热器9

…

散热部。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1