电子封装件的制作方法

[0001]

本发明有关一种封装结构,特别是一种散热型电子封装件。

背景技术:

[0002]

随着电子产品在功能及处理速度的需求的提升,作为电子产品的核心组件的半导体芯片需具有更高密度的电子电路(electronic circuits),故半导体芯片在运行时将随之产生更大量的热能。

[0003]

因此,为了迅速将热能散逸至外部,业界通常在半导体封装件中配置散热片(heat sink或heat spreader),该散热片通常经由散热胶,如导热界面材(thermal interface material,简称tim),结合至芯片背面,以借散热胶与散热片逸散出半导体芯片所产生的热量。

[0004]

如图1所示,现有半导体封装件1的制法先将一半导体芯片11以其作用面11a利用覆晶接合方式(即通过导电凸块110与底胶111)设在一封装基板10上,再将一散热件13以其顶片130经由tim层12(其包含焊锡层与助焊剂)回焊结合在该半导体芯片11的非作用面11b上,且该散热件13的支撑脚131通过粘着层14架设在该封装基板10上。接着,进行封装压模作业,以供封装胶体(图略)包覆该半导体芯片11及散热件13,并使该散热件13的顶片130外露出封装胶体。

[0005]

当运行时,该半导体芯片11所产生的热能经由该非作用面11b、tim层12而传导至该散热件13的顶片130以散热至该半导体封装件1的外部。

[0006]

但是,随着电子产品的功能增加,其所用的半导体封装件1中,该半导体芯片11的运行量也随之大增,致使该半导体芯片11所产生的热能大幅增加,故现有半导体封装件1中,该半导体芯片11的散热途径仅能经由其非作用面11b进行散热,因而难以满足散热需求,造成该半导体封装件1容易因过热而故障。

[0007]

因此,如何克服上述现有技术的问题,实已成为目前业界亟待克服的难题。

技术实现要素:

[0008]

鉴于上述现有技术的种种缺陷,本发明提供一种电子封装件,其经由将该第一散热层形成在该电子元件的侧面上,以大幅提升散热效果。

[0009]

本发明的电子封装件包括:电子元件,其具有相对的第一表面与第二表面及邻接该第一与第二表面的侧面;多个导电结构,其设在该电子元件的第一表面上;第一散热层,其接触形成在该电子元件的侧面上且经由绝缘体隔离所述多个导电结构;以及封装层,其包覆该电子元件、所述多个导电结构与该第一散热层,且令该导电结构外露出该封装层的表面。

[0010]

前述的电子封装件中,该电子元件的第二表面外露出该封装层的表面。

[0011]

前述的电子封装件中,该第一散热层还形成在该电子元件的第二表面上。

[0012]

前述的电子封装件中,该第一散热层具有凹凸表面。

[0013]

前述的电子封装件中,该第一散热层为金属层。

[0014]

前述的电子封装件中,还包括设置该电子元件的承载结构,其电性连接该导电结构。例如,该承载结构具有板体及设在该板体中的第三散热层。进一步包括设在该承载结构上的散热件,其连接该第三散热层。或者,可包括设在该承载结构上的散热件。例如,该散热件具有一散热体与设在该散热体上的支撑脚,以令该支撑脚结合在该承载结构上,使该散热体设在该承载结构上,且该散热体结合在该电子元件的第二表面上。进一步,该散热件具有凹凸部。

[0015]

前述的电子封装件中,还包括设置该电子元件的中介结构,其电性连接该导电结构。例如,该中介结构具有板体及设在该板体中的第二散热层或设在该板体上的散热柱。或者,还包括设置该中介结构的承载结构,其电性连接该中介结构。又包括设在该承载结构上的散热件。例如,该散热件其具有一散热体与设在该散热体上的支撑脚,以令该支撑脚结合在该承载结构上,使该散热体设在该承载结构上,且该散热体结合在该电子元件的第二表面上。进一步,该散热件具有凹凸部。

[0016]

由上可知,本发明的电子封装件主要经由将该第一散热层形成在该电子元件的侧面上,以将该电子元件所产生的热能经由该第一散热层散逸至外界,故相比于现有技术,本发明的电子封装件的散热途径包含该电子元件的第二表面及侧面,因而能大幅提升散热效果,以满足散热需求,且避免该电子封装件因过热而故障的问题。

附图说明

[0017]

图1为现有半导体封装件的剖视示意图。

[0018]

图2为本发明的电子封装件的剖视示意图。

[0019]

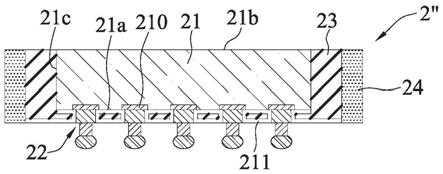

图2’及2”为本发明的电子封装件的其它实施例的剖视示意图。

[0020]

图2a、2b及2c为本发明的电子封装件的局部构成的不同实施例的剖视示意图。

[0021]

图3a为图2”的另一实施例。

[0022]

图3b为图3a的局部剖视示意图。

[0023]

图3b’为图3b的上视示意图

[0024]

图3c为图3a的局部剖视示意图。

[0025]

图3d为图3a的局部剖视示意图。

[0026]

图3d’为图3d的另一实施例的示意图。

[0027]

附图标记说明

[0028]1ꢀꢀꢀꢀꢀꢀꢀ

半导体封装件

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

10

ꢀꢀꢀꢀꢀꢀ

封装基板

[0029]

11

ꢀꢀꢀꢀꢀꢀ

半导体芯片

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

11a

ꢀꢀꢀꢀꢀ

作用面

[0030]

11b

ꢀꢀꢀꢀꢀ

非作用面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

110

ꢀꢀꢀꢀꢀ

导电凸块

[0031]

111

ꢀꢀꢀꢀꢀ

底胶

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

12

ꢀꢀꢀꢀꢀꢀ

tim层

[0032]

13

ꢀꢀꢀꢀꢀꢀ

散热件

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

130

ꢀꢀꢀꢀꢀ

顶片

[0033]

131

ꢀꢀꢀꢀꢀ

支撑脚

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

14

ꢀꢀꢀꢀꢀꢀ

粘着层

[0034]

2,2’,2”,3 电子封装件

ꢀꢀꢀꢀꢀꢀꢀ

2a

ꢀꢀꢀꢀꢀꢀ

多芯片封装体

[0035]

2b,3b

ꢀꢀꢀ

中介结构

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

2c,3c

ꢀꢀꢀ

承载结构

[0036]

2d,3d

ꢀꢀꢀ

散热件

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

21,21

’ꢀꢀ

电子元件

[0037]

21a

ꢀꢀꢀꢀꢀ

第一表面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

21b

ꢀꢀꢀꢀꢀ

第二表面

[0038]

21c

ꢀꢀꢀꢀꢀ

侧面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

210

ꢀꢀꢀꢀꢀ

电极垫

[0039]

211

ꢀꢀꢀꢀꢀ

绝缘体

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

22

ꢀꢀꢀꢀꢀꢀ

导电结构

[0040]

220,221,222 导电材

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

23,23’,23

”ꢀ

第一散热层

[0041]

23a

ꢀꢀꢀꢀꢀ

凹凸表面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

24

ꢀꢀꢀꢀꢀꢀ

封装层

[0042]

24a

ꢀꢀꢀꢀꢀ

第一侧

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

24b

ꢀꢀꢀꢀꢀ

第二侧

[0043]

25

ꢀꢀꢀꢀꢀꢀ

导电元件

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

26,26’,36 结合层

[0044]

27

ꢀꢀꢀꢀꢀꢀ

散热体

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

270,370 支撑脚

[0045]

28

ꢀꢀꢀꢀꢀꢀ

粘着层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

29

ꢀꢀꢀꢀꢀꢀ

导电凸块

[0046]

290

ꢀꢀꢀꢀꢀ

底胶

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

30

ꢀꢀꢀꢀꢀꢀ

第一板体

[0047]

31

ꢀꢀꢀꢀꢀꢀ

第二散热层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

32

ꢀꢀꢀꢀꢀꢀ

散热柱

[0048]

33

ꢀꢀꢀꢀꢀꢀ

线路部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

34

ꢀꢀꢀꢀꢀꢀ

第二板体

[0049]

35

ꢀꢀꢀꢀꢀꢀ

第三散热层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

350

ꢀꢀꢀꢀꢀ

散热接点

[0050]

36

ꢀꢀꢀꢀꢀꢀ

线路层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

37a,37b,37c 凹凸部

[0051]

370a,370b 端部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

a

ꢀꢀꢀꢀꢀꢀꢀ

置晶区。

具体实施方式

[0052]

以下经由特定的具体实施例说明本发明的实施方式,本领域技术人员可由本说明书所揭示的内容轻易地了解本发明的其他优点及功效。

[0053]

须知,本说明书附图所绘示的结构、比例、大小等,均仅用在配合说明书所揭示的内容,以供本领域技术人员的了解与阅读,并非用在限定本发明可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本发明所能产生的功效及所能达成的目的下,均应仍落在本发明所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“上”、“下”、“第一”、“第二”及“一”等用语,也仅为便在叙述的明了,而非用在限定本发明可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当也视为本发明可实施的范畴。

[0054]

图2其为本发明的电子封装件2的剖面示意图。如图2所示,所述的电子封装件2包括:至少一电子元件21、多个导电结构22、一第一散热层23、一封装层24、一承载结构2c以及一散热件2d。

[0055]

在本实施例中,该电子封装件2可包括多个电子元件21,21’,如图2a至2c所示,以整合成多芯片封装体2a,其包括多个电子元件21,21’、多个导电结构22、第一散热层23及该封装层24,使该多个电子元件21,21’相互分离地配置在该封装层24中。

[0056]

所述的多个电子元件21,21’为主动元件、被动元件或其组合者,其中,该主动元件例如为半导体芯片,而该被动元件例如为电阻、电容及电感。

[0057]

在本实施例中,该电子元件21,21’为半导体芯片,其具有相对的第一表面21a(如作用面)与第二表面21b(如非作用面)及邻接该第一与第二表面21a,21b的侧面21c,且该第一表面21a上具有多个电极垫210及一保护该电极垫210的绝缘体211。

[0058]

所述的导电结构22对应设在该电子元件21,21’的第一表面21a的电极垫210上以电性连接该电子元件21,21’,并外露出该绝缘体211。

[0059]

在本实施例中,该导电结构22包含有至少一种导电材220,221,222(如图2a所示)。例如,该导电材220为金属凸块(如铜凸块);或者,该导电材221也可为金属柱(如铜柱);又或者,该导电材220可为焊锡凸块(如锡膏)。应可理解地,该导电结构22可依需求选择导电材220,221,222的组成,如单一材料或多种材料等,并无特别限制。

[0060]

再者,该导电结构22凸出该绝缘体211,例如,至少一种导电材221,222凸出该绝缘体211,以令该导电结构22外露在该绝缘体211。

[0061]

所述的第一散热层23接触形成在该电子元件21的侧面21c上且经由该绝缘体211隔离所述多个导电结构22。

[0062]

在本实施例中,该第一散热层23形成在其中一电子元件21上,但该多芯片封装体2a可依需求在多个电子元件21,21’上形成该第一散热层23。

[0063]

再者,该第一散热层23为金属层,如铜层,其未电性连接该电子元件21,21’。

[0064]

又,该第一散热层23延伸形成在该电子元件21的第一表面21a上方,且经由该绝缘体211隔离该第一散热层23与该第一表面21a,即该第一散热层23与该第一表面21a之间形成有该绝缘体211,其中该绝缘体211可为芯片表面的氧化层(如:氧化硅)或线路层中的绝缘层(如:pi)。所述的封装层24包覆该电子元件21,21’、所述多个导电结构22与该第一散热层23。

[0065]

在本实施例中,该封装层24具有相对的第一侧24a与第二侧24b,且令该导电结构22外露出该封装层24的第一侧24a的表面,并使该电子元件21,21’的第二表面21b齐平该封装层24的第二侧24b,以令该电子元件21,21’外露在该封装层24的第二侧24b。

[0066]

再者,形成该封装层24的材料为绝缘材,如聚酰亚胺(polyimide,简称pi)、环氧树脂(epoxy)的封装胶体或封装材(molding compound),其可用模压(molding)、压合(lamination)或涂布(coating)的方式形成。

[0067]

又,该第一散热层23’可依需求形成在该电子元件21,21’的第二表面21b上,例如,该第一散热层23’接触结合该电子元件21,21’的第二表面21b与该封装层24的第二侧24b的表面,如图2b所示。

[0068]

另外,该第一散热层23”可依需求形成有凹凸表面23a,如图2c所示。应可理解地,有关凹凸表面的形式繁多,并无特别限制。

[0069]

所述的承载结构2c用在设置该电子元件21,21’并电性连接该导电结构22。

[0070]

在本实施例中,该承载结构2c例如为具有核心层与线路结构的封装基板、无核心层(coreless)形式线路结构的封装基板或其它封装基板形式,其包含至少一绝缘层及至少一结合该绝缘层的线路层,如至少一扇出(fan out)型重布线路层(redistribution layer,简称rdl)。应可理解地,该承载结构2c也可为其它承载芯片的板材,如导线架(lead frame)或其它具有金属布线(routing)的板体等,并不限上述。

[0071]

再者,该承载结构2c的基板制程方式繁多,例如,可采用一般非晶圆制程方式形成线路层,即采用成本较低的高分子介电材作为绝缘层,如聚酰亚胺(pi)、聚对二唑苯(polybenzoxazole,简称pbo)、预浸材(prepreg,简称pp)、封装胶体、感光型介电层或其它材料等以涂布方式形成。

[0072]

又,该承载结构2c在其下侧可形成多个导电元件25,以供该电子封装件2可经由所述导电元件25接置一如电路板的电子装置(图略)。具体地,该导电元件25可为如铜柱的金

属柱、包覆有绝缘块的金属凸块、焊球(solder ball)、具有核心铜球(cu core ball)的焊球或其它导电构造等。

[0073]

另外,可形成底胶290在该电子元件21,21’的第一表面21a(或该多芯片封装体2a)与该承载结构2c之间以包覆所述导电结构22。

[0074]

所述的散热件2d经由该结合层26结合至该多个电子元件21,21’的第二表面21b上。

[0075]

在本实施例中,该散热件2d具有一散热体27与多个设在该散热体27下侧的支撑脚270,该散热体27为散热片型式,并以下侧接触该结合层26,且该支撑脚270经由粘着层28结合在该承载结构2c上。

[0076]

再者,该结合层26为导热界面材(thermal interface material,简称tim),如高导热金属胶材。

[0077]

又,在其它实施例中,如图2’所示的电子封装件2’,该电子元件21可以其导电结构22设在一中介结构2b上,使该中介结构2b用以设置该电子元件21且电性连接该导电结构22,再将该中介结构2b设在该承载结构2c上。具体地,该中介结构2b为硅中介板(through silicon interposer,简称tsi),其具有一多个导电硅穿孔(through-silicon via,简称tsv),且可依需求形成线路重布层(rdl),例如,可采用晶圆制程制作rdl,并通过化学气相沉积(chemical vapor deposition,简称cvd)形成氮化硅或氧化硅以作为绝缘层。应可理解地,有关该中介结构2b的态样繁多,例如,在介电材上布线所形成的线路板或以封装胶体所形成的中介板,故不限上述的tsi形式。

[0078]

另外,该中介结构2b经由多个导电凸块29设在该承载结构2c上,并以底胶290包覆所述导电凸块29。例如,该导电凸块29可为如铜材的金属凸块、焊锡材或其它导电构造等。

[0079]

应可理解地,有关本发明的电子封装件的种类繁多,例如,图2”所示的晶圆级芯片尺寸封装(wafer level chip scale packaging)形式的电子封装件2”,其无需配置中介结构2b及承载结构2c,以经由所述导电结构22接置一如电路板的电子装置(图略),故该电子封装件的态样并无特别限制。

[0080]

因此,本发明的电子封装件2,2’,2”主要经由该第一散热层23的设计,以将该电子元件21所产生的热能经由其第一表面21a及侧面21c上的第一散热层23散逸至外界,故相比于现有技术,本发明的电子封装件2,2’,2”的散热途径除了该电子元件21的非作用面(第二表面21b)外,也增加其第一表面21a及侧面21c的第一散热层23,因而能大幅提升散热效果。

[0081]

再者,当该电子元件21的第一表面21a在作用中产生热能时,不仅能经由该电子元件21的第二表面21b将热能经由该结合层26及散热体27传递至该电子封装件2,2外,且能经由该第一散热层23,23’,23”将该热能经由该结合层26及散热体27传递至该电子封装件2,2外。

[0082]

另一方面,基于散热需求,该电子封装件3可依需求增设散热途径,如图3a所示的结合层36、中介结构3b、该承载结构3c及/或该散热件3d。

[0083]

如图3a所示,该结合层36包覆该多芯片封装体2a及该中介结构3b,且接触该支撑脚370,以增加该结合层36的布设范围,而增加散热效果。

[0084]

在本实施例中,该结合层36为流体型导热界面材(thermal interface material,简称tim)。

[0085]

如图3a及3b所示,该中介结构3b具有一第一板体30、设在该第一板体30中的第二散热层31及设在该第一板体30上的散热柱32。

[0086]

在本实施例中,该第一板体30为绝缘板材或半导体板材,其配置有多个线路部33(图中省略内部布线态样),以电性连接该导电结构22及该承载结构3c。

[0087]

再者,该第二散热层31为大面积金属层,如图3b’所示,且其电性隔绝该线路部33,使该第二散热层31不具电路功能。该第二散热层31可设在线路部33表面或设在线路部33中,故该第二散热层31的态样并无特别限制。

[0088]

又,该散热柱32布设在该第一板体30边缘且环绕该第一板体30(或布设该电子元件21,21’的置晶区a),如图3b’所示,并电性隔绝该线路部33,使该散热柱32不具电路功能。例如,该散热柱的形状繁多,如圆柱、椭圆形、方柱或其它态样,并无特别限制。

[0089]

另外,该第二散热层31可依需求一体连接该散热柱32,以提升散热效果。

[0090]

因此,当该电子元件21的第一表面21a在作用中产生热能时,能经由该中介结构3b的第二散热层31及/或散热柱32将该热能经由该结合层36及散热件3d传递至该电子封装件3外。

[0091]

如图3a及3c所示,该承载结构3c具有一第二板体34及设在该第二板体34中的第三散热层35。

[0092]

在本实施例中,该第二板体34为封装基板所需的板材形式,其配置有至少一线路层36(图中省略内部布线态样)。

[0093]

再者,该第三散热层35为大面积金属层,且其电性隔绝该线路层36,使该第三散热层35不具电路功能。

[0094]

又,该第三散热层35可依需求外露在该第二板体34的表面,以作为散热接点350。

[0095]

因此,当该电子元件21的第一表面21a在作用中产生热能时,能经由该承载结构3c的第三散热层35将该热能传递至该电子封装件3外。

[0096]

如图3a及3d所示,该散热件3d还具有至少一凹凸部37a,37b,37c。

[0097]

在本实施例中,该凹凸部37a形成在该散热体27下侧,以增加接触该结合层36的面积,且该凹凸部37b也可形成在该支撑脚270的端处,以增加接触该粘着层28的面积。

[0098]

再者,该散热件3d的部分支撑脚370可作为强化散热用,其可结合该第三散热层35。例如,该支撑脚270,370不仅可经由该粘着层28结合该承载结构3c,且该支撑脚370还可经由该结合层26’结合该第三散热层35的散热接点350。具体地,该凹凸部37c可依需求形成在该支撑脚370上,以增加结合该结合层26’(及/或该粘着层28)的面积。

[0099]

又,该支撑脚370可依需求设计其端部370a,370b,如图3d所示的垫形端部370a或如图3d’所示的柱形端部370b,以利在结合该第三散热层35。

[0100]

因此,当该电子元件21的第一表面21a在作用中产生热能时,能经由该承载结构3c的第三散热层35的散热接点350将该热能经由该结合层26’,36及/或该散热件3d传递至该电子封装件3外。

[0101]

综上所述,本发明的电子封装件2,2’,2”,3,主要经由该第一散热层23形成在该电子元件21的第一表面21a及侧面21c,以将该电子元件21所产生的热能经由该第一散热层23散逸至外界,故本发明的电子封装件2,2’,2”,3的散热途径包含该电子元件21的第二表面21b及侧面21c,因而能大幅提升散热效果,以满足散热需求,且避免该电子封装件2,2’,2”,

3因过热而故障的问题。

[0102]

再者,可经由增设散热途径在该电子封装件2,2’,2”,3的其它构件(该结合层36、该中介结构3b、该承载结构3c及/或该散热件3d)上,以快速有效地将该电子元件21所产生的热能传递至该电子封装件2,2’,2”,3外,故能大幅提升散热效果,以进一步满足散热需求,且避免该电子封装件2,2’,2”,3因过热而故障的问题。

[0103]

上述实施例仅用于例示性说明本发明的原理及其功效,而非用于限制本发明。任何本领域技术人员均可在不违背本发明的精神及范畴下,对上述实施例进行修改。因此本发明的权利保护范围,应如权利要求书所列。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1