削角蚀刻装置以及半导体器件制造方法与流程

[0001]

本发明构思涉及用于制造半导体器件的装置和方法,更具体地,涉及一种用于削角蚀刻衬底边缘(bevel etching a substrate edge)的装置以及使用该装置的半导体器件制造方法。

背景技术:

[0002]

在半导体器件以及使用半导体器件的电子产品中,对高容量、薄和紧凑尺寸的需求不断增长,因此已经提出各种新的封装技术。例如,半导体器件可以包括应用处理器、存储器件和图像传感器。封装技术可以将应用处理器、存储器件和图像传感器集成到单个芯片中。

技术实现要素:

[0003]

本发明构思的一些示例实施方式提供一种削角蚀刻装置(bevel etching apparatus),其能够减少或防止等离子体引起的对衬底的底表面的损伤。

[0004]

本发明构思的一些示例实施方式提供一种制造半导体器件的方法,该方法能够减少衬底边缘的缺陷。

[0005]

根据本发明构思的一些示例实施方式,一种削角蚀刻装置可以包括:卡盘板,配置为接收衬底;围绕卡盘板的周边的下等离子体隔离区(pez)环;在卡盘板上的盖板;以及围绕盖板的周边的上pez环。下pez环可以包括:环基部;和突起,从环基部的边缘向上延伸以围绕衬底的侧壁的下部。

[0006]

根据本发明构思的一些示例实施方式,一种削角蚀刻装置可以包括:腔室;在腔室中的卡盘板,该卡盘板配置为接收衬底;下pez环,围绕卡盘板的周边,该下pez环包括围绕衬底的侧表面的下部的外壁;在卡盘板上的盖板;围绕盖板的周边并在下pez环上的上pez环;以及与上pez环和下pez环相邻的偏置电极。

[0007]

根据本发明构思的一些示例实施方式,一种半导体器件制造方法可以包括:在第一衬底上形成第一半导体器件;在第二衬底上形成第二半导体器件;蚀刻第二衬底的上拐角以形成阶梯状凹槽,该上拐角与第二半导体器件径向地间隔开;以及将第二半导体器件接合到第一半导体器件。

附图说明

[0008]

图1示出流程图,其示出根据本发明构思的半导体器件制造方法的示例。

[0009]

图2至图7示出剖视图,其示出图1的半导体器件制造方法。

[0010]

图8示出剖视图,其示出蚀刻图3所示的第二衬底的上拐角的削角蚀刻装置。

[0011]

图9示出剖视图,其示出图8所示的卡盘板、下等离子体隔离区(pez)环、盖板和上pez环的示例。

[0012]

图10示出透视图,其示出图9所示的下pez环的示例。

具体实施方式

[0013]

图1示出根据本发明构思的半导体器件制造方法的示例。图2至图7示出剖视图,其示出图1的半导体器件制造方法。

[0014]

参照图1和图2,第一制造设备可以在第一衬底w1上形成第一半导体器件102(s10)。第一制造设备可以包括膜沉积装置、光刻装置和蚀刻装置,但是本发明构思不限于此。例如,第一衬底w1可以包括硅晶片。第一衬底w1可以具有约300mm的第一直径d1,但是本发明构思不限于此。第一半导体器件102可以形成在第一衬底w1的顶表面处。例如,第一半导体器件102可以是存储器件。第一半导体器件102可以包括例如dram器件或nand闪存器件。或者,第一半导体器件102可以包括应用处理器,但是本发明构思不限于此。

[0015]

参照图1和图3,第二制造设备可以在第二衬底w2上形成第二半导体器件112(s20)。第二制造设备可以与第一制造设备相同。此外,第二衬底w2可以与第一衬底w1相同。例如,第二衬底w2可以包括硅晶片。第二衬底w2可以具有约300mm的第二直径d2。第二半导体器件112可以形成在第二衬底w2的顶表面处。例如,第二半导体器件112可以包括图像传感器。

[0016]

图8示出蚀刻图3所示的第二衬底w2的上拐角的削角蚀刻装置100的示例。如这里使用的,术语“上拐角”可以表示由第二衬底w2的顶表面的边缘和第二衬底w2的侧壁或侧表面的上部界定的部分或区域。上拐角可以绕第二衬底w2的整个周边延伸。

[0017]

参照图1、图4和图8,削角蚀刻装置100可以蚀刻或修整第二衬底w2的上拐角以形成阶梯状凹槽114(s30)。削角蚀刻装置100可以向第二衬底w2的上拐角局部地提供等离子体p以形成阶梯状凹槽114。阶梯状凹槽114可以形成为具有l形或具有l形截面。例如,阶梯状凹槽114可以具有约0.5mm至约3mm的第一宽度wd1和约3μm至约30μm的第一高度h1。

[0018]

参照图8,削角蚀刻装置100可以包括腔室10、卡盘板20、下等离子体隔离区(pez)环30、偏置电极40、盖板50和上pez环60。

[0019]

腔室10可以向第二衬底w2提供与外界的气密密封或空间。腔室10可以具有小于大气压强的真空压强。

[0020]

卡盘板20可以设置在腔室10中。卡盘板20可以接收第二衬底w2。卡盘板20可以支撑第二衬底w2的中心。例如,卡盘板20可以包括卡盘基部22和电介质层24。卡盘基部22可以包括铝合金。电介质层24可以设置在卡盘基部22上。电介质层24可以包括铝氧化物(al2o3),但是本发明构思不限于此。

[0021]

源电源26可以提供在腔室10外部。源电源26可以连接到卡盘基部22,从而提供源功率28。卡盘基部22可以使用源功率28在第二衬底w2的边缘上产生等离子体p。例如,源功率28可以具有约13.56mhz的频率。

[0022]

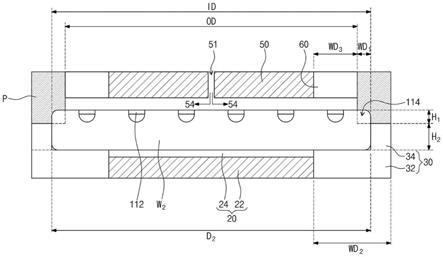

图9示出图8所示的卡盘板20、下pez环30、盖板50和上pez环60的示例。为了图示的方便,图8所示的一些部件没有在图9中示出。

[0023]

参照图9,卡盘板20、下pez环30、盖板50和上pez环60可以限制地和/或选择性地将第二衬底w2的上拐角暴露于等离子体p。下pez环30可以绕卡盘板20的侧面设置或围绕卡盘板20的侧面,并可以支撑第二衬底w2的边缘或第二衬底w2的底表面的边缘。盖板50可以覆盖第二衬底w2的中心。上pez环60可以绕盖板50设置或围绕盖板50,并可以部分地覆盖第二衬底w2的边缘或设置在第二衬底w2的边缘上方。

[0024]

下面将详细描述下pez环30、盖板50和上pez环60。

[0025]

下pez环30可以设置在卡盘板20的侧壁或侧面上或围绕卡盘板20的侧壁或侧面,和/或在卡盘板20的周边上。下pez环30可以包括例如al2o3和/或y2o3的陶瓷。下pez环30可以具有l形或具有l形截面。下pez环30可以围绕第二衬底w2的下拐角。例如,下pez环30可以围绕第二衬底w2的底表面的边缘和第二衬底w2的侧壁或侧表面的下部。下pez环30可以防止等离子体p接触第二衬底w2的底表面的边缘和第二衬底w2的下拐角。

[0026]

图10示出图9所示的下pez环30的示例。

[0027]

参照图9和图10,下pez环30可以包括环基部32和突起或外壁34。

[0028]

环基部32可以支撑第二衬底w2的边缘。环基部32可以具有与卡盘板20的电介质层24的顶表面或上表面共面的顶表面或上表面。环基部32可以具有约10mm至约50mm的第二宽度wd2。

[0029]

突起34可以设置在环基部32的边缘(例如最外边缘)上,并可以从环基部32向上(例如垂直于环基部32的顶表面)延伸。突起34可以在上pez环60的侧壁方向上(例如平行于上pez环60的侧面或侧壁)延伸。突起34可以围绕第二衬底w2的侧壁的下部和/或第二衬底w2的下拐角,并可以使第二衬底w2的上拐角或第二衬底w2的侧壁的上部暴露于等离子体p。突起34可以防止第二衬底w2的底表面和下拐角由于等离子体p而损伤。突起34可以具有与第二衬底w2的第二直径d2相同的内径id。当第二衬底w2的第二直径d2为约300mm时,突起34的内径id可以为约300mm。当第二衬底w2具有约775μm的厚度时,突起34可以具有从环基部32的顶表面起的约745μm至约772μm的第二高度h2。突起34可以使第二衬底w2的上拐角或第二衬底w2的侧壁的上部沿着约3μm至约30μm的第一高度h1暴露于等离子体p。等离子体p可以部分地蚀刻第二衬底w2的上拐角,从而形成阶梯状凹槽114。等离子体p可以蚀刻第二衬底w2的顶表面的边缘和第二衬底w2的侧壁的上部,从而形成阶梯状凹槽114。

[0030]

参照图8和图10,偏置电极40可以在腔室10中设置在下pez环30和上pez环60外部或设置为径向地远离下pez环30和上pez环60。例如,偏置电极40可以设置为与下pez环30和/或上pez环60的拐角相邻。偏置电极40可以具有环形或环的形状。偏置电极40可以使等离子体p集中在第二衬底w2的上拐角上。偏置电极40可以包括例如下电极42和上电极44。

[0031]

下电极42可以设置在下pez环30下面。等离子体p可以容纳在下电极42和上电极44之间。下电极42可以连接到偏置电源46。偏置电源46可以向下电极42供应偏置功率48。下电极42可以使用偏置功率48将等离子体p集中在第二衬底w2的上拐角上。偏置功率48可以具有约2mhz至约60mhz的频率。或者,下电极42可以被电接地,但是本发明构思不限于此。

[0032]

上电极44可以设置在下电极42上方。上电极44可以设置在上pez环60之上。当下电极42被连接到偏置电源46时,上电极44可以被电接地。或者,当下电极42被电接地时,上电极44可以连接到偏置电源46。上电极44可以使用偏置功率48将等离子体p集中在第二衬底w2的上拐角上。

[0033]

参照图8至图10,盖板50可以在腔室10中设置在卡盘板20上或之上。盖板50可以与卡盘板20重叠。盖板50和卡盘板20可以具有相同的直径或基本上相同的直径。例如,盖板50可以包括石英。对于另一示例,盖板50可以包括al2o3和/或y2o3的陶瓷,但是本发明构思不限于此。

[0034]

气体供应器52可以连接到盖板50。气体供应器52可以向盖板50供应反应气体54。

例如,盖板50可以具有限定在其中的孔或通道51。反应气体54可以通过孔51提供到第二衬底w2的顶表面。反应气体54可以沿着第二衬底w2的顶表面流动,并可以被提供到上pez环60外部的等离子体p中。例如,盖板50可以与第二衬底w2间隔开约1mm或更小。由于盖板50的底表面和第二衬底w2的顶表面以小于等离子体p的鞘宽度(sheath width)的间距间隔开,所以在盖板50和第二衬底w2之间可以不产生等离子体p。反应气体54可以激活第二衬底w2的上拐角的蚀刻反应。反应气体54可以是蚀刻气体。例如,反应气体54可以包括sf6、cf4、hf和/或nf3。

[0035]

上pez环60可以设置在盖板50的横向表面或侧表面和/或盖板50的周边上。上pez环60可以具有与盖板50的底表面共面的底表面。上pez环60可以包括例如al2o3和/或y2o3的陶瓷。上pez环60可以覆盖第二衬底w2的边缘或设置在第二衬底w2的边缘上方。由于上pez环60的底表面和第二衬底w2的顶表面以小于等离子体p的鞘宽度的间距间隔开,所以在上pez环60和第二衬底w2之间可以不产生等离子体p。

[0036]

上pez环60可以比下pez环30厚。上pez环60可以具有比下pez环30的第二宽度wd2小的第三宽度wd3。上pez环60可以具有比突起34的内径id小的外径od。例如,突起34可以具有比上pez环60的外径od大的内径id。上pez环60的外径od可以例如在从约294mm至约299mm的范围内。上pez环60可以将第二衬底w2的上拐角暴露于等离子体p。第二衬底w2的被暴露的上拐角可以具有约0.5mm至约3mm的第一宽度wd1。上pez环60可以暴露第二衬底w2的顶表面的边缘。

[0037]

返回参照图1和图5,接合装置可以将第二半导体器件112接合到第一半导体器件102(s40)。例如,将第二半导体器件112接合到第一半导体器件102的步骤s40可以包括晶片到晶片接合方法。第二衬底w2的顶表面可以接合到第一衬底w1的顶表面。尽管没有示出,但是第一半导体器件102的焊盘可以接合到第二半导体器件112的焊盘。

[0038]

参照图1和图6,抛光装置可以抛光第二衬底w2的底表面以暴露阶梯状凹槽114(s50)。例如,可以去除阶梯状凹槽114的底表面以暴露阶梯状凹槽114的侧壁或垂直侧壁。抛光第二衬底w2的底表面的步骤s50可以是例如对第二衬底w2的背面打磨(back lap)工艺或背面研磨(back grind)工艺。第二衬底w2可以被抛光以具有约3μm至约30μm的第一高度h1。当阶梯状凹槽114被暴露时,第二衬底w2可以具有约294mm至约299mm的第三直径d3。阶梯状凹槽114可以减少在对第二衬底w2的底表面的抛光工艺期间产生的第二衬底w2的裂纹碎片或颗粒缺陷。当不存在阶梯状凹槽114时,第二衬底w2的上拐角可能在抛光工艺期间产生裂纹碎片或颗粒。

[0039]

参照图1和图7,切割装置120可以沿着或邻近第一半导体器件102和第二半导体器件112切割第一衬底w1和第二衬底w2,结果半导体芯片c可以与第一衬底w1和第二衬底w2分离(s60)。切割装置120可以包括锯切装置和/或激光切割装置。半导体芯片c可以具有第一半导体器件102和第二半导体器件112的接合结构或堆叠结构。

[0040]

如上所述,根据本发明构思的一些示例实施方式的削角蚀刻装置可以使用具有围绕衬底的下拐角的突起的下pez环,因此可以防止对衬底的底表面的损伤。此外,根据本发明构思的一些示例实施方式的半导体器件制造方法可以蚀刻衬底的上拐角以形成阶梯状凹槽,并且当衬底的底表面被抛光时可以使用阶梯状凹槽来减少衬底的边缘缺陷。

[0041]

尽管已经结合本发明构思的在附图中示出的实施方式描述了本发明构思,但是本

领域技术人员将理解,在不脱离本发明构思的范围的情况下可以进行各种改变和修改。因此,将理解,上述实施方式在所有的方面仅是说明性的,而不是限制性的。本发明构思由所附权利要求限定,权利要求的等同物将被包括在其中。

[0042]

本申请要求于2019年8月27日在韩国知识产权局提交的韩国专利申请第10-2019-0104939号的优先权,其公开内容通过引用整体地结合于此。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1