显示面板的制作方法

1.本技术涉及显示技术领域,尤其涉及一种显示面板。

背景技术:

2.micro led显示技术由于其亮度高、电压低、能耗低、稳定性好、寿命长、色域宽等优点被认为是下一代新型显示技术,有望在诸多领域取得广泛的应用。目前,水平结构的led芯片在面板的电路设计及绑定(bonding)工艺上具有优势。但是,led芯片的p电极与n电极存在高度差,导致led芯片绑定时p电极与n电极承受的压力不同,引起n电极处绑定接触不良,形成暗点。

3.具体的,水平led芯片的p电极与n电极存在约1um的高度差,异方性导电膜(anisotropic conductive film,acf)中导电粒子的直径一般在2

‑

3um之间。阵列基板中的vdd电极、vss电极与源漏极层同层设置,且由同一金属层蚀刻形成。

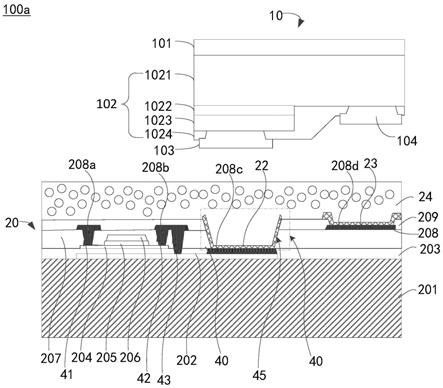

4.如图1所示,当led芯片10与阵列基板20进行绑定时,在温度、压力和时间的共同作用下,acf导电粒子实现led芯片与阵列基板在垂直方向导通,水平方向绝缘。然而,由于p电极与n电极之间的高度差,使得led芯片与阵列基板在压合过程中,p电极率先压合至阵列基板的vdd电极,而n电极与vss电极存在1um的高度差。

5.因此,在led芯片与阵列基板进行绑定的过程中,容易导致n电极与vss电极之间接触不良的风险,形成大量暗点,进而影响显示面板的品质。

技术实现要素:

6.本发明的目的在于,提供一种显示面板,以解决led芯片与阵列基板在绑定过程中,n电极与vss电极存在高度差导致接触不良的技术问题。

7.为实现上述目的,本发明提供一种显示面板,包括相互绑定压合的led芯片和阵列基板;所述led芯片包括:基底;以及第一电极部和第二电极部,突出于所述基底的上表面;其中,所述第二电极部的高度低于所述第一电极部的高度;所述阵列基板包括:衬底层,设有一压合槽;第一像素电极,设于所述压合槽内;第二像素电极,设于所述衬底层的上表面;以及异方性导电膜,设于所述衬底层、所述第一像素电极及所述第二像素电极上;当所述led芯片与所述阵列基板相互绑定压合时,所述第一电极部压合至所述压合槽,且连接至所述第一像素电极;所述第二电极部连接至所述第二像素电极。

8.进一步地,所述第二电极部与所述第一电极部的高度差,与所述第一像素电极与所述第二像素电极的高度差相同;所述第一电极部的高度与所述压合凹槽的深度相同。

9.进一步地,所述衬底层包括:玻璃基板;遮光层,设于所述玻璃基板上;缓冲层,覆盖所述遮光层,且延伸至所述玻璃基板上;有源层,设于所述缓冲上,且正对着部分所述遮光层;栅极绝缘层,设于所述有源层上;第一金属层,设于所述栅极绝缘层上;介电层,覆盖所述第一金属层,且延伸至所述有源层、所述缓冲层上;第一通孔,从所述介电层贯穿至所述有源层的表面;第二通孔,从所述介电层贯穿至所述有源层的表面;第三通孔,设于所述

第二通孔且远离所述第一通孔的一侧,所述第三通孔从所述介电层贯穿至所述遮光层的表面;以及第四通孔,设于所述第三通孔且远离所述第一通孔的一侧,所述第四通孔从所述介电层贯穿至所述遮光层的表面;第二金属层,被图案化形成源极走线、漏极走线、vdd走线以及vss走线;其中,所述源极走线通过所述第一通孔连接至所述有源层;所述漏极走线通过所述第二通孔连接至所述有源层,所述漏极通过所述第三通孔连接至所述遮光层;所述vdd走线设于所述第四通孔的底部,连接至所述遮光层,其中所述vdd走线上表面与所述第四通孔的侧壁围成一凹槽;所述vss走线设于所述介电层上且远离所述第一通孔的一侧;以及钝化层,设于所述介电层上,且覆盖所述源极走线和所述漏极走线。

10.进一步地,所述第一像素电极设于所述凹槽内,连接至所述vdd走线,且从所述凹槽的侧壁延伸至底壁形成所述压合槽;所述第二像素电极设于所述vss走线上,且延伸至部分所述钝化层的表面。

11.进一步地,所述衬底层包括:玻璃基板;遮光层,设于所述玻璃基板上;缓冲层,覆盖所述遮光层,且延伸至所述玻璃基板上;有源层,设于所述缓冲上,且正对着部分所述遮光层;栅极绝缘层,设于所述有源层上及所述缓冲层上;第一金属层,包括第一栅极和第二栅极,所述第一金属层设于所述栅极绝缘层上;介电层,覆盖所述第一金属层,且延伸至所述有源层、所述缓冲层上;第一通孔,从所述介电层贯穿至所述有源层的表面;第二通孔,从所述介电层贯穿至所述有源层的表面;第三通孔,设于所述第二通孔且远离所述第一通孔的一侧,所述第三通孔从所述介电层贯穿至所述遮光层的表面;以及第四通孔,设于所述第三通孔且远离所述第一通孔的一侧,所述第四通孔从所述介电层贯穿至所述第二栅极的表面;第二金属层,被图案化形成源极走线、漏极走线、vdd走线以及vss走线;其中,所述源极走线通过所述第一通孔连接至所述有源层;所述漏极走线通过所述第二通孔连接至所述有源层,所述漏极通过所述第三通孔连接至所述遮光层;所述vdd走线设于所述第四通孔的底部,连接至所述第二栅极,其中所述vdd走线上表面与所述第四通孔的侧壁围成一凹槽;所述vss走线设于所述介电层上且远离所述第一通孔的一侧;以及钝化层,设于所述介电层上,且覆盖所述源极走线和所述漏极走线,所述钝化层设有第五通孔,贯穿至所述vss走线的表面。

12.进一步地,所述第一像素电极设于所述凹槽内,且连接至所述vdd走线,其中所述第一像素电极的上表面与所述凹槽的侧壁,形成所述压合槽;所述第二像素电极通过所述第五通孔连接至所述vss走线,且延伸至所述钝化层的表面。

13.进一步地,所述衬底层包括:玻璃基板;第一金属层,设于所述玻璃基板上,且被图案化形成栅极和vdd走线;栅极绝缘层,设于所述玻璃基板上,且覆盖所述栅极;有源层,设于所述栅极绝缘层上,且正对于所述栅极;绝缘层,设于所述栅极绝缘层上,且覆盖所述有源层;第六通孔,从所述绝缘层贯穿至所述有源层的表面;第七通孔,从所述绝缘层贯穿至所述有源层的表面;第二金属层,被图案化形成源极走线、漏极走线、vdd走线以及vss走线;其中,所述源极走线通过所述第六通孔连接至所述有源层;所述漏极走线通过所述第七通孔连接至所述有源层,且延伸至所述vdd走线上;所述vss走线设于所述绝缘层上;以及钝化层,设于所述绝缘层上,且覆盖所述源极走线和部分所述漏极走线。

14.进一步地,所述第一像素电极从所述钝化层的侧壁延伸至所述漏极走线的侧壁,且连接至所述vdd走线,形成所述压合槽;所述第二像素电极设于所述钝化层上,且延伸至

部分所述钝化层上。

15.进一步地,所述衬底层包括:玻璃基板;第一金属层,设于所述玻璃基板上,被图案化形成第一栅极和第二栅极;栅极绝缘层,设于所述玻璃基板上,且覆盖所述第一栅极;有源层,设于所述栅极绝缘层上,且正对于所述第一栅极;第八通孔,从所述栅极绝缘层贯穿至所述玻璃基板表面;第二金属层,被图案化形成源极走线、漏极走线、vdd走线以及vss走线;所述源极走线和所述漏极走线分别设于所述有源层的两侧,且延伸至所述栅极绝缘层的表面;所述vdd走线设于所述第八通孔的底部,且连接至所述第二栅极,其中所述vdd走线上表面与所述第八通孔的侧壁围成一凹槽;所述vss走线设于所述栅极绝缘层上;以及钝化层,设于所述绝缘层上,且覆盖所述源极走线和部分所述漏极走线;其中,所述第一像素电极从所述钝化层的侧壁延伸至所述vdd走线,所述vdd走线的上表面与所述第八通孔的侧壁围成所述压合凹槽;所述第二像素电极设于所述vss走线上,且延伸至部分所述钝化层上。

16.进一步地,所述led芯片包括:外延层,设于所述基底上;p电极,设于所述外延层的p型层上;以及n电极,设于所述外延层的n型层上;其中,所述p电极与所述外延层形成第一电极部,所述n电极与所述外延层形成所述第二电极部。

17.本发明的技术效果在于,提供一种显示面板,通过设置led芯片的p电极与n电极的高度差,与阵列基板的第一像素电极与第二像素电极的高度差相同,使得第一像素电极所受到p电极的力度,与第二像素电极所受到n电极的力度是相同的,从而有利于提高所述led芯片和阵列基板的绑定良率。

附图说明

18.下面结合附图,通过对本技术的具体实施方式详细描述,将使本技术的技术方案及其它有益效果显而易见。

19.图1为现有显示面板的结构示意图。

20.图2为本技术实施例1提供的显示面板的结构示意图。

21.图3为本技术实施例1提供的led芯片与阵列基板绑定压合后的结构示意图。

22.图4为本技术实施例2提供的显示面板的结构示意图。

23.图5为本技术实施例3提供的显示面板的结构示意图。

24.图6为本技术实施例4提供的显示面板的结构示意图。

25.附图部件标识如下:

26.100a、100b、100c、100d显示面板;

27.10、led芯片;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

20、阵列基板;

28.101、基底;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

102、外延层;

29.103、p电极;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

104、n电极;

30.1021、n型层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1022、发光层;

31.1023、p型层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1024、ito透明导电层;

32.21、衬底层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

22、第一像素电极;

33.23、第二像素电极;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

24、异方性导电膜;

34.201、玻璃基板;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

202、遮光层;

35.203、缓冲层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

204、有源层;

36.205、栅极绝缘层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

206、第一金属层;

37.207、介电层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

208、第二金属层;

38.209、钝化层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

208a、源极走线;

39.208b、漏极走线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

208c、vdd走线;

40.208d、vss走线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

206a、第一栅极;

41.206b、第二栅极;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

40、压合槽;

42.41、第一通孔;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

42、第二通孔;

43.43、第三通孔;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

44、第四通孔;

44.45、凹槽;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

46、第五通孔;

45.47、第六通孔;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

48、第七通孔;

46.49、第八通孔。

具体实施方式

47.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。在本技术的描述中,需要理解的是,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个所述特征。在本技术的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

48.实施例1

49.如图2所示,本实施例提供一种显示面板100a,其包括相互绑定压合的led芯片10和阵列基板20。

50.所述led芯片10包括基底101、外延层102、p电极103以及n电极104。

51.所述外延层102设于所述基底101上,所述外延层102包括n型层1021、发光层1022、p型层1023以及ito透明导电层1024。所述n型层1021设于所述基底101上;所述发光层1022设于所述n型层1021上;所述n电极104设于所述n型层1021上;所述p型层1023设于所述发光层1022上;所述ito透明导电层1024设于所述p型层1023上,且延伸至所述n型层1021上;所述p电极103贯穿所述ito透明导电层1024连接至所述p型层1023。

52.在本实施例中,所述p电极103与所述外延层102形成第一电极部,所述n电极104与所述外延层102形成所述第二电极部。其中,所述第二电极部的高度低于所述第一电极部的高度,所述第二电极部与所述第一电极部的高度差为0.8

‑

1.2μm,优选地,所述第二电极部与所述第一电极部的高度差为1μm。

53.阵列基板20包括衬底层21、第一像素电极22、第二像素电极23以及异方性导电膜24。

54.所述衬底层21设有一压合槽40,所述第一像素电极22设于所述压合槽40内。所述第二像素电极23设于所述衬底层21的上表面。所述异方性导电膜24设于所述衬底层21、所述第一像素电极22及所述第二像素电极23上。

55.本实施例中,所述第二电极部与所述第一电极部的高度差,与所述第一像素电极22与所述第二像素电极23的高度差相同,所述第一电极部的高度与所述压合凹槽的深度相同。

56.如图3所示,当所述led芯片10与所述阵列基板20相互绑定压合时,所述第一电极部压合至所述压合槽40,且连接至所述第一像素电极22,所述第二电极部连接至所述第二像素电极23,这样可以使得所述p电极103和所述n电极104同时压合时,受力均匀,提升绑定良率。

57.具体的,所述衬底层21包括玻璃基板201、遮光层202、缓冲层203、有源层204、栅极绝缘层205、第一金属层206、介电层207、第二金属层208以及钝化层209。

58.所述遮光层202设于所述玻璃基板201上。

59.所述缓冲层203覆盖所述遮光层202,且延伸至所述玻璃基板201上。

60.所述有源层204设于所述缓冲上,且正对着部分所述遮光层202。

61.所述栅极绝缘层205,设于所述有源层204上。

62.所述第一金属层206设于所述栅极绝缘层205上。其中,所述第一金属层206为栅极。

63.所述介电层207覆盖所述第一金属层206,且延伸至所述有源层204、所述缓冲层203上。

64.所述衬底层21开设有多个通孔。其中,第一通孔41从所述介电层207贯穿至所述有源层204的表面。第二通孔42从所述介电层207贯穿至所述有源层204的表面。第三通孔43设于所述第二通孔42且远离所述第一通孔41的一侧,所述第三通孔43从所述介电层207贯穿至所述遮光层202的表面。第四通孔44设于所述第三通孔43且远离所述第一通孔41的一侧,所述第四通孔44从所述介电层207贯穿至所述遮光层202的表面。

65.所述第二金属层208被图案化形成源极走线208a、漏极走线208b、vdd走线208c以及vss走线208d。

66.本实施例中,所述源极走线208a通过所述第一通孔41连接至所述有源层204;所述漏极走线208b通过所述第二通孔42连接至所述有源层204,所述漏极通过所述第三通孔43连接至所述遮光层202;所述vdd走线208c设于所述第四通孔44的底部,连接至所述遮光层202,其中所述vdd走线208c上表面与所述第四通孔44的侧壁围成一凹槽45;所述vss走线208d设于所述介电层207上且远离所述第一通孔41的一侧。所述vdd走线208c的厚度与所述vss走线208d的厚度相同。

67.所述钝化层209设于所述介电层207上,且覆盖所述源极走线208a和所述漏极走线208b。

68.本实施例中,所述第一像素电极22设于所述凹槽45内,连接至所述vdd走线208c,且从所述凹槽45的侧壁延伸至底壁形成所述压合槽40;所述第二像素电极23设于所述vss走线208d上,且延伸至部分所述钝化层209的表面。当所述led芯片10与所述阵列基板20相互绑定压合时,由于所述第二电极部与所述第一电极部的高度差,与所述第一像素电极22与所述第二像素电极23的高度差相同,这样可以使得所述第一像素电极22所受到所述p电极103的力度,与所述第二像素电极23所受到所述n电极104的力度是相同的,从而有利于提高所述led芯片10和所述阵列基板20的绑定良率。另外,在压合过程中,所述异方性导电膜24中的acf离子爆裂,使得所述led芯片10的p电极103与所述第一像素电极22相互导通,所述n电极104与所述第二像素电极23相互导通,从而使得所述led芯片10与所述阵列基板20相互导通,且防止上下电极接触不良,防止显示面板100a形成大量暗点。

69.实施例2

70.本实施例提供一种显示面板,其包括实施例1大部分技术方案,其区别在于,所述阵列基板的结构不同。

71.如图4所示,本实施例提供一种显示面板100b,所述阵列基板20包括玻璃基板201、遮光层202、缓冲层203、有源层204、栅极绝缘层205、第一金属层206、介电层207、第二金属层208以及钝化层209。

72.所述遮光层202设于所述玻璃基板201上。

73.所述缓冲层203覆盖所述遮光层202,且延伸至所述玻璃基板201上。

74.所述有源层204设于所述缓冲上,且正对着部分所述遮光层202。

75.所述栅极绝缘层205设于所述有源层204上及所述缓冲层203上。

76.所述第一金属层206包括第一栅极206a和第二栅极206b,所述第一金属层206设于所述栅极绝缘层205上。

77.所述介电层207覆盖所述第一金属层206,且延伸至所述有源层204、所述缓冲层203上。

78.所述衬底层21还包括多个通孔。其中,第一通孔41从所述介电层207贯穿至所述有源层204的表面。第二通孔42从所述介电层207贯穿至所述有源层204的表面。第三通孔43设于所述第二通孔42且远离所述第一通孔41的一侧,所述第三通孔43从所述介电层207贯穿至所述遮光层202的表面。第四通孔44设于所述第三通孔43且远离所述第一通孔41的一侧,所述第四通孔44从所述介电层207贯穿至所述第二栅极206b的表面。

79.所述第二金属层208被图案化形成源极走线208a、漏极走线208b、vdd走线208c以及vss走线208d。其中,所述源极走线208a通过所述第一通孔41连接至所述有源层204;所述漏极走线208b通过所述第二通孔42连接至所述有源层204,所述漏极通过所述第三通孔43连接至所述遮光层202;所述vdd走线208c设于所述第四通孔44的底部,连接至所述第二栅极206b,其中所述vdd走线208c上表面与所述第四通孔44的侧壁围成一凹槽45;所述vss走线208d设于所述介电层207上且远离所述第一通孔41的一侧。

80.所述钝化层209设于所述介电层207上,且覆盖所述源极走线208a和所述漏极走线208b,所述钝化层209设有第五通孔46,贯穿至所述vss走线208d的表面。

81.在本实施例中,所述第一像素电极22设于所述凹槽45内,且连接至所述vdd走线208c,其中所述第一像素电极22的上表面与所述凹槽45的侧壁,形成所述压合槽40;所述第二像素电极23通过所述第五通孔46连接至所述vss走线208d,且延伸至所述钝化层209的表面,或者,所述第二像素电极23设于所述vss走线208d上,且延伸至所述钝化层209的表面(图未示)。

82.所述第一像素电极22设于所述凹槽45内,且连接至所述vdd走线208c,其中所述第一像素电极22的上表面与所述凹槽45的侧壁,形成所述压合槽40;所述第二像素电极23通过所述第五通孔连接至所述vss走线208d,且延伸至所述钝化层209的表面。

83.当所述led芯片10与所述阵列基板20相互绑定压合时,由于所述第二电极部与所述第一电极部的高度差,与所述第一像素电极22与所述第二像素电极23的高度差相同,这样可以使得所述第一像素电极22所受到所述p电极103的力度,与所述第二像素电极23所受到所述n电极104的力度是相同的,从而有利于提高所述led芯片10和所述阵列基板20的绑

定良率。另外,在压合过程中,所述异方性导电膜24中的acf离子爆裂,使得所述led芯片10的p电极103与所述第一像素电极22相互导通,所述n电极104与所述第二像素电极23相互导通,从而使得所述led芯片10与所述阵列基板20相互导通,且防止上下电极接触不良,防止显示面板100a形成大量暗点。

84.实施例3

85.本实施例提供一种显示面板,其包括实施例1所述led芯片的技术方案,其区别在于,所述衬底层的结构不同。

86.如图5所示,所述阵列基板20包括玻璃基板201、第一金属层206、栅极绝缘层205、有源层204、绝缘层300、第二金属层208以及钝化层209。

87.所述第一金属层206设于所述玻璃基板201上,且被图案化形成栅极和vdd走线208c。

88.所述栅极绝缘层205设于所述玻璃基板201上,且覆盖所述栅极。

89.所述有源层204设于所述栅极绝缘层205上,且正对于所述栅极。

90.所述绝缘层300设于所述栅极绝缘层205上,且覆盖所述有源层204。

91.所述阵列基板20还包括多个通孔。其中,第六通孔47从所述绝缘层300贯穿至所述有源层204的表面。第七通孔48从所述绝缘层300贯穿至所述有源层204的表面。

92.所述第二金属层208被图案化形成源极走线208a、漏极走线208b、vdd走线208c以及vss走线208d。其中,所述源极走线208a通过所述第六通孔47连接至所述有源层204;所述漏极走线208b通过所述第七通孔48连接至所述有源层204,且延伸至所述vdd走线208c上;所述vss走线208d设于所述绝缘层300上。

93.所述钝化层209设于所述绝缘层300上,且覆盖所述源极走线208a和部分所述漏极走线208b。

94.所述第一像素电极22从所述钝化层209的侧壁延伸至所述漏极走线208b的侧壁,且连接至所述vdd走线208c,形成所述压合槽40;所述第二像素电极23设于所述钝化层209上,且延伸至部分所述钝化层209上。

95.当所述led芯片10与所述阵列基板20相互绑定压合时,由于所述第二电极部与所述第一电极部的高度差,与所述第一像素电极22与所述第二像素电极23的高度差相同,这样可以使得所述第一像素电极22所受到所述p电极103的力度,与所述第二像素电极23所受到所述n电极104的力度是相同的,从而有利于提高所述led芯片10和所述阵列基板20的绑定良率。另外,在压合过程中,所述异方性导电膜24中的acf离子爆裂,使得所述led芯片10的p电极103与所述第一像素电极22相互导通,所述n电极104与所述第二像素电极23相互导通,从而使得所述led芯片10与所述阵列基板20相互导通,且防止上下电极接触不良,防止显示面板100a形成大量暗点。

96.实施例4

97.本实施例提供一种显示面板,其包括实施例1所述led芯片的技术方案,其区别在于,所述阵列基板的结构不同。

98.如图6所示,所述阵列基板20包括玻璃基板201、第一金属层206、栅极绝缘层205、有源层204、第二金属层208以及钝化层209。

99.所述第一金属层206设于所述玻璃基板201上。

100.所述第一金属层206设于所述玻璃基板201上,被图案化形成第一栅极206a和第二栅极206b。

101.所述栅极绝缘层205设于所述玻璃基板201上,且覆盖所述第一栅极206a。

102.所述有源层204设于所述栅极绝缘层205上,且正对于所述第一栅极206a。

103.第八通孔49,从所述栅极绝缘层205贯穿至所述玻璃基板201表面。

104.所述第二金属层208被图案化形成源极走线208a、漏极走线208b、vdd走线208c以及vss走线208d;所述源极走线208a和所述漏极走线208b分别设于所述有源层204的两侧,且延伸至所述栅极绝缘层205的表面;所述vdd走线208c设于所述第八通孔49的底部,且连接至所述第二栅极206b,其中所述vdd走线208c上表面与所述第八通孔49的侧壁围成一凹槽45;所述vss走线208d设于所述栅极绝缘层205上。

105.所述钝化层209设于所述绝缘层300上,且覆盖所述源极走线208a和部分所述漏极走线208b;其中,所述第一像素电极22从所述钝化层209的侧壁延伸至所述vdd走线208c,所述vdd走线208c的上表面与所述第八通孔49的侧壁围成所述压合凹槽45;所述第二像素电极23设于所述vss走线208d上,且延伸至部分所述钝化层209上。

106.当所述led芯片10与所述阵列基板20相互绑定压合时,由于所述第二电极部与所述第一电极部的高度差,与所述第一像素电极22与所述第二像素电极23的高度差相同,这样可以使得所述第一像素电极22所受到所述p电极103的力度,与所述第二像素电极23所受到所述n电极104的力度是相同的,从而有利于提高所述led芯片10和所述阵列基板20的绑定良率。另外,在压合过程中,所述异方性导电膜24中的acf离子爆裂,使得所述led芯片10的p电极103与所述第一像素电极22相互导通,所述n电极104与所述第二像素电极23相互导通,从而使得所述led芯片10与所述阵列基板20相互导通,且防止上下电极接触不良,防止显示面板100a形成大量暗点。

107.在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

108.以上对本技术实施例所提供的一种显示面板进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例的技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1