智能功率级模块的封装结构及晶圆结构的制作方法

1.本实用新型涉及半导体封装领域,尤其是一种智能功率级模块的封装结构及晶圆结构。

背景技术:

2.现有的智能功率级模块用焊料接合芯片焊垫与引线框架时,经常存在导电的焊料形成的焊珠或隆起,使得芯片表面的电极与芯片侧边的半导体衬底直接短路,降低了成品的可靠度。

技术实现要素:

3.基于此,本实用新型所要解决的技术问题之一是提供一种智能功率级模块的封装结构,具备非常高的可靠性,能够避免芯片表面的电极与芯片侧边的半导体衬底直接短路。

4.为解决上述技术问题,本实用新型一种技术方案是,一种智能功率级模块的封装结构,包括引线框架、第一芯片、第二芯片、导电夹,第一芯片及第二芯片夹设于引线框架与导电夹之间,第一芯片、第二芯片分别具有第一表面、第二表面及侧壁,第二表面具有组件区与切割区,切割区位于组件区的周围;

5.第二芯片还包括焊垫和绝缘层;焊垫设置于第二表面的组件区;绝缘层设置于第二芯片的第二表面,并覆盖组件区及切割区,且暴露焊垫;在第二芯片两侧的侧壁露出绝缘层。

6.在一实施例中,在组件区与切割区之间有封装环,设置于第二表面。封装环用来隔离防护因为外部切割应力、潮湿、外部电荷带入,从而影响内部芯片性能。此外,还作为组件区与切割区的分界点,用于区分切割区域。

7.在一实施例中,第二芯片的第二表面面向引线框架,焊垫透过焊料层电性连接引线框架。

8.在一实施例中,第一芯片的第二表面及第二芯片的第一表面面向导电夹并彼此电性连接。

9.在一实施例中,导电夹的一端延伸设有接脚部,接脚部通过焊料层电性连接引线框架。

10.本实用新型所要解决的技术问题之二是提供一种晶圆结构,不仅能提高智能功率级模块成品的可靠性,而且保障制作效率不受影响。为解决上述技术问题,本实用新型另一种技术方案是,一种晶圆结构,晶圆结构包括多个芯片及切割道,芯片具有第一表面、第二表面及侧壁,第二表面具有组件区与切割区,切割区位于组件区的周围;芯片还包括焊垫和绝缘层,焊垫设置于第二表面的组件区,绝缘层设置于芯片的第二表面,并覆盖组件区及切割区,且暴露焊垫;切割道位于相邻的多个芯片之间,其中,绝缘层完全覆盖切割道。此处说述的芯片为第一芯片或者第二芯片。

11.本实用新型与现有技术相比所带来的有益效果是,通过将绝缘层覆盖组件区及切

割区并暴露焊垫,该结构能够在焊接工序中,避免焊料形成的焊珠或隆起,从而造成与芯片表面的电极与芯片切割区的半导体衬底直接短路的质量问题,提高成品的可靠性和稳定性。在晶圆切片制程中,在切割晶圆之前,在相邻的芯片之间的切割道覆盖有绝缘层。在切割程序中,切割相邻两个芯片之间切割道的同时切割绝缘层,在没有增加工序而降低效率的情况,提供前述绝缘层结构来提高成品的可靠性和稳定性。

附图说明

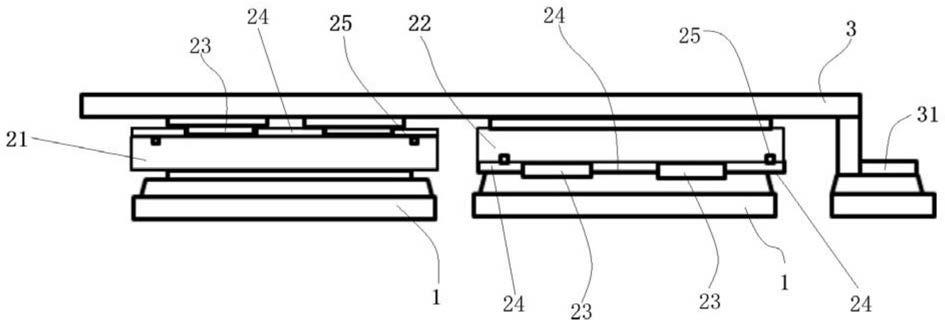

12.图1为实施例1的智能功率级模块的封装结构的主视图。

13.图2为实施例2的单个芯片的示意图。

14.图3为实施例2的晶圆切片工序的示意图。

具体实施方式

15.为使本实用新型的上述目的、特征和优点能够更加明显易懂,下面结合附图对本实用新型的具体实施方式做详细的说明。在下面的描述中阐述了很多具体细节以便于充分理解本实用新型。但是本实用新型能够以很多不同于在此描述的其它方式来实施,本领域技术人员可以在不违背本实用新型内涵的情况下做类似改进,因此本实用新型不受下面公开的具体实施例的限制。

16.实施例1

17.如图1所示,一种智能功率级模块的封装结构,包括引线框架1、第一芯片21、第二芯片22、导电夹3。导电夹3的一端延伸设有接脚部31,接脚部31通过焊料层电性连接引线框架1。第一芯片21及第二芯片22夹设于引线框架1与导电夹3之间。第一芯片21、第二芯片22分别具有第一表面、第二表面及侧壁,第二表面包括有组件区与切割区,切割区位于组件区的周围。第二芯片22还包含焊垫23和绝缘层24,其中,第二芯片22的焊垫23设置于第二表面的组件区;第二芯片22的绝缘层24设置于第二表面,覆盖组件区及切割区,并暴露焊垫23。并且,在第二芯片22的侧壁露出绝缘层24。第二芯片22的第二表面面向引线框架1,焊垫23透过焊料层与引线框架1电性连接。第一芯片21和第二芯片22的封装环25均设置于第二表面的表面,位于组件区与切割区之间有封装环25。封装环25用来隔离防护因为外部切割应力、潮湿、外部电荷带入,从而影响内部芯片性能。此外,还作为组件区与切割区的分界点,用于区分组件区与切割区。

18.该结构通过在将芯片的绝缘层24设置于第二表面,覆盖组件区及切割区,并暴露焊垫23,该结构能够在焊接工序中,避免焊料形成的焊珠或隆起,从而造成芯片表面的电极与芯片切割区的半导体衬底直接短路的质量问题,提高成品的可靠性和稳定性。

19.在本实施方式中,第一芯片21第二表面面向导电夹3;第一芯片21还包含焊垫23和绝缘层24,第一芯片21的焊垫23设置于第二表面的组件区,第一芯片21的绝缘层24设置于第二表面,覆盖组件区及切割区,并暴露焊垫23;在第一芯片21的侧壁露出绝缘层24。第一芯片21的第二表面及第二芯片22的第一表面面向导电夹3并彼此电性连接。

20.实施例2

21.如图2和3所示,本实施例涉及种技术方案是一种晶圆结构,包括多个芯片及切割道,本实施例中的芯片具体是第二芯片22,在其他实施方式中,亦可具体是第一芯片21。切

割道6位于相邻的多个芯片之间,绝缘层24完全覆盖所述切割道。。

22.请参阅图3,本实施例中,切割晶圆制备上述芯片的晶圆切片制程中,晶圆置于切割工位上,在芯片的第二表面包括切割道6覆盖绝缘层24,以封装环25为分界点,封装环25靠近芯片边缘的区域为芯片与切割道6的切割分界线,芯片间的切割道6置于切割线路上,切割头5沿切割线路切割切割道6的同时切割绝缘层24,形成分離的第二芯片22。该制程工艺在切割道6覆盖有绝缘层24,利用切割程序切割相邻两个芯片之间切割道的同时切割绝缘层24,在没有增加工序、降低效率的情况,提供前述绝缘层结构来提高成品的可靠性和稳定性。

23.以上所述,仅为本实用新型的较佳实施例而已,当不能以此限定本发明的保护范围,即凡依本发明所作的简单的等效变化与修改,皆仍属本实用新型所涵盖的范围。另外本实用新型的任一实施例或权利要求范围不须达到本实用新型所揭示的全部目的或优点或特点。

技术特征:

1.一种智能功率级模块的封装结构,包括引线框架、第一芯片、第二芯片、导电夹,所述第一芯片及所述第二芯片夹设于所述引线框架与所述导电夹之间,其特征在于:所述第一芯片、所述第二芯片分别具有第一表面、第二表面及侧壁,所述第二表面具有组件区与切割区,所述切割区位于所述组件区的周围;所述第二芯片还包括焊垫和绝缘层,所述焊垫设置于所述第二表面的所述组件区,所述绝缘层设置于所述第二芯片的所述第二表面,并覆盖所述组件区及所述切割区,且暴露所述焊垫;其中,所述第二芯片的所述侧壁露出所述绝缘层。2.根据权利要求1所述的封装结构,其特征在于:在所述组件区与所述切割区之间有封装环,设置于所述第二表面。3.根据权利要求1所述的封装结构,其特征在于:其中所述第二芯片的所述第二表面面向所述引线框架,所述焊垫透过焊料层电性连接所述引线框架。4.根据权利要求1所述的封装结构,其特征在于:所述第一芯片的所述第二表面及所述第二芯片的所述第一表面面向所述导电夹并彼此电性连接。5.根据权利要求1所述的封装结构,其特征在于:所述导电夹的一端延伸设有接脚部,所述接脚部通过焊料层电性连接所述引线框架。6.一种晶圆结构,其特征在于:所述晶圆结构包括多个芯片及切割道,所述芯片具有第一表面、第二表面及侧壁,所述第二表面具有组件区与切割区,所述切割区位于所述组件区的周围;所述芯片还包括焊垫和绝缘层,所述焊垫设置于所述第二表面的所述组件区,所述绝缘层设置于所述芯片的所述第二表面,并覆盖所述组件区及所述切割区,且暴露所述焊垫;所述切割道位于相邻的所述多个芯片之间,其中,绝缘层完全覆盖所述切割道。

技术总结

本实用新型公开了一种智能功率级模块的封装结构及晶圆结构,智能功率级模块的封装结构包括引线框架、第一芯片、第二芯片、导电夹,第一芯片与第二芯片分别具有第一表面、第二表面及侧壁,第二表面具有组件区与切割区,切割区位于组件区的两侧;第二芯片还包括焊垫和绝缘层,焊垫设置于第二表面的组件区,绝缘层设置于第二芯片的第二表面,并覆盖组件区及切割区,且暴露焊垫;第二芯片的侧壁露出绝缘层。晶圆结构在相邻的芯片之间具有切割道,绝缘层完全覆盖切割道。该结构能够避免焊料形成的焊珠或隆起造成芯片的直接短路问题,提高成品的可靠性和稳定性。靠性和稳定性。靠性和稳定性。

技术研发人员:黄水木 苏子龙 王光峰

受保护的技术使用者:力智电子(深圳)有限公司

技术研发日:2021.03.12

技术公布日:2021/10/8

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1