片上集成检波功能的CMOS功率放大器芯片的制作方法

片上集成检波功能的cmos功率放大器芯片

技术领域

1.本发明涉及cmos功率放大器芯片,具体涉及片上集成检波功能的cmos功率放大器芯片。

背景技术:

2.随着通信技术的不断发展,无线通信技术也越来越成熟,射频功率放大器是各种无线通信系统中不可或缺的关键器件,它主要用于将收发信机输出的已调制射频信号进行功率放大,以得到满足无线通信需求的射频信号。在实际应用过程中,通常需要对射频功率放大器输出的射频信号进行功率检测,从而为无线通信系统的精确控制提供依据。因此,亟需一种小型化片上集成检波功能的cmos功率放大器芯片。

3.现有技术中,公开号为cn104852695a,公开日为2015年08月19日,名称为“一种用于功率放大器的自偏置功率检测电路”的中国发明专利,公开了一种用于功率放大器的自偏置功率检测电路,包括信号采集电路、信号放大电路和信号整形电路,其中:信号采集电路用于从被检测电路中采集信号,并能够控制采集的信号大小;信号放大电路用于对信号采集电路采集的信号进行放大,以实现足够的输出电平信号;信号整形电路用于对放大后信号进行整形和滤波,从而输出平滑的电平信号。

4.上述发明专利采用电容耦合的方式对功率放大器的信号进行采集,可以得到正比于功率放大器输出功率的电压信号。然而,采用该功率检测电路得到的检波器输出电压在高低温(

‑

55℃~+85℃)状态下波动较大,无法为无线通信系统的精确控制提供依据。

技术实现要素:

5.本发明旨在提供一种片上集成检波功能的cmos功率放大器芯片,在具有温补功能的功率放大器的输出端口并联一个电阻,通过该电阻把射频信号传输至与功率放大器连接的功率检测器,使放大器增益、放大器输出功率和检波器输出电压在高低温(

‑

55℃~+85℃)状态下波动很小。

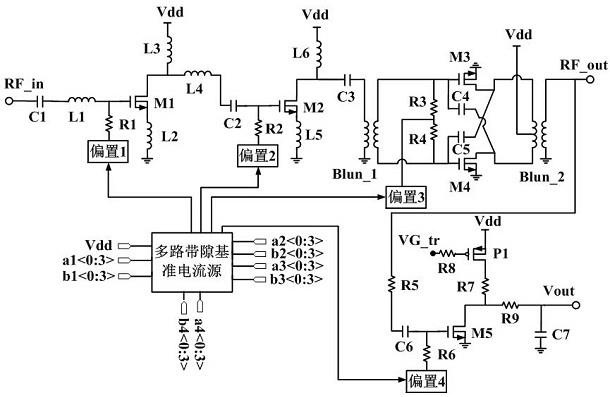

6.为了实现上述发明目的,本发明的技术方案如下:片上集成检波功能的cmos功率放大器芯片,其特征在于,包括具有温度补偿功能的功率放大器和用于检测所述功率放大器输出功率的功率检测器;所述功率放大器包括第一级放大、第二级放大和第三级放大,其中,第一级放大和第二级放大均为共源极放大器,第三级放大为采用变压器巴伦功率合成的差分放大器;所述功率检测器包括检波管第五nmos管和由第九电阻r9和第七电容c7构成的rc低通滤波器,以及第六电容c6、第七电阻r7、pmos管p1、第八电阻r8和偏置电路四;所述偏置电路四用于为第五nmos管m5提供和温度成负斜率的偏压,使第五nmos管m5工作在亚阈值区域;功率放大器的第三级放大输出端口rf_out并联有一个电阻,功率放大器输出的射频信号通过该电阻传输至功率检测器,并经过所述检波管产生dc以及高次谐波分量,最后经过rc低通滤波器后,输出检波电压vout。

7.进一步的,功率检测器的输入端通过第五电阻r5连接功率放大器的输出端rf_

out,第五电阻r5的第二端连接第六电容c6的第一端,第六电容c6的第二端连接第六电阻r6的第一端及第五nmos管m5的栅极,第六电阻r6的第二端接至偏置电路四,第五nmos管m5的源极接地,第五nmos管m5的漏极连接第七电阻r7的第一端及第九电阻r9的第一端,第七电阻r7的第二端连接第一pmos管p1的漏极,第一pmos管p1的栅极连接第八电阻r8的第一端,第一pmos管p1的源极连接电源电压vdd,第八电阻r8的第二端连接控制电压vg_tr;第九电阻r9的第二端为检测电压输出端口,同时连接第七电容c7的第一端,第七电容c7的第二端接地。

8.进一步的,所述第一级放大包括第一电容c1、第一电感l1、第二电感l2、偏置电路一和第一nmos管m1;功率放大器的输入端rf_in通过第一电容c1连接至第一电感l1的第一端,第一电感l1的第二端连接第一电阻r1的第一端及第一nmos管m1的栅极,第一电阻r1的第二端连接至偏置电路一的输出端,第一nmos管m1的源极连接第二电感l2的第一端,第二电感l2的第二端接地。

9.进一步的,所述第二级放大包括第二电容c2、第四电感l4、第三电感l3、第五电感l5、偏置电路二、第二nmos管m2、第六电感l6和第三电容c3,第一nmos管m1的漏极连接第三电感l3的第一端及第四电感l4的第一端,第三电感l3的第二端连接电源电压vdd,第四电感l4的第二端接第二电容c2的第一端,第二电容c2的第二端连接第二电阻r2的第一端及第二nmos管m2的栅极,第二电阻r2的第二端连接至偏置电路二的输出端,第二nmos管m2的源极连接第五电感l5的第一端,第五电感l5的第二端接地,第二nmos管m2的漏极连接第六电感l6的第一端及第三电容c3的第一端,第六电感l6的第二端连接电源电压vdd。

10.进一步的,所述第三级放大包括第一巴伦blun_1、第四电容c4、第三电阻r3、第三nmos管m3、第五电容c5、第四电阻r4、第四nmos管m4、偏置电路三和第二巴伦blun_2;第三电容c3的第二端连接第一巴伦blun_1的单端输入端,第一巴伦blun_1的差分输出第一端口连接第四电容c4的第一端、第三电阻r3的第一端及第三nmos管m3的栅极,第一巴伦blun_1的差分输出第二端口连接第五电容c5的第一端、第四电阻r4的第一端及第四nmos管m4的栅极,第三电阻r3的第二端及第四电阻r4的第二端连接至偏置电路三的输出端;第三nmos管m3的源极接地,第四nmos管m4的源极接地,第三nmos管m3的漏极和第五电容c5的第二端连接第二巴伦blun_2的差分输入第二端口,第四nmos管m4的漏极和第四电容c4的第二端连接第二巴伦blun_2的差分输入第一端口,第二巴伦blun_2的差分输入端中间抽头连接至电源电压vdd,第二巴伦blun_2的单端输出端为功率放大器的输出端rf_out。

11.进一步的,第三nmos管m3和第四nmos管m4的单指栅长、栅宽和总指数相同,第三nmos管m3和第四nmos管m4的指数是第二nmos管m2的2倍。

12.进一步的,第二nmos管m2和第一nmos管m1的单指栅长和栅宽相同,第二nmos管m2的指数是第一nmos管m1的2倍。

13.进一步的,偏置电路一、偏置电路二、偏置电路三以及偏置电路四的电路结构相同,均包括一个nmos管m和一个电阻r;该nmos管m的源极接地,该nmos管m的栅极和该nmos管m的漏极短接,该nmos管m的漏极接i_in端,该nmos管m的栅极连接电阻r的第一端,电阻r的第二端连接i_out端。

14.进一步的,偏置电路一、偏置电路二、偏置电路三以及偏置电路四均与多路带隙基

准电流源连接,由多路带隙基准电流源提供镜像电流。

15.本发明的有益效果:1、本发明方案,在具有温补功能的功率放大器的输出端口rf_out并联一个电阻,通过该电阻把射频信号传输至工作在亚阈值区晶体管的输入端,经过该晶体管产生dc以及高次谐波分量,最后经过rc低通滤波后,输出检波电压vout,即可检测到功率放大器的幅值变化,具有温补功能的功率放大器使放大器增益、放大器输出功率和检波器输出电压在高低温(

‑

55℃~+85℃)状态下波动很小,本申请电路结构简单、面积小、成本低、性能优良,能够实现宽动态范围、低温度敏感度,为硅基小型化片上集成检波功能的cmos功率放大器芯片提供了一个解决方案;2、本发明方案,所述功率放大器采用的是三级放大电路结构,第一级放大电路和第二级放大电路的偏置电路都是和温度成正比的电流源相连接,第三级放大电路和与温度无关的电流源相连接,从而来补偿高低温状态下增益波动和输出功率波动的问题;3、本发明方案,偏置电路四为检波管第五nmos管m5提供和温度成负斜率的偏压,来补偿高低温状态下检测功率波动的问题,使功率检测器中的第五nmos管m5工作在亚阈值区域,能够降低功耗。

附图说明

16.图1为本发明的片上集成检波功能的cmos功率放大器芯片电路原理图;图2为本发明的片上集成检波功能的cmos功率放大器芯片偏置电路原理图;图3为本发明的片上集成检波功能的cmos功率放大器芯片在高低温(

‑

55℃~+85℃)状态下的幅频特性曲线;图4为本发明的片上集成检波功能的cmos功率放大器芯片在高低温(

‑

55℃~+85℃)状态下的功率随频率变化曲线;图5为本发明的片上集成检波功能的cmos功率放大器芯片在高低温(

‑

55℃~+85℃)状态下功率检测结果曲线。

17.图中:r3和r4电阻值一样,c6和c7电容值一样,m3和m4管子的栅长、栅宽和指数一样。

具体实施方式

18.为了更清楚地说明本发明,下面结合优选实施例和附图对本发明做进一步的说明。本领域技术人员应当理解,下面所具体描述的内容是说明性的而非限制性的,不应以此限制本发明的保护范围。

19.本发明的说明书和权利要求书及上述附图中的属于“第一”、“第二”等是用于区别不同的对象,而不是用于描述特定顺序。此外,术语

“ꢀ

包括”和

“ꢀ

具有”以及它们任何变形,意图在于覆盖不排他的包含。例如包含了一系列步骤或单元的过程、方法、系统、产品或设备没有限定于已列出的步骤或单元,而是可选地还包括没有列出的步骤或单元,或可选地还包括对于这些过程、方法或设备固有的气体步骤或单元。

20.如图1所示,为本发明片上集成检波功能的cmos功率放大器芯片的电路原理图,在具有温补功能的功率放大器的输出端口rf_out并联一个电阻r5,通过该电阻r5把射频信号

传输至工作在亚阈值区的晶体管m5的输入端,经过该晶体管m5产生dc以及高次谐波分量,最后经过r9和c7构成的rc低通滤波后,输出检波电压vout,即可检测到功率放大器的幅值变化。

21.偏置电路一、偏置电路二、偏置电路三、偏置电路四(也即图1中的偏置1、偏置2、偏置3和偏置4)的内部电路结构如图2所示,该偏置电路包括一个nmos管子m和一个电阻r。该nmos管m的源极接地,该nmos管m的栅极和该nmos管m的漏极短接,该nmos管m的漏极接i_in端,该nmos管m的栅极连接电阻r的第一端,电阻r的第二端连接i_out端。该偏置电路分别与放大器中的nmos管和检波器中的nmos管构成电流镜。

22.多路带隙基准电流源分别为偏置1、偏置2、偏置3和偏置4提供镜像电流。

23.第一路电流源的大小可以通过4bit控制位a1<0:3>来控制,第一路电流源的斜率可以通过4bit控制位b1<0:3>来控制。

24.第二路电流源的大小可以通过4bit控制位a2<0:3>来控制,第二路电流源的斜率可以通过4bit控制位b2<0:3>来控制。

25.第三路电流源的大小可以通过4bit控制位a3<0:3>来控制,第三路电流源的斜率可以通过4bit控制位b3<0:3>来控制。

26.第四路电流源的大小可以通过4bit控制位a4<0:3>来控制,第四路电流源的斜率可以通过4bit控制位b4<0:3>来控制。

27.如图1所示,功率放大器的输入端rf_in通过第一电容c1连接至第一电感l1的第一端,第一电感l1的第二端连接第一电阻r1的第一端及第一nmos管m1的栅极,第一电阻r1的第二端连接至偏置1,第一nmos管m1的源极连接第二电感l2的第一端,第二电感l2的第二端接地,第一nmos管m1的漏极连接第三电感l3的第一端及第四电感l4的第一端,第三电感l3的第二端连接电源电压vdd,第四电感l4的第二端接第二电容c2的第一端,第二电容c2的第二端连接第二电阻r2的第一端及第二nmos管m2的栅极,第二电阻r2的第二端连接至偏置2,第二nmos管m2的源极连接第五电感l5的第一端,第五电感l5的第二端接地,第二nmos管m2的漏极连接第六电感l6的第一端及第三电容c3的第一端,第六电感l6的第二端连接电源电压vdd,第三电容c3的第二端连接第一巴伦blun_1的单端输入端。

28.第一巴伦blun_1的差分输出第一端口连接第四电容c4的第一端、第三电阻r3的第一端及第三nmos管m3的栅极,第一巴伦blun_1的差分输出第二端口连接第五电容c5的第一端、第四电阻r4的第一端及第四nmos管m4的栅极,第三电阻r3的第二端及第四电阻r4的第二端连接至偏置3。

29.第三nmos管m3的源极接地,第四nmos管m4的源极接地,第三nmos管m3的漏极和第五电容c5的第二端连接第二巴伦blun_2的差分输入第二端口,第四nmos管m4的漏极和第四电容c4的第二端连接第二巴伦blun_2的差分输入第一端口,第二巴伦blun_2的差分输入端中间抽头连接至电源电压vdd,第二巴伦blun_2的单端输出端为功率放大器的输出端rf_out。

30.功率检测器的输入端通过第三电阻r5连接功率放大器的输出端rf_out,第五电阻r5的第二端连接第六电容c6的第一端,第六电容c6的第二端连接第六电阻r6的第一端及第五nmos管m5的栅极,第六电阻r6的第二端接至偏置4,第五nmos管m5的源极接地,第五nmos管m5的漏极连接第七电阻r7的第一端及第九电阻r9的第一端,第七电阻r7的第二端连接第

一pmos管p1的漏极,第一pmos管p1的栅极连接第八电阻r8的第一端,第一pmos管p1的源极连接电源电压vdd,第八电阻r8的第二端连接控制电压vg_tr。第九电阻r9的第二端为检测电压输出端口,同时连接第七电容c7的第一端,第七电容c7的第二端接地。

31.本发明实施例中,功率放大器共三级放大,也就是由三级放大电路组成,可以实现高低温(

‑

55℃~+85℃)状态下增益波动在

±

0.5db范围内,同时还保证输出功率波动在

±

0.15db范围内。

32.其中,第一级放大为共源极放大器,其中第一电容c1为隔直作用,第一电感l1为输入匹配电路,第二电感l2提供负反馈回路,起稳定作用,第三电感l3为电源电路和输出匹配电路。

33.偏置1为第一nmos管m1提供和温度成正斜率的偏压,使第一nmos管m1工作在ab类放大区,提供足够的增益以及高低温增益补偿。

34.第二级放大为共源极放大器,其中第二电容c2为隔直作用,第四电感l4和第三电感l3共同构成第二级放大输入端和第一级放大输出端的级间匹配电路,第五电感l5提供负反馈回路,起稳定作用,第六电感l6为电源电路和输出匹配电路,第三电容c3为隔直作用;偏置2为第二nmos管m2提供和温度成正斜率的偏压,使第二nmos管m2工作在ab类放大区,第二nmos管m2和第一nmos管m1的单指栅长和栅宽相同,第二nmos管m2的指数是第一nmos管m1的2倍,提供足够的增益、高低温增益补偿和输出功率。

35.第三级放大为采用变压器巴伦功率合成的差分放大器。

36.第一巴伦blun_1和第六电感l6共同构成第三级放大输入端和第二级放大输出端的级间匹配电路,同时第一巴伦blun_1把一路单端信号转化为两路差分信号。

37.偏置3为第三nmos管m3和第四nmos管m4提供不随温度变化的偏压,使第三nmos管m3和第四nmos管m4工作在ab类放大区,同时使第三级放大的增益不随温度变化,从而保证第三级放大器的输出功率也不随温度变化。

38.其中,第三nmos管m3和第四nmos管m4的单指栅长、栅宽和总指数相同,第三nmos管m3和第四nmos管m4的指数是第二nmos管m2的2倍。第四电容c4和第五电容c5为中和电容,提高差分放大器的稳定性。

39.第二巴伦blun_2把两路差分信号转化为一路单端信号,实现功率合成的目的。

40.如图3所示为本发明所述的一种小型化片上集成检波功能的cmos功率放大器芯片实施例的仿真结果,其工作频率为14ghz~15 ghz,在不同温度下该功率放大器(

‑

55℃、25℃和85℃)的增益曲线,高低温状态下增益波动在

±

0.5db左右,很好的实现了增益温度补偿功能。

41.如图4所示为本发明所述的一种小型化片上集成检波功能的cmos功率放大器芯片实施例的仿真结果,其工作频率为14ghz~15 ghz,在不同温度下该功率放大器(

‑

55℃、25℃和85℃)的功率曲线,高低温状态下功率波动在

±

0.15db左右,很好的实现了功率温度补偿功能。

42.第五电阻r5在功率放大器的输出端rf_out和功率检测器输入端的中间,把放大器输出端到检波器输入端的功率作一定的衰减,既要保证为功率检测器提供足够的输入电压,同时又要对功率放大器的输出端rf_out的功率和驻波影响足够的小。

43.功率检测器输入端的第六电容c6为隔直电容,偏置4为检波管第五nmos管m5提供

和温度成负斜率的偏压,使第五nmos管m5工作在亚阈值区域,同时保证在高低温(

‑

55℃~+85℃)状态下检测到的电压不变。

44.第五nmos管m5的漏极通过第七电阻r7和第一pmos管p1连接电源电压vdd,其中第一pmos管p1的栅压是通过电压vg_tr来控制导通或关闭。

45.当系统为发射状态时,电压vg_tr为低电平,第一pmos管p1导通,第五nmos管m5的电源电压导通,检波电路正常工作。

46.当系统为接收状态时,电压vg_tr为高电平,第一pmos管p1关闭,第五nmos管m5的电源电压断开,检波电路停止工作。

47.当射频信号输入时,经过检波管m5,产生dc以及高次谐波分量,再经过rc低通滤波网络,最后输出直流或低频信号,即可检测到射频信号的幅值变化。

48.如图5所示为本发明所述的一种小型化片上集成检波功能的cmos功率放大器芯片实施例检波的仿真结果,由图5可知,在高低温(

‑

55℃~+85℃)状态下,当rf_out为14dbm左右时,

‑

55℃、+25℃和+85℃状态下输出电压有一个交叉点,高低温状态下输出检波电压波动在

±

0.03v左右,很好的实现了功率温度补偿功能。由图5可知,功率检测器的最大检测功率为22dbm,动态范围为

‑

3dbm~22dbm。

49.第五nmos管m5工作在亚阈值区使得功耗极低,同时此方案的一个显著特点是能检测的功率值非常高。

50.本发明所述的片上集成检波功能的cmos功率放大器芯片电路的有益效果是:电路结构简单、面积小、成本低、性能优良,能够实现宽动态范围、低温度敏感度,为硅基小型化片上集成检波功能的cmos功率放大器芯片提供了一个解决方案。

51.显然,本发明的上述实施例仅仅是为清楚地说明本发明所作的举例,而并非是对本发明的实施方式的限定,对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动,这里无法对所有的实施方式予以穷举,凡是属于本发明的技术方案所引伸出的显而易见的变化或变动仍处于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1