一种超宽频段晶体驱动电路的制作方法

1.本发明涉及集成电路技术领域,尤其涉及一种晶体驱动电路,特别是涉及一种超宽频段晶体驱动电路。

背景技术:

2.晶体驱动器自上世纪20年代问世以来,其理论研究与制造水平都得到了飞速发展,各项性能指标显著提升。作为一种时钟频率源,与其他类型的振荡器相比,晶体振荡器以其优异的q值、频率精度、稳定度等,广泛应用于军工以及民用消费电子领域。而在集成电路领域,为了使晶体频率信号有效、合理地传输至芯片核心,io接口集成电路地作用至关重要。

3.随着对晶体驱动电路性能要求越来越高,不管是32.768khz(低频)晶体驱动电路,还是几mhz乃至几十mhz(中高频)晶体驱动电路,都是设计者探索的方向。但是现有的晶体驱动电路中,不管是低频32.768k、还是中高频,都是相互独立于不同的芯片中。若同一颗芯片需要同时支持低频晶振和中高频晶振,即使两个频率不会同时存在于芯片系统中,也需要在芯片内为两个晶振分别提供晶体驱动电路、封装引脚以及外挂电阻,这样会导致芯片的面积增大、可利用的封装引脚减少,成本大大增加。

技术实现要素:

4.本发明的主要目的在于提供一种超宽频段晶体驱动电路,旨在同一颗芯片同时支持低频晶振和中高频晶振。

5.为实现上述目的,本发明提供一种超宽频段晶体驱动电路,用以驱动低频晶体或中高频晶体、并输出低频或中高频晶体振荡信号;所述晶体驱动电路包括反馈电阻模块、起振电路模块和第一选择器; 所述反馈电阻模块连接于所述起振电路模块,所述起振电路模块连接于所述第一选择器、外部晶体和外部负载端;所述第一选择器连接于所述起振电路模块;所述起振电路模块还包括低频起振子电路和中高频起振子电路,分别用于启动低频晶体和中高频晶体;当需要启动外部晶体时,所述驱动电路根据所需频率连接对应晶体;发送控制信号至所述反馈电阻模块,以将所述反馈电阻模块的阻值配置到启动晶体所需的阻值;发送选择信号至所述起振电路模块,以接通所述起振电路模块中的其中一起振子电路,同时关闭另一起振子电路;第一选择器根据选择信号将选择后的晶体振荡信号输出至后续电路。

6.优选地,所述驱动电路还包括输出模块,所述输出模块连接于所述第一选择器,用于增加所述晶体振荡信号的驱动能力并输出。

7.优选地,所述驱动电路还包括触发器模块,所述触发器模块连接于所述输出模块和所述外部负载端,用于将外部输入的时钟信号发送至所述输出模块。

8.优选地,所述触发器模块为施密特触发器。

9.优选地,所述晶体驱动电路还包括第二选择器,所述第二选择器连接于所述触发

器模块和所述第一选择器,用于将所述触发器模块或所述第一选择器的信号输出。

10.优选地,所述驱动电路还包括寄存器模块,所述寄存器模块配置所述控制信号以调整所述反馈电阻模块的阻值、配置所述选择信号以选择接通低频起振子电路或中高频起振子电路;所述寄存器模块还配置第一启动信号或第二启动信号,以分别启动低频起振子电路或中高频起振子电路。

11.优选地,寄存器模块还发送旁路控制信号至所述触发器模块、所述起振电路模块和所述第二选择器,用以接通所述触发器模块和所述晶体驱动电路的外部负载端、关闭所述起振电路模块,并使所述第二选择器选择输出外部时钟信号。

12.优选地,所述反馈电阻模块包括多个串联的电阻,多个串联的电阻分别并联有开关,控制信号通过控制开关的接通或断开,以调整反馈电阻模块的阻值。

13.优选地,所述反馈电阻模块的阻值范围为500kohm~10mohm。

14.本发明技术方案通过将低频起振子电路和中高频起振子电路集成在同一颗芯片中,同时通过调整反馈电阻模块的阻值,以满足起振电路模块所需的反馈电阻,再通过选择信号分别接通低频或中高频起振子电路,分别启动低频或中高频晶体,满足芯片系统对不同时钟的要求,减小了电路设计面积、减少了引脚的使用和外挂电阻,大大减小了芯片面积和芯片成本。

附图说明

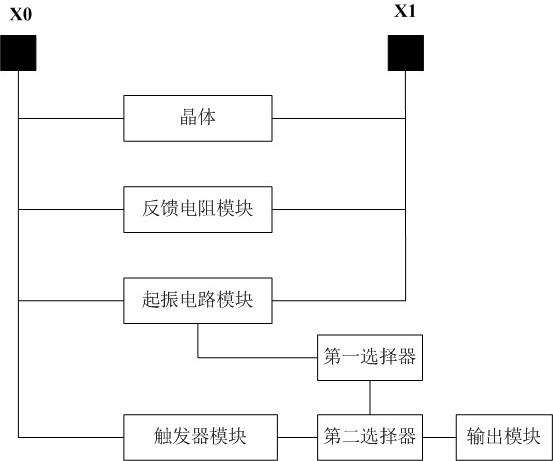

15.图1为本发明超宽频段晶体驱动电路的电路原理图;图2为本发明超宽频段晶体驱动电路的电路示意图;图3为本发明超宽频段晶体驱动电路中反馈电阻模块的电路示意图。

16.本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

17.具体实施方式

18.应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

19.下面结合附图对本发明进一步说明。

20.本发明实施例提供一种超宽频段晶体驱动电路,支持低频晶体和中高频晶体驱动,用于为芯片系统提供不同频率的时钟信号。

21.如图1、图2所示,该超宽频段晶体驱动电路用以驱动低频晶体或中高频晶体、并输出低频或中高频晶体振荡信号,包括反馈电阻模块、起振电路模块和第一选择器mux1;所述反馈电阻模块连接于所述起振电路模块,所述起振电路模块连接于所述第一选择器mux1、外部晶体和外部负载端x0、x1;所述第一选择器mux1连接于所述起振电路模块;所述起振电路模块还包括低频起振子电路和中高频起振子电路,分别用于启动低频晶体和中高频晶体;当需要启动外部晶体时,所述驱动电路根据所需时钟频率连接对应晶体;发送控制信号rf_sel至所述反馈电阻模块,以将所述反馈电阻模块的阻值配置到启动晶体所需的阻值;发送选择信号reg_sel至所述起振电路模块,以接通所述起振电路模块中的其中一起振子电路,同时关闭另一起振子电路;第一选择器mux1根据选择信号reg_sel将选择后的晶体振荡信号输出至后续电路。

22.由于本发明实施例将低频起振子电路和中高频起振子电路集成在同一颗芯片中,同时通过调整反馈电阻模块的阻值,以满足起振电路模块所需的反馈电阻,再通过选择信号reg_sel分别接通低频或中高频起振子电路,分别启动低频或中高频晶体,满足芯片系统对不同时钟的要求,减小了电路设计面积、减少了引脚的使用和外挂电阻,大大减小了芯片面积和芯片成本。

23.具体地,起振电路模块中的低频起振子电路和中高频起振子电路的具体电路结构,可使用现有技术已公开的任意起振电路,只需分别对应满足启动低频晶体或中高频晶体的要求即可。

24.在具体实施例中,当芯片系统需要低频时钟信号时,晶体驱动电路在其外部负载端x0、x1连接低频晶体、并对地挂上负载。发送控制信号rf_sel至反馈电阻模块,以将反馈电阻模块的阻值配置到启动低频晶体所需的阻值。发送选择信号reg_sel至低频起振子电路,以接通低频起振子电路,同时关闭中高频起振子电路。低频晶体启动后,第一选择器mux1根据选择信号reg_sel选择将低频晶体振荡信号输出至后续电路。

25.在另一具体实施例中,当芯片系统需要中高频时钟信号时,晶体驱动电路在其外部负载端x0、x1连接中高频晶体、并对地挂上负载。发送控制信号rf_sel至反馈电阻模块,以将反馈电阻模块的阻值配置到启动中高频晶体所需的阻值。发送选择信号reg_sel至中高频起振子电路,以接通中高频起振子电路,同时关闭低频起振子电路。中高频晶体启动后,第一选择器mux1根据选择信号reg_sel选择将中高频晶体振荡信号输出至后续电路。

26.在优选实施例中,如图2所示,晶体驱动电路还包括寄存器模块,所述寄存器模块配置所述控制信号rf_sel以调整所述反馈电阻模块的阻值、配置所述选择信号reg_sel以选择接通低频起振子电路或中高频起振子电路;所述寄存器模块还配置第一启动信号32k_iopsel或第二启动信号mf_iopsel,以分别启动低频起振子电路或中高频起振子电路。具体的,第一启动信号32k_iopsel用以启动低频起振子电路、第二启动信号mf_iopsel用以启动中高频起振子电路。

27.在具体实施例中,当芯片系统需要低频时钟信号时,晶体驱动电路在其外部负载端x0、x1连接低频晶体、并对地挂上负载。寄存器模块发送控制信号rf_sel至反馈电阻模块,以将反馈电阻模块的阻值配置到启动低频晶体所需的阻值。寄存器模块发送选择信号reg_sel至低频起振子电路,以接通低频起振子电路,同时关闭中高频起振子电路。寄存器模块发送第一启动信号32k_iopsel至低频起振子电路,以使低频起振子电路正常工作、启动低频晶体。寄存器模块发送选择信号reg_sel至第一选择器mux1,第一选择将低频晶体振荡信号选择输出至后续电路。具体地,第一启动信号32k_iopsel为合适的低频晶体起振电流。该起振电流可根据晶体具体的频率和实际电路工艺等条件进行设置。

28.在另一具体实施例中,当芯片系统需要中高频时钟信号时,晶体驱动电路在其外部负载端x0、x1连接中高频晶体、并对地挂上负载。寄存器模块发送控制信号rf_sel至反馈电阻模块,以将反馈电阻模块的阻值配置到启动中高频晶体所需的阻值。寄存器模块发送选择信号reg_sel至中高频起振子电路,以接通中高频起振子电路,同时关闭低频起振子电路。寄存器模块发送第二启动信号mf_iopsel至中高频起振子电路,以使中高频起振子电路正常工作、启动中高频晶体。寄存器模块发送选择信号reg_sel至第一选择器mux1,第一选择器mux1将中高频晶体振荡信号选择输出至后续电路。具体地,第二启动信号mf_iopsel为

合适的中高频晶体起振电流。该起振电流可根据晶体具体的频率和实际电路工艺等条件进行设置。

29.在优选实施例中,如图1、图2所示,所述驱动电路还包括输出模块vout,所述输出模块vout连接于所述第一选择器mux1,用于增加所述晶体振荡信号的驱动能力并输出。输出模块vout用于将驱动电路的晶体振荡信号输出,并增加驱动能力。

30.在优选实施例中,如图1、图2所示,所述驱动电路还包括触发器模块buffer,所述触发器模块buffer连接于所述输出模块vout和所述外部负载端x0、x1,用于将外部输入的时钟信号发送至所述输出模块vout。外部输入的时钟信号通过外部负载端x0、x1输入,替代晶体驱动时钟,可根据实际需要输入,灵活性大大增加。具体的,所述触发器模块buffer为施密特触发器。

31.进一步的,如图1、图2所示,所述晶体驱动电路还包括第二选择器mux2,所述第二选择器mux2连接于所述触发器模块buffer和所述第一选择器mux1,用于将所述触发器模块buffer或所述第一选择器mux1的信号输出。

32.更进一步的,寄存器模块还发送旁路控制信号byp至触发器模块buffer、起振电路模块和第二选择器mux2,用以接通触发器模块buffer和晶体驱动电路的外部负载端x0、x1,关闭起振电路模块,并使第二选择器mux2选择输出外部时钟信号。

33.当芯片系统需要晶体驱动时钟以外的时钟信号时,可以选择由外部输入时钟信号。具体的,寄存器模块输入旁路控制信号byp至起振电路模块、触发器模块buffer和第二选择器mux2,以关闭起振电路模块,外部时钟信号由外部负载端x0、x1输入至触发器模块buffer,再由触发器模块buffer发送至第二选择器mux2,第二选择器mux2选择外部时钟信号输出。在具体实施例中,外部时钟信号可根据芯片系统具体的时钟需求输入。

34.在本发明实施例中,实际使用时,可根据需要的频率选择外部晶体或外部时钟信号,通过寄存器模块控制反馈电阻模块的阻值大小,再通过寄存器模块选择是由低频起振子电路工作还是由中高频起振子电路工作。

35.在优选实施例中,反馈电阻模块包括多个串联的电阻,多个串联的电阻分别并联有开关,控制信号rf_sel通过控制开关的接通或关断,以调整反馈电阻模块的阻值。

36.进一步地,反馈电阻模块的阻值范围为500kohm~10mohm。在具体实施例中,低频晶体一般指32.768k晶体,对应的,该晶体工作时的反馈电阻阻值一般为10mohm;中高频晶体一般为4~32m晶体,对应的,该晶体工作时的反馈电阻阻值一般为500kohm~2mohm。在其他实施例中,可根据用户需求连接需要的晶体,再根据晶体设置反馈电阻模块的阻值范围,具体的阻值可根据实际使用情况进行预先调整设置。

37.具体地,如图3所示,反馈电阻模块包括依次串联的第一电阻r1、第二电阻r2、第三电阻r3和第四电阻r4,第一电阻s1的另一端和第四电阻s4的另一端还连接于起振电路模块。第二电阻r2并联有第一开关s1、第三电阻r3并联有第二开关s2、第四电阻r4并联有第三开关s3,寄存器模块分别发送控制信号rf_sel至第一开关s1、第二开关s2和第三开关s3,以分别控制其接通或关断。具体的,第一控制子信号rf_sel<1>用于控制第一开关s1的接通或关断;第二控制子信号rf_sel<2>用于控制第二开关s2的接通或关断;第三控制子信号rf_sel<3>用于控制第三开关s3的接通或关断。预设第一电阻r1、第二电阻r2、第三电阻r3和第四电阻r4的阻值依次为500kohm、1.5mohm、3mohm和5mohm;当需要驱动低频32.768k晶体时,

接通所有电阻,即可满足低频晶体工作时的需要反馈电阻阻值;当需要驱动中高频4~32m晶体,在接通对应阻值的电阻,即可满足中高频晶体工作。在另一些实施例中,电阻和开关的数量也可根据实际需求预先设置。

38.具体实施例:如图2所示,在第一具体实施例中,晶体驱动电路用于32.768k晶体驱动电路时:在晶体驱动电路的外部负载端x0、x1之间连接32.768k晶体;外部负载端x0和x1对地挂12pf的负载;通过寄存器模块发送控制信号rf_sel将反馈电阻模块的阻值配置到10mohm;令寄存器模块输出的旁路控制信号byp为0,选择晶体振荡模式,即:关闭触发器模块buffer、接通起振电路模块、并使得第二选择器mux2选择输出起振电路模块的振荡信号;通过寄存器模块发送选择信号reg_sel选择低频起振子电路工作、同时关闭中高频起振子电路,再通过寄存器模块发送第一启动信号32k_iopsel配置合适的32.768k晶振起振电流;此时,晶振开始工作,输出模块vout输出32.768k时钟信号。

39.如图2所示,在第二具体实施例中,晶体驱动电路用于中高频晶体驱动电路时候,以32m晶体为例:在晶体驱动电路的外部负载端x0、x1之间连接32m晶体;外部负载端x0和x1对地挂12pf的负载;通过寄存器模块发送控制信号rf_sel将反馈电阻模块的阻值配置到500kohm;令寄存器模块输出的旁路控制信号byp为0,选择晶体振荡模式,即:关闭触发器模块buffer、接通起振电路模块、并使得第二选择器mux2选择输出起振电路模块的振荡信号;通过寄存器模块发送选择信号reg_sel选择中高频起振子电路工作、同时关闭低频起振子电路,再通过寄存器模块发送第二启动信号mf_iopsel配置合适的32m晶振起振电流;此时,晶振开始工作,输出模块vout输出32m时钟信号。

40.如图2所示,在第三具体实施例中,当芯片系统需要外部输入时钟信号,即晶振bypass模式:令寄存器模块输出的旁路控制信号byp为1,选择外部时钟输入模式,旁路控制信号byp的优先级很高,当它为1时候,不管是低频起振子电路还是中高频起振子电路都不会工作;从晶体驱动电路的外部负载端x0输入时钟信号,这时候晶振不工作,在输出模块vout输出的时钟等于外部负载端x0输入的时钟,即,此时外部负载端x0输入10mhz时钟,输出模块vout也输出10mhz时钟。

41.该模式下,可支持任意频率的时钟信号输入,便于为芯片系统提供更多的时钟频率选择,增加芯片系统的灵活性。

42.应当理解的是,以上仅为本发明的优选实施例,不能因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1