多通道射频接口模块的制作方法

1.本实用新型涉及数据采集技术领域,尤其涉及多通道射频接口模块。

背景技术:

2.现有技术中,在进行模拟数据采集的时候,大多数是简单的通过ad转换器把模拟信号转换成数字信号,而不考虑采样信号同步和精度的问题,在信号不经过预处理的情况下,采样数据容易出现严重偏离的现象,使得数据的价值降低;传统的采样设备接口单一,通用性差,数据处理速度低,导致灵敏度低,无法实现数据高速传输。

技术实现要素:

3.本实用新型的目的就在于为了解决上述问题而提供多通道射频接口模块,包括多个sma接口、多个mgc模块、zynq模块、时钟模块、调试及方波输出接口、sfp光信号接口、存储器、网络接口与io接口;zynq模块设置有模拟输入端与数字输出端;sma接口通过mgc模块与模拟输入端相连;zynq模块的pl端与调试及方波输出接口相连;zynq模块的pl端与sfp光信号接口相连;zynq模块的ps端与存储器、网络接口、io接口相连;时钟模块与zynq模块相连。

4.优选的,所述调试及方波输出接口包括连接器驱动、矩形连接器;zynq模块的pl端通过连接器驱动与矩形连接器相连。

5.优选的,所述时钟模块包括模拟时钟模块与数字时钟模块;模拟时钟模块与zynq模块的ps端相连;数字时钟模块与zynq模块的pl端相连。

6.优选的,所述模拟时钟模块包括时钟发生器、温补晶振、外部时钟、压控振荡器、时钟缓冲器与宽带频率合成器;温补晶振、外部时钟、压控振荡器分别与第一时钟发生器相连;时钟发生器通过时钟缓冲器与宽带频率合成器相连;宽带频率合成器与模拟输入端相连。

7.优选的,所述数字时钟模块包括时钟芯片与第二时钟发生器;时钟芯片通过第二时钟发生器与数字输出端相连。

8.优选的,所述mgc模块包括多级串联的低噪声宽带放大器与数控衰减器。

9.优选的,所述低噪声宽带放大器为hmc8411;数控衰减器为七位数控衰减pe43712。

10.优选的,所述zynq模块为rf soc芯片;rf soc芯片的ps端为arm处理器与rf数据转换器;zynq模块的pl端为fpga模块;arm处理器与fpga模块之间连接有数据总线。

11.本实用新型的有益效果在于:本实用新型能够实现多通道模拟信号的同步采样;具有信号放大功能;支持用户的二次开发,并预留足够资源;具有光纤数据导出的功能;能够通过千兆网上传板卡状态;能够输出1路lvttl信号;具有低噪放的特点,提高了灵敏度。

附图说明

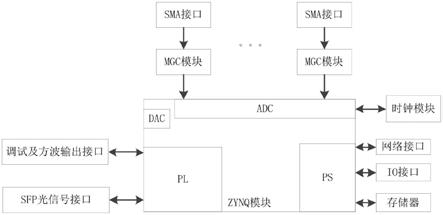

12.图1是本实用新型的原理图;

13.图2是具体实施方式的原理图;

14.图3是mgc模块的原理图;

15.图4是时钟模块的原理图;

16.图5是电源模块的原理图。

具体实施方式

17.下面结合附图对本实用新型作进一步说明:

18.如附图1所示,本实用新型多通道射频接口模块,包括多个sma接口、多个mgc模块、zynq模块、时钟模块、调试及方波输出接口、sfp光信号接口、存储器、网络接口与io接口;zynq模块设置有模拟输入端与数字输出端;sma接口通过mgc模块与模拟输入端相连;zynq模块的pl端与调试及方波输出接口相连;zynq模块的pl端与sfp光信号接口相连;zynq模块的ps端与存储器、网络接口、io接口相连;时钟模块与zynq模块相连。

19.优选的,所述调试及方波输出接口包括连接器驱动、矩形连接器;zynq模块的pl端通过连接器驱动与矩形连接器相连。

20.优选的,所述时钟模块包括模拟时钟模块与数字时钟模块;模拟时钟模块与zynq模块的ps端相连;数字时钟模块与zynq模块的pl端相连。

21.优选的,所述模拟时钟模块包括时钟发生器、温补晶振、外部时钟、压控振荡器、时钟缓冲器与宽带频率合成器;温补晶振、外部时钟、压控振荡器分别与第一时钟发生器相连;时钟发生器通过时钟缓冲器与宽带频率合成器相连;宽带频率合成器与模拟输入端相连。

22.优选的,所述数字时钟模块包括时钟芯片与第二时钟发生器;时钟芯片通过第二时钟发生器与数字输出端相连。

23.优选的,所述mgc模块包括多级串联的低噪声宽带放大器与数控衰减器。

24.优选的,所述低噪声宽带放大器为hmc8411;数控衰减器为七位数控衰减pe43712。

25.优选的,所述zynq模块为rf soc芯片;rf soc芯片的ps端为arm处理器与rf数据转换器;zynq模块的pl端为fpga模块;arm处理器与fpga模块之间连接有数据总线。

26.本实用新型能够实现多路模拟数据采集,通过多个sma接口分别通过mgc模块连接zynq模块的模拟输入端。mgc模块,包括多级串联的低噪声宽带放大器与数控衰减器,能够实现压制整机噪声,低噪放的性能能够提高接收机系统的灵敏度和噪声系数,另外天线接收到的微弱射频信号经过低噪放放大后也便于后端增益控制电路的正常工作。选用低噪声宽带放大器hmc8411,在系统所述100mhz

‑

6ghz频率范围内,具有较佳的增益平坦特性。

27.接收的射频信号要经过多级低噪声放大、数控衰减器,每个模块都有固有噪声,前端器件的级联,使两级的噪声都加到系统中,导致噪声功率向输出增长。采用低噪声放大器与数控衰减器组合级联的方式,同样选择低插损的数控衰减器,实现0

‑

60db的增益控制。依据公式其恶化程度远小于一级放大器的噪声,故系统的噪声系数主要由第一级低噪声放大器的噪声系数决定,0衰减的情况下,理论噪声小于4db。数控衰减器选用7位数控衰减pe43712。

28.zynq模块的ps端连接usb接口、dp83867以太网控制器、emmc存储器、ddr4存储器;dp83867收发器连接rj45网络接口。

29.zynq模块的pl端通过连接器驱动连接矩形连接器j30j

‑

15zk,zynq模块的pl端连

接sfp光信号接口。

30.zynq模块的ps端的以太网控制器支持gmii、rgmii和sgmii模式。

31.如附图4所示,采用一片倍频时钟,产生多种不同频率的时钟,然后用这些时钟进行fanout输出多路的方式;再考虑到fpga的gty参考输入时钟以及dsp的各种输入时钟对时钟的相位抖动要求较高,选用844n255时钟芯片;在25mhz输入下可产生156.25mhz、125mhz、100mhz、50mhz和25mhz的时钟信号。该芯片的时钟输出优化了周期到周期抖动,具有非常低的相位噪声,适合用作dsp与fpga高速gty的时钟。844n255输出的100mhz采用一片ics85408进行fanout,输出8组100mhzlvds时钟,其中4路分别接到dsp的coreclk、ddrclk、passclk和pcieclk,2路接到zu28dr的ps端pcieclk和usbclk,剩余的2路接到zu28dr的io全局时钟;156.25mhz时钟采用一片ics85408进行fanout,输出5路lvds时钟,其中2路分别接dsp的srioclk和hyperlinkclk,剩下的3路分别接到zu28dr的pl端gty bank128、129和130的参考输入时钟1上;125mhz时钟采用一片ics85408进行fanout,输出5路lvds时钟,其中1路接到zu28dr的ps端的sataclk,剩下的4路分别接到pl端gty bank128、129、130和131的参考时钟输入0上;ics844n255直接倍频输出的50mhz接连到xc6slx25的bank3的全局时钟上。

32.如附图5所示,外部供电输入采用vpx连接器的12v,zynq模块的soc内核1.0v均需要大功率供电,本板考虑保留较大的供电余量,采用具有3相供电的大功率电源ltc3773,共需要3片,每项最大供电电流可达20a,最大电流取决于外部mos管的选择,可以两相组合最大输出电流可达40a;其余电源可采用单项输出的tps54622和tlv62130,其中前者输出电流最大为6a,后者输出电流最大3a。ltc3773每相输出、tps54622和tlv62130均有独立的en管脚,便以做整板的上电时序。模拟部分供电采用超低噪声低压差的ldo芯片,根据电流大小选用tps7a8300和adp1762。ddr的终端电源采用专用ddr电源tps51200。

33.输入频率范围:2200.5mhz~2500.5mhz,步进1khz;有用信号带宽;20mhz;采样率:1.7ghz~2.2ghz可配置;通道数:12;输入功率范围:

‑

105~

‑

20dbm;mgc范围:20~60db;sfdr(adc):>60db;噪声系数:<12db;信噪比恶化:<0.5db;三阶交调抑制:>64db;相位噪声:<

‑

60dbc/hz@100hz;<

‑

75dbc/hz@1khz;<

‑

85dbc/hz@10khz;<

‑

95dbc/hz@100khz;<

‑

105dbc/hz@1mhz;杂波抑制:>60dbc;二次、三次谐波抑制:<

‑

60db;群时延:线性变化<1ns,24小时绝对时延变化<1ns;通道隔离度:>60dbc;fpga处理资源要求:不低于xc7v690t;光纤接口:两路输出,线速率不低于6.25gbps。

34.本实用新型能够实现12通道模拟信号的同步采样;具有信号放大功能;支持用户的二次开发,并预留足够资源;具有光纤数据导出的功能;能够通过千兆网上传板卡状态;能够输出1路lvttl信号;具有低噪放的特点,提高了灵敏度。

35.本实用新型的技术方案不限于上述具体实施例的限制,凡是根据本实用新型的技术方案做出的技术变形,均落入本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1