硅基宽带高速可重构正交分频器的制作方法

1.本发明属于射频无线收发前端集成电路技术领域,具体涉及一种工作频率覆盖低频(~mhz)至毫米波(~30ghz)频段,基于硅基工艺的宽带高速可重构正交分频器,尤其涉及一种带开关调节的负载时钟前馈cmos宽带高速动态电流模逻辑dcml(dynamic current mode logic)分频器结构,主要应用于毫米波无线收发前端系统中。

背景技术:

2.硅基毫米波技术的不断发展给人们的生活带来了日新月异的变化,各种不同的通信标准协议和技术应用层出不穷。其中,无线收发前端系统不但需要满足越来越严苛的延迟、传输速率、功耗、成本和可靠性等要求,而且还能够同时支持多种通信协议及未来软件无线电定义。分频器作为无线收发前端中频率源中不可或缺的组成部分,其主要功能就是将振荡器产生的最高频率一分为二,并根据需要正交输出,该模块的性能好坏将直接影响整个链路的相位噪声及功耗等,其性能的优劣对整个无线通信系统产生直接的影响。现代光纤通信网络使用波分复用技术极大地提升了网络传输容量。基于硅基液晶技术的波长选择开关使光纤网络运营商在网络节点处可以灵活地调度各个波长信道,让光纤通信网络在波长级具有可重构性,大幅地降低了网络的传输和运营成本,已经成为了现代光纤通信网络的核心组件。同时,基于硅基液晶(liquid crystal on silicon,lcos)技术的波长选择开关wss具有高端口数目,且支持灵活栅格(flex-grid)标准,可大幅提升全光通信网络的传输容量,波长路径切换不需要传统的光-电-光转换过程,极大地提升了网络的可重构性和鲁棒性,已成为业界的主流选择。现代wss需要支持灵活栅格,匹配wdm信道的频谱宽度。wss通常具有1个输入端口和n个输出端口,可以将任意的输入wdm信道分配至任意输出光纤端口。将多个1

×

n wss共同封装在一个模块中也成为近些年来业界发展的趋势。随着光纤通信网络的传输速率和频谱效率越来越高,其对wss光学性能的要求也日益提升,以保证通信质量和传输距离。现代高速光纤通信网络采用偏振复用方式对激光器进行调制,因此wss模块需保证不同偏振态的光束在光学系统中经历相同的插入损耗。滤波通带特性(passband):wss属于一种可调滤波器,滤波通带特性是其重要的技术指标。在roadm网络中,一个wdm信号通常需要经过15个结点(即30个wss)才可以抵达目的地。因此,即使是细微的wss滤波通带特性差异也会在网络层引起巨大的信道质量差异。具有不同滤波通带特性的wss的通带曲线。经过30次级联后,滤波通带宽度发生了明显的收窄,传输信道的一部分频谱会被过滤掉,影响该波长通信质量。同时,wss部署环境的湿度、气压等差别相对较大。因此,通信应用对lcos器件的可靠性提出了更高的要求。由于超高速主动硅基功能的开发,如全光开关等,仍然是一大挑战。因此目前常用毫米波宽带高速分频器。分频器在cpld/fpga设计中使用频率比较高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源,但是对于要求奇数倍分频(如3、5等)、小数倍(如2.5、3.5等)分频、占空比50%的应用场合却往往不能满足要求。

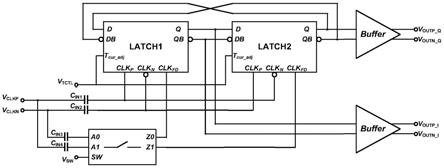

3.目前,常用的毫米波宽带高速分频器主要包括以下三种类型:1、注入锁定分频器

(ilfd);2、可再生分频器(rfd);3、电流模逻辑分频器(cml)。相对于前两种类型,cml分频器具有尺寸小、分频范围宽、灵敏度高和能够提供正交输出等优点。传统cml结构主要采用:1)静态电阻负载。负载r

l

通常采用无源电阻或偏置在饱和区的pmos管实现。在该结构中,r

l

阻值大小的选择需要综合考虑最高工作频率和输出摆幅之间的关系。阻值过大会导致rc时间常数增大,相应的充放电时间增长,从而影响最高工作频率;负载电阻阻值过小,则有可能不能正常驱动后级电路,必须增加偏置电流,导致功耗增加;这一对矛盾关系使得传统静态负载结构往往不能有一个较大的最高工作频率。2)动态电阻负载。为了克服静态负载结构中最高工作频率受限的问题,该结构中负载pmos管栅压直接受时钟信号ck动态控制,使其在采样模式下阻值小,放电快,保持模式下组织大,输出摆幅高,从而提高了最高工作频率。然而,该结构存在分频范围较窄的不足,难以满足毫米波宽带应用甚至全频带多通信协议应用的需求。

4.综上所述,基于cmos工艺设计一种宽带高速低功耗的正交分频器对于改善频率源性能,推动毫米波无线收发前端系统朝低成本、高集成、低功耗发展具有重要的意义。

技术实现要素:

5.本发明的目的是针对现有技术存在的不足之处,提供一种宽分频范围、高工作频率、低功耗的硅基宽带高速可重构正交分频器。

6.本发明的上述目的可以通过以下措施来得到,一种硅基宽带高速可重构正交分频器,包括:带尾电流偏置阵列的主从两个差分锁存器latch1和latch2,一个负载时钟前馈射频开关单元以及分别连接i/q两路的差分输出缓冲器buffer,其特征在于,主差分锁存器latch1的数据信号差分输出端q、qb依次连接从差分锁存器latch2的数据信号差分输入端d、db;从差分锁存器latch2数据信号输出端q、qb连接缓冲器buffer1,latch1数据信号输出端q、qb连接另一缓冲器buffer2;负载时钟前馈射频开关单元通过时钟信号差分输出端口z0和z1分别连接主从两个差分锁存器的时钟馈入端口clk

fd

;外部差分时钟信号v

clkp

和v

clkn

通过电容c

in1

、c

in2

传输至主从两个差分锁存器的时钟信号差分输入端口clk

p

和clkn,同时外部差分时钟信号v

clkp

和v

clkn

通过起隔直作用的电容c

in1

,c

in2

和c

in3

、c

in4

,将时钟输入差分信号clk

p

和clk传输至负载时钟前馈射频开关单元时钟信号差分输入端口a0和a1;主从两个差分锁存器的偏置电流源阵列控制端t

cur_adj

相互连接,并通过外部数字信号v

tctl

控制整个分频器工作时的时钟输入为正弦波或方波的信号,输出信号通过自带的缓冲器buffer直接驱动后级电路。

7.本发明相比于现有技术具有如下有益效果:本发明两个差分锁存器均由三组差分nmos对管,一组pmos负载管以及电流值可变的偏置尾电流源阵列构成。如图2所示,m

s1

和m

s2

为采样对管,m

h1

和m

h2

为正反馈交叉耦合锁存对管,m1和m2为时钟信号输入对管。当差分锁存器差分正相时钟信号输入端口clk

p

为高电平时,m1开启,m2关闭,采样对管工作,对输入信号进行采样;当差分锁存器差分正相时钟信号输入端口clk

p

为低电平时,m1关闭,m2开启,锁存对管工作,锁定采样得到的数据。pmos负载管m

p1

和m

p2

将电流信号转换成电压信号输出。整个差分锁存器的尾电流偏置采用电流值可变的偏置电流源阵列,可根据输入信号的频率大小并通过外部控制,切换不同的电流镜比例,从而降低功耗。

8.本发明采用负载时钟前馈射频开关电路单元通过外部v

sw

信号控制,其内部构成采用π型差分结构,该开关电路配合pmos负载管m

p1

和m

p2

构成一对随时钟变化的动态负载,决定了差分锁存器的工作状态,能够提供良好的开关隔离度。当输入信号频率较高时,开关导通,差分锁存器工作为动态,具有更高的工作频率;差分锁存器被认为是动态差分锁存器,在相同的输入幅度下,分频器最高工作频率提高;反之,开关断开,差分锁存器工作为静态,差分锁存器被认为是静态差分锁存器,分频器拥有更宽的分频范围。该时钟前馈射频开关电路配合差分锁存器中电流源阵列能够根据输入信号情况合理重构分频器状态,使其降低功耗的同时具有更高的工作频率和更宽的分频范围。

9.本发明采用如图4所示的一个带电阻反馈的两级结构输出buffer,该buffer前后端连接有隔直电容c

in1

和隔直电容c

in2

和c

in3

,c

in4

,中间两级放大单元采用pmos/nmos互补反相器结构,晶体管类型均为lvt管。电容对c

in1

,c

in2

和c

in3

,c

in4起隔直作用

,使差分锁存器及时钟前馈射频开关单元模块内部偏置不受输入时钟影响。相比共源放大电路,该buffer能够在保证高速工作的情况下,使输出信号摆幅接近满摆幅。与传统cml结构分频器相比,本发明:1、可以在保证较高工作频率的情况下具有更宽的分频范围;2、能够根据输入信号频率重构分频器状态,使其具有更低的功耗;3、高速满摆幅互补输出buffer,可以直接驱动后级电路,一定程度上降低了系统设计复杂度。

10.本发明在分频器的主从差分锁存器中采用pmos晶体管作为动态电阻,通过引入时钟信号前馈改变其栅极电压大小实现负载阻抗变化,动态调节其支路电流从而提高分频器的最高工作频率;通过在负载时钟前馈链路中引入射频开关单元,使其能够根据输入时钟频率高低进行控制:在输入时钟频率低时,开关关断,不引入时钟前馈从而保证了分频器的最低工作频率,使其具有更宽的分频范围。此外,整个差分锁存器的偏置电流采用了电流值可变的偏置电流源阵列,通过外部控制切换不同的电流镜比例实现。通过这种设计,该分频器能够在一个较宽的工作频率范围内保持一个合理的工作电流范围,从而降低了动态功耗。本发明具有一定的可重构性,不仅具有工作频率高,分频范围广,而且在一定程度上降低了系统功耗,弥补了传统cml分频器的不足,输出端自带的缓冲buffer更是可以直接驱动后级电路,使其适用于高速的毫米波收发系统前端。一方面,在分频器的锁存器中采用pmos管作为负载,通过引入时钟信号前馈改变其栅极电压实现阻抗变化,动态调节其支路电流从而提高分频器的最高工作频率;另一方面,在负载时钟前馈链路中引入射频开关,当输入时钟频率低时,关断时钟前馈从而保证分频器的最低工作频率,使其分频范围更宽。此外,锁存器的偏置电流采用可变电流源阵列,通过控制切换不同的电流镜比例,使分频器能够在较宽的工作频率范围内保持耕地的动态工作电流。本发明具有一定的可重构性,不仅工作频率高,分频范围广,而且功耗更低,弥补了传统cml分频器的不足,输出端缓冲buffer更是可以直接驱动后级电路,使其适用于高速毫米波收发前端。

附图说明

11.图1为本发明的硅基宽带高速可重构正交分频器原理框图;图2为图1分频器中的差分锁存器单元电路原理图;图3为图1分频器中的负载时钟前馈射频开关电路原理图;图4为图1分频器中的输出buffer电路原理图。

12.下面结合附图对本发明进一步详细说明。

具体实施方式

13.参阅图1。在以下描述的示意性优选实施例中,一种硅基宽带高速可重构正交分频器,包括:带尾电流偏置阵列的主从两个差分锁存器latch1和latch2,一个负载时钟前馈射频开关单元以及分别连接i/q两路的差分输出缓冲器buffer,其中,主差分锁存器latch1的数据信号差分输出端q、qb依次连接从差分锁存器latch2的数据信号差分输入端d、db;从差分锁存器latch2数据信号输出端q、qb连接缓冲器buffer1,latch1数据信号输出端q、qb连接另一缓冲器buffer2;负载时钟前馈射频开关单元通过时钟信号差分输出端口z0和z1分别连接主从两个差分锁存器的时钟馈入端口clk

fd

;外部差分时钟信号v

clkp

和v

clkn

通过电容c

in1

、c

in2

传输至主从两个差分锁存器的时钟信号差分输入端口clk

p

和clkn,同时外部差分时钟信号v

clkp

和v

clkn

通过起隔直作用的电容c

in1

,c

in2

和c

in3

、c

in4

,将时钟输入差分信号clk

p

和clk传输至负载时钟前馈射频开关单元时钟信号差分输入端口a0和a1;主从两个差分锁存器的偏置电流源阵列控制端t

cur_adj

相互连接,并通过外部数字信号v

tctl

控制整个分频器工作时的时钟输入为正弦波或方波的信号,输出信号通过自带的缓冲器buffer直接驱动后级电路。

14.两个差分锁存器对输入信号进行采样,将时钟输入差分信号clk

p

和clkn通过电容器c

in1

、c

in2

并联电容器c

in3

、c

in4

,将该正弦波或方波信号时钟信号传输到负载时钟前馈射频开关单元,对时钟频率高低进行控制;在输入时钟频率低时,开关导通,主差分锁存器latcch1工作为动态,当差分锁存器差分正相时钟信号输入端口clk

p

为高电平时,开关断开,从差分锁存器latcch2工作为静态,主从差分锁存器输出端自带的缓冲器buffer直接驱动后级电路。

15.开关单元模块内部偏置不受输入时钟影响。主从两个差分锁存器的偏置电流源阵列控制端t

cur_adj

相互连接并通过外部数字信号v

tctl

控制。整个分频器工作时的时钟输入信号可为正弦波或方波信号,输出信号通过自带的缓冲器buffer能够直接驱动后级电路。

16.参阅图2。在可选的实施例中,差分锁存器由三组差分nmos对管,一组pmos负载管以及电流值可变的偏置尾电流源阵列组成。其中,第一组差分nmos对管m

s1

和m

s2

为采样对管,第二组nmos对管m

h1

和m

h2

为正反馈交叉耦合锁存对管,第三组nmos对管m1和m2为时钟信号输入对管;pmos对管m

p1

和m

p2

为有源负载对管,pmos负载管m

p1

和m

p2

将电流信号转换成电压信号输出。当差分锁存器差分正相时钟信号输入端口clk

p

为高电平时,m1开启,m2关闭,采样对管工作,对输入数据信号进行采样;当差分锁存器差分正相时钟信号输入端口clk

p

为低电平时,m1关闭,m2开启,锁存对管工作,锁定采样得到的数据,尾电流偏置大小改变通过外部控制信号t

cur_adj

切换不同的电流镜比例实现。

17.对于采样管m

s1

,其漏极连接锁存管m

h2

漏极与锁存管m

h1

栅极后接入负载管m

p1

漏极,构成所属差分锁存器信号输出端qb;对于采样管m

s2

,其漏极连接锁存管m

h1

漏极与锁存管m

h2

栅极后接入负载管m

p2

漏极,构成所属差分锁存器信号输出端q。负载对管m

p1

和m

p2

的栅极偏置电压经过大电阻r1=10k后由外部电压v

bias

提供;c1为负载管m

p1

和m

p2

栅极的隔直电容,一端连接m

p1

和m

p2

栅极,一端构成差分锁存器的时钟馈入端口clk

fd

;第一组nmos对管m

s1

和m

s2

源极短接后连接第三组nmos对管中m1的漏极,其栅极分别构成所述差分锁存器的信号输入

端口d和db,第二组nmos对管m

h1

和m

h2

源极短接后连接第三组nmos对管中m2的漏极;第三组nmos对管m1和m2源极短接后接入尾电流管m

t1

的漏极,其栅极分别构成所述差分锁存器的时钟信号输入端口clk

p

和clkn,其中,晶体管m1的栅极处还并联有一个大电阻r2,电阻另一端连接外部偏置电压v

cas

给晶体管m1栅极提供直流偏置。

18.对于所述差分锁存器中电流值可调的尾电流源阵列,其由晶体管m

t1

、m

t2

…mtn-1

、m

tn

,电容c

de

,电阻r

de

以及使能开关enn构成,其中,晶体管m

t1

、m

t2

…mtn-1

、m

tn

构成基本电流镜结构:可调谐镜像源部分晶体管m

t2

…mtn-1

、m

tn

栅极分别短接各自漏极后通过电阻r

de

连接至晶体管m

t1

的栅极;大电阻r

de

=10k,防止外部电源杂波通过电流镜进入差分锁存器内部;滤波电容c

de

并联在晶体管m

t1

栅极,采用有源nmos管实现,有利于减小芯片尺寸;在电容c

de

与电阻r

de

之间增加使能开关enn,闭合时强制晶体管m

t1

、m

t2

…mtn-1

、m

tn

栅极电压短路到地,使差分锁存器停止工作。该尾电流源阵列内部包含多种不同的电流镜比例(可配置为1:1:1:1或1:2:4:8等),通过外部信号t

cur_adj

控制晶体管m

t2

…mtn-1

、m

tn

漏极处开关实现。当输入时钟信号频率降低时,减小尾电流镜像比例,从而降低功耗。

19.对于所述第一差分锁存器latch1或第二差分锁存器latch2,其工作时包括采样和锁存两个阶段。当差分锁存器差分正相时钟信号输入端口clk

p

为高电平时,尾电流管m1开启,其偏置电流完全从采样管m

s1

或采样管m

s2

所在支路流过,采样管m

s1

栅极输入端口d的输入数据经负载管m

p1

完成电流信号到电压信号的转换并传输至采样管m

s1

漏极输出端口qb,采样管m

s2

栅极输入端口db的输入数据经负载管m

p2

完成电流信号到电压信号的转换并传输至采样管m

s2

漏极输出端口q,从而实现采样过程;同时,由于差分锁存器差分负相时钟信号clkn为低电平,尾电流m2管关断,所以采样过程中,正反馈交叉耦合锁存对管m

h1

和m

h2

关闭而不起作用。当差分锁存器差分正相时钟信号输入端口clk

p

为低电平时,尾电流m1管关断使采样对管m

s1

和m

s2

关断而不起作用;同时,由于差分锁存器差分负相时钟信号输入端口clkn为高电平,尾电流m2管开启,其偏置电流完全从锁存对管m

h1

和m

h2

流过,采样管m

s1

漏极输出端口qb的输出数据和采样管m

s2

漏极输出端口q的输出数据通过锁存对管m

h1

和m

h2

的正反馈作用而被保持,从而实现锁存过程。

20.对于所述第一差分锁存器latch1或第二差分锁存器latch2,当差分输入正相时钟信号时,clk

p

为高电平,第一差分锁存器latch1进入采样阶段,第二差分锁存器latch2进入锁存阶段。这样,第二差分锁存器latch2的采样管m

s1

漏极输出端口qb的输出数据由于保持锁存状态而不变,并作为第一差分锁存器latch1的差分正相数据信号输入端口d,同时经第一差分锁存器latch1采样后直接传输到第一差分锁存器latch1差分负相数据信号输出端口qb;第二差分锁存器latch2的差分正相数据信号输出端口q与第二差分锁存器latch2的差分负相数据信号输出端口qb的工作情况类似。

21.对于所述第一差分锁存器latch1或第二差分锁存器latch2,当差分输入负相时钟信号时,clk

p

为低电平,第一差分锁存器latch1进入锁存阶段,第二差分锁存器latch2进入采样阶段。第一差分锁存器latch1的差分正相信号输出端口q的输出数据仍然由于保持锁存状态而不变,并作为第二差分锁存器latch2差分正相数据信号输入端口d的输入数据,同时经第二差分锁存器latch2采样后直接传输到第二差分锁存器latch2差分负相数据信号输出端口qb;第一差分锁存器latch1的差分负相数据信号输出端口qb与第一差分锁存器latch1的差分正相数据信号输出端口q的输出数据的工作情况类似。

22.如图3所示的一个负载时钟前馈射频开关电路,其中,整个开关采用π型差分结构,由nmos管m

n1

、m

n2

、m

n3

构成,能提供更为良好的开关隔离度;端口a0和a1为时钟信号差分输入,端口z0和z1为时钟信号差分输出,分别连接nmos管m

n1

、m

n2

的漏极和栅极,同时,在这两处分别并联电阻r

p1

,r

p2

以及r

p3

,r

p4

到地以保证射频开关左右两端电位明确;外部信号v

sw

分别通过数字缓冲器buf.,以及数字缓冲器buf.串联数字反相器inv.连接至nmos管m

n1

、m

n2

的栅极以及nmos管m

n3

的栅极,以增大外部信号的驱动能力使晶体管m

n1

、m

n2

、m

n3

的导通/关断更为彻底。当v

sw

=“1”,负载时钟前馈射频开关中晶体管m

n1

,m

n2

导通,m

n3

关断,差分时钟信号顺利通过,差分锁存器工作为动态;当v

sw

=“0”,负载时钟前馈射频开关中晶体管m

n1

,m

n2

关断,m

n3

导通,差分时钟信号无法通过,少量经由晶体管m

n1

,m

n2

泄漏的时钟信号也由于m

n3

的导通而被消除,差分锁存器工作为静态。

23.参阅图4。缓冲器buffer包含前后端连接的隔直电容c

b1

和隔直电容c

b2

。中间两级放大单元采用pmos/nmos互补反相器结构,晶体管类型均为lvt管。反馈电阻r

b1

和r

b2

分别跨接在前后两个放大单元的输入与输出端之间,以提高工作带宽。相比共源放大电路,该buffer能够在保证高速工作的情况下,使输出信号摆幅接近满摆幅。

24.由于该分频器在工作时涉及:1、负载是否受时钟信号动态控制,2、尾电流偏置大小,两方面的状态调节重构,因此具体实施方式还需要从这两个方面来具体描述。首先,硅基宽带高速可重构正交分频器的基本自由振荡频率由图2中负载pmos管的栅极直流电压v

bias

确定。通过调整其值改变负载pmos管的基本阻值,从而使分频器的负载rc常数改变;此外,为了进一步提高分频器的最高工作频率,引入了一个负载时钟前馈射频开关。当该开关导通时,差分时钟信号通过输入端口a0、a1进入,并流过输出端口z0、z1再叠加至负载pmos管栅极,即工作在dcml模式。此时,pmos负载栅极电压由时钟动态控制,使其在采样模式下阻值减小,放电快;保持模式下阻值增大,输出摆幅提高,从而提高分频器的最高工作频率,其次,为了降低分频器的功耗,流经该宽带高速可重构正交分频器采样管m

s1

和m

s2

以及正反馈交叉耦合锁存对管m

h1

和m

h2

的电流可根据工作频率预先确定并通过外部信号t

cur_adj

控制切换不同的电流镜比例实现。工作电流的预先确定需要结合最高工作频率和输出幅度共同确定。

25.与传统cml分频器采用纯静态负载或纯动态负载不同,该宽带高速可重构正交分频器负载情况可根据实际应用调节重构,通过外部信号v

sw

控制。当v

sw

=“1”,负载时钟前馈射频开关中晶体管m

n1

,m

n2

导通,m

n3

关断,差分锁存器工作为动态,具有更高的工作频率;当v

sw

=“0”,负载时钟前馈射频开关中晶体管m

n1

,m

n2

关断,m

n3

导通,差分锁存器工作为静态,具有更宽的分频范围。

26.对于所述第一锁存器latch1或第二锁存器latch2,其工作时包括采样和锁存两个阶段。当锁存器差分正相时钟信号输入端口clk

p

为高电平时,尾电流管m1开启,其偏置电流完全从采样管m

s1

或采样管m

s2

所在支路流过,采样管m

s1

栅极输入端口d的输入数据经负载管m

p1

完成电流信号到电压信号的转换并传输至采样管m

s1

漏极输出端口qb,采样管m

s2

栅极输入端口db的输入数据经负载管m

p2

完成电流信号到电压信号的转换并传输至采样管m

s2

漏极输出端口q,从而实现采样过程;同时,由于锁存器差分负相时钟信号clkn为低电平,尾电流m2管关断,所以采样过程中,正反馈交叉耦合锁存对管m

h1

和m

h2

关闭而不起作用。当锁存器差分正相时钟信号输入端口clk

p

为低电平时,尾电流m1管关断使采样对管m

s1

和m

s2

关断而不起

作用;同时,由于锁存器差分负相时钟信号输入端口clkn为高电平,尾电流m2管开启,其偏置电流完全从锁存对管m

h1

和m

h2

流过,采样管m

s1

漏极输出端口qb的输出数据和采样管m

s2

漏极输出端口q的输出数据通过锁存对管m

h1

和m

h2

的正反馈作用而被保持,从而实现锁存过程。对于所述第一锁存器latch1或第二锁存器latch2,当差分输入正相时钟信号时,clk

p

为高电平,第一锁存器latch1进入采样阶段,第二锁存器latch2进入锁存阶段。这样,第二锁存器latch2的采样管m

s1

漏极输出端口qb的输出数据由于保持锁存状态而不变,并作为第一锁存器latch1的差分正相数据信号输入端口d,同时经第一锁存器latch1采样后直接传输到第一锁存器latch1差分负相数据信号输出端口qb;第二锁存器latch2的差分正相数据信号输出端口q与第二锁存器latch2的差分负相数据信号输出端口qb的工作情况类似。

27.对于所述第一锁存器latch1或第二锁存器latch2,当差分输入负相时钟信号时,clk

p

为低电平,第一锁存器latch1进入锁存阶段,第二锁存器latch2进入采样阶段。第一锁存器latch1的差分正相信号输出端口q的输出数据仍然由于保持锁存状态而不变,并作为第二锁存器latch2差分正相数据信号输入端口d的输入数据,同时经第二锁存器latch2采样后直接传输到第二锁存器latch2差分负相数据信号输出端口qb;第一锁存器latch1的差分负相数据信号输出端口qb与第一锁存器latch1的差分正相数据信号输出端口q的输出数据的工作情况类似。

28.以上所述仅为本发明的较佳实施例,对本发明而言仅仅是说明性的,而非限制性的。本专业技术人员理解,在本发明权利要求所限定的精神和范围内可对其进行许多改变、修改、甚至等效,但都将落入本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1