像素阵列基板的制作方法

[0001]

本发明涉及一种像素阵列基板,且特别涉及一种包含扫描线以及数据线的像素阵列基板。

背景技术:

[0002]

由于显示面板具有体积小、辐射低等优点,显示面板已经普遍地被应用在各式各样的电子产品中。在现有的显示面板中,通常会于显示区的外围保留大面积的驱动电路区来设置驱动电路,并通过驱动电路来控制子像素。然而,位于显示区外侧的驱动电路区使显示面板具有很宽的边框,并限缩了产品的屏占比。随着科技的进步,消费者对显示面板外观的要求越来越高,为了要提高消费者的购买意愿,如何增加显示面板的屏占比已经成为目前各家厂商欲解决的问题之一。

[0003]

一些厂商将显示面板中的驱动电路集中于显示区的同一侧,借此缩小驱动电路区的面积。然而,前述方法需要于显示区中设置转线结构来调整信号的传递路径。这些转线结构容易使子像素的电压分布不均匀,导致画面产生亮度不均匀的问题。

技术实现要素:

[0004]

本发明提供一种像素阵列基板,能解决显示画面亮度不均匀的问题。

[0005]

本发明的至少一实施例提供一种像素阵列基板,包括多条扫描线、多条传输线、多条数据线以及多个子像素。扫描线、传输线以及数据线位于基板上。第1级扫描线至第n级扫描线沿着第一方向延伸,其中n为大于3的整数。第1级传输线至第n级传输线,沿着第二方向延伸,且分别电性连接至第1级扫描线至第n级扫描线。数据线沿着第二方向延伸。各子像素电性连接至对应的一条扫描线以及对应的一条数据线。第一子像素重叠于第3级传输线。第一子像素的第一开关元件电性连接至第3级扫描线,且第一开关元件的漏极与第一开关元件的栅极之间的电容为cgd1。第二子像素重叠于第3+x级传输线,其中x为小于3的整数。第二子像素的第二开关元件电性连接至第3级扫描线,且第二开关元件的漏极与第二开关元件的栅极之间的电容为cgd2。第三子像素重叠于第3-x级传输线。第三子像素的第三开关元件电性连接至第3级扫描线。第三开关元件的漏极与第三开关元件的栅极之间的电容为cgd3。cgd2大于cgd3大于cgd1。

[0006]

本发明的至少一实施例提供一种像素阵列基板,包括基板、驱动电路、多条扫描线、多条传输线、多条数据线、第一子像素以及第二子像素。扫描线位于基板上,且包括第1级扫描线至第n级扫描线。第1级扫描线至第n级扫描线沿着第一方向延伸,其中n为大于3的整数。传输线位于基板上,且包括第1级传输线至第n级传输线。第1级传输线至第n级传输线沿着第二方向延伸,且第1级传输线至第n级传输线分别电性连接驱动电路至第1级扫描线至第n级扫描线。第1级传输线至第n级传输线中的其中一者电性连接至第1级扫描线至第n级扫描线中的其中一者,且驱动电路与第1级扫描线至第n级扫描线中的其中一者之间的第1级传输线至第n级传输线中的其中一者的长度为y1。第1级传输线至第n级传输线中的其中

另一者电性连接至第1级扫描线至第n级扫描线中的其中另一者,且驱动电路与第1级扫描线至第n级扫描线中的其中另一者之间的第1级传输线至第n级传输线中的其中另一者的长度为y2,其中长度y2大于长度y1。数据线位于基板上,且沿着第二方向延伸。第一子像素包括第一开关元件以及电性连接至第一开关元件的第一像素电极。第一开关元件电性连接至第1级传输线至第n级传输线中的其中一者,且第一开关元件的漏极与栅极的重叠面积为a1,第一开关元件的栅极与第一像素电极的重叠面积为b1。第二子像素包括一第二开关元件以及电性连接至第二开关元件的第二像素电极。第二开关元件电性连接至第1级传输线至第n级传输线中的该其中另一者,且第二开关元件的漏极与栅极的重叠面积为a2,第二开关元件的栅极与第二像素电极的重叠面积为b2。面积a1>面积a2,及/或面积b1>面积b2。

附图说明

[0007]

图1是依照本发明的一实施例的一种像素阵列基板的俯视图。

[0008]

图2是依照本发明的一实施例的一种像素阵列基板的显示区俯视图。

[0009]

图3是依照本发明的一实施例的一种像素阵列基板的扫描线信号波形图。

[0010]

图4a至图4f分别是依照本发明的一实施例的不同个子像素俯视图。

[0011]

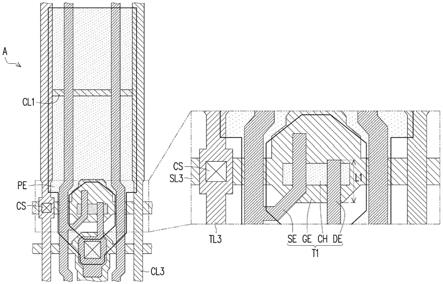

图5是沿着图4a的线aa’的剖面示意图。

[0012]

图6是依照本发明的一实施例的一种像素阵列基板的扫描线信号以及像素电极信号波形图。

[0013]

图7a和图7b分别是依照本发明的一实施例的不同个子像素俯视图。

[0014]

图8a和图8b分别是依照本发明的一实施例的不同个子像素俯视图。

[0015]

图9是依照本发明的一实施例的一种像素阵列基板的显示区俯视图。

[0016]

图10是依照本发明的一实施例的一种像素阵列基板的俯视图。

[0017]

图11a和图11b分别是依照本发明的一实施例的不同个子像素俯视图。

[0018]

图12是依照本发明的一实施例的一种像素阵列基板的俯视图。

[0019]

附图标记说明:

[0020]

10、20、30、40:像素阵列基板

[0021]

a、c、d、e:子像素

[0022]

aa:显示区

[0023]

ba:周边区

[0024]

cl1、cl2、cl3:共用信号线

[0025]

ch:通道层

[0026]

cs:转接结构

[0027]

dl:数据线

[0028]

de:漏极

[0029]

dc、dr:驱动电路

[0030]

dr1、dr2:方向

[0031]

ep:延伸部

[0032]

ge:栅极

[0033]

gi:栅极绝缘层

[0034]

l、l1~l3、l5、l6、y1、y2、y3:长度

[0035]

n:标准子像素

[0036]

o:开口

[0037]

pe:像素电极

[0038]

pl:绝缘层

[0039]

sb:基板

[0040]

se:源极

[0041]

sl、sl1~sl5:扫描线

[0042]

t:标准开关元件

[0043]

tl、tl1~tl9、tlm、tla、tlb、tlc:传输线

[0044]

t1~t3、t5、t6:开关元件

[0045]

u:绝缘层

[0046]

w1、w2、x、x1:宽度

具体实施方式

[0047]

在整个说明书中,相同的附图标记表示相同或类似的元件。在附图中,为了清楚起见,放大了层、膜、面板、区域等的厚度。应当理解,当诸如层、膜、区域或基板的元件被称为“在另一元件上”或“连接另一元件”时,其可以直接在另一元件上或与另一元件连接,或者所述元件与所述另一元件中间可以也存在其他元件。相反,当元件被称为“直接在另一元件上”或“直接连接另一元件”时,所述元件与所述另一元件中间不存在其他元件。如本文所使用的,“连接”可以指物理及/或电性连接。再者,二元件互相“电性连接”或“耦合”可为二元件间存在其它元件。

[0048]

应当理解,尽管术语“第一”与“第二”等在本文中可以用于描述各种元件、部件、区域、层及/或部分,但是这些元件、部件、区域、及/或部分不应受这些术语的限制。这些术语仅用于将一个元件、部件、区域、层或部分与另一个元件、部件、区域、层或部分区分开。

[0049]

图1是依照本发明的一实施例的一种像素阵列基板的俯视图。图1示出了像素阵列基板的基板、扫描线、数据线、传输线以及驱动电路,并省略了其他构件。

[0050]

请参考图1,像素阵列基板10包括基板sb、扫描线sl、数据线dl、传输线tl以及驱动电路dc。扫描线sl、数据线dl、传输线tl以及驱动电路dc位于基板sb上。

[0051]

基板sb上具有显示区aa以及位于显示区aa外侧的周边区ba。驱动电路dc设置于周边区ba。扫描线sl位于显示区aa中,且沿着第一方向dr1延伸。数据线dl以及传输线tl沿着第二方向dr2延伸,且自驱动电路dc延伸至显示区aa中。每条传输线tl电性连接至对应的一条扫描线sl。在本实施例中,传输线tl通过转接结构cs而电性连接至对应的扫描线sl。

[0052]

图2是依照本发明的一实施例的一种像素阵列基板的显示区俯视图。举例来说,图2例如为图1的像素阵列基板10的显示区aa的局部放大示意图。

[0053]

请参考图2,像素阵列基板包括多条扫描线、多条传输线、多条数据线以及多个子像素。在本实施例中,像素阵列基板还包括沿着第一方向dr1延伸的共用信号线cl1、cl2以及沿着第二方向dr2延伸的共用信号线cl3。

[0054]

扫描线包括第1级扫描线sl1至第n级扫描线sln,其中n为大于3的整数。在图2仅绘

出了第1级扫描线sl1至第5级扫描线sl5,但本发明不以此为限。扫描线的数量可以依照需求而进行调整。在本实施例中,第1级扫描线sl1至第n级扫描线sln以及共用信号线cl1、cl2属于相同导电层(例如第一导电层)。

[0055]

传输线包括第1级传输线tl1至第n级传输线tln。在图2仅绘出了第1级传输线tl1至第5级传输线tl5,但本发明不以此为限。传输线的数量可以依照需求而进行调整。第1级传输线tl1至第n级传输线tln分别电性连接至第1级扫描线sl1至第n级扫描线sln。举例来说,第1级传输线tl1电性连接至第1级扫描线sl1,第2级传输线tl2电性连接至第2级扫描线sl2,第3级传输线tl3电性连接至第3级扫描线sl3,其他的传输线与扫描线以类似的方式电性连接。在本实施例中,第1级传输线tl1至第n级传输线tln、数据线dl以及共用信号线cl3属于相同导电层(例如第二导电层)。第一导电层与第二导电层之间夹有绝缘层,而转接结构cs贯穿前述绝缘层。

[0056]

各子像素电性连接至对应的一条扫描线以及对应的一条数据线。图2用于说明不同子像素的位置关系,子像素的结构可以参考图4a至图4f的实施例。

[0057]

请继续参考图2,在本实施例中,元件符号a标记了重叠于对应阶级的传输线的子像素。举例来说,电性连接至第3级扫描线sl3且重叠于第3级传输线tl3的子像素被元件符号a所标记,电性连接至第4级扫描线sl4且重叠于第4级传输线tl4的子像素被元件符号a所标记,其他元件符号a所标记的子像素以此类推。

[0058]

在本实施例中,元件符号b标记了重叠于后一阶级(post-stage)的传输线的子像素。举例来说,电性连接至第3级扫描线sl3且重叠于第4级传输线tl4的子像素被元件符号b所标记,电性连接至第4级扫描线sl4且重叠于第5级传输线tl4的子像素被元件符号b所标记,其他元件符号b所标记的子像素以此类推。

[0059]

在本实施例中,元件符号c标记了重叠于后两阶级的传输线的子像素。举例来说,电性连接至第3级扫描线sl3且重叠于第5级传输线tl5的子像素被元件符号c所标记,电性连接至第4级扫描线sl4且重叠于第6级传输线tl6的子像素被元件符号c所标记,其他元件符号c所标记的子像素以此类推。

[0060]

在本实施例中,元件符号d标记了重叠于前一阶级(pre-stage)的传输线的子像素。举例来说,电性连接至第3级扫描线sl3且重叠于第2级传输线tl2的子像素被元件符号d所标记,电性连接至第4级扫描线sl4且重叠于第3级传输线tl3的子像素被元件符号d所标记,其他元件符号d所标记的子像素以此类推。

[0061]

在本实施例中,元件符号e标记了重叠于前两阶级的传输线的子像素。举例来说,电性连接至第3级扫描线sl3且重叠于第1级传输线tl1的子像素被元件符号e所标记,电性连接至第4级扫描线sl4且重叠于第2级传输线tl2的子像素被元件符号e所标记,其他元件符号e所标记的子像素以此类推。

[0062]

图3是依照本发明的一实施例的一种像素阵列基板的扫描线信号波形图。

[0063]

请参考图2与图3,在本实施例中,对子像素进行预充电以使子像素能即时达到预定的电压。每级扫描线的充电时间会部分重叠于前级扫描线的充电时间以及后级扫描线的充电时间。举例来说,第3级扫描线sl3的充电时间t3部分重叠于第3+x级扫描线sl3+x的充电时间以及第3-x级扫描线sl3-x的充电时间,其中x为小于3的整数。在本实施例中,第3级扫描线sl3的充电时间t3部分重叠于第1级扫描线sl1的充电时间t1、第2级扫描线sl2的充

电时间t2、第4级扫描线sl4的充电时间t4以及第5级扫描线sl5的充电时间t5。在本时实施例中,各级扫描线的充电时间不重叠于超过其3级以上的扫描线的充电时间。举例来说,第3级扫描线sl3的充电时间t3不重叠于第6级扫描线sl6的充电时间t6。

[0064]

每条扫描线的预充电的时间可以依照需求而进行调整,换句话说,有多少条扫描线的充电时间彼此重叠可以依照需求而进行调整。

[0065]

在本实施例中,同一条扫描线所电性连接的多个子像素会重叠于不同条传输线,而不同条传输线上的信号彼此不同,因此,不同个子像素上可能会有亮度分布不均匀的问题。在一些实施例中,子像素a、子像素b、子像素c、子像素d以及子像素e具有补偿设计,借此消减亮度分布不均匀的问题,相关设计请参考后续实施例的说明。

[0066]

在本实施例中,不具有补偿设计的子像素被元件符号n所标记。在一些实施例中,标准子像素n所重叠的传输线的阶级与对应阶级的传输线相差较大。举例来说,电性连接至第1级扫描线sl1且重叠于第4级扫描线sl4的子像素可以被元件符号n所标记。在一些实施例中,标准子像素n重叠于共用信号线cl3而非传输线。

[0067]

图4a至图4f分别是依照本发明的一实施例的不同个子像素俯视图。图5是沿着图4a的线aa’的剖面示意图。

[0068]

请参考图2、图4a与图5,标准子像素n包括标准开关元件t以及像素电极pe,标准开关元件t包括栅极ge、通道层ch、源极se以及漏极de。

[0069]

栅极ge位于基板sb上,且电性连接至对应的扫描线。在本实施例中,以栅极ge电性连接至第3级扫描线sl3为例。通道层ch重叠于栅极ge,且通道层ch与栅极ge之间夹有栅极绝缘层gi。

[0070]

源极se以及漏极de电性连接至通道层ch,源极se电性连接至数据线dl。标准开关元件t的漏极de与标准开关元件t的栅极ge(或第3级扫描线sl1)之间的电容为cgd0。绝缘层pl设置于源极se以及漏极de上。在一些实施例中,绝缘层pl为彩色滤光层,并构成彩色滤光层于像素阵列上(color filter on array,coa)的结构,但本发明不以此为限。在其他实施例中,彩色滤光层设置于其他基板上。

[0071]

绝缘层u设置于绝缘层pl上,绝缘层u例如为有机材料或无机材料。像素电极pe设置于绝缘层u上,且通过贯穿绝缘层u以及绝缘层pl的开口o而电性连接至漏极de。

[0072]

虽然在本实施例中,在俯视图中,每个子像素的开口区位于对应的扫描线的上方,但本发明不以此为限。在其他实施例中,通过调整像素电极pe的延伸方向,使各子像素的开口区位于对应的扫描线的下方。

[0073]

标准子像素n重叠于共用信号线cl3及/或第m级传输线tlm,且标准子像素n中的第3级扫描线sl3亦重叠于共用信号线cl3及/或第m级传输线tlm其中1<m<n。在本实施例中,第m级传输线tlm(或第m级扫描线)的充电时间不与第3级扫描线sl3的充电时间重叠。

[0074]

请参考图4a与图4b,图4b的子像素a与图4a的标准子像素n有类似的结构,差异在于子像素a重叠于第3级传输线tl3,且子像素a的漏极de重叠于栅极ge的长度l1小于标准子像素n的标准开关元件t的漏极de重叠于栅极ge的长度l。

[0075]

在本实施例中,子像素a的开关元件t1的栅极ge电性连接至第3级扫描线sl3,且开关元件t1的漏极de与开关元件t1的栅极ge(或第3级扫描线sl3)之间的电容为cgd1。

[0076]

在本实施例中,开关元件t1的漏极de重叠于栅极ge的长度l1小于标准开关元件t

的漏极de重叠于栅极ge的长度l,使开关元件t1的漏极de与栅极ge之间的重叠面积小于标准开关元件t的漏极de与栅极ge之间的重叠面积。因此,开关元件t1的电容cgd1小于标准开关元件t的电容cgd0。

[0077]

子像素a除了开关元件t1的漏极de会与栅极ge产生电容cgd1之外,子像素a的像素电极pe也会与第3级传输线tl3之间产生电容cvg1。然而,标准子像素n的像素电极pe并非重叠于第3级传输线tl3,导致子像素a与标准子像素n容易出现亮度不一致的问题。在本实施例中,通过使开关元件t1的电容cgd1小于标准开关元件t的电容cgd0能够改善前述亮度不一致的问题。

[0078]

图6是依照本发明的一实施例的一种像素阵列基板的扫描线信号以及像素电极信号波形图。

[0079]

请参考图4a、图4b以及图6,子像素a以及标准子像素n电性连接至第3级扫描线sl3。在本实施例中,子像素a重叠于第3级传输线tl3,而标准子像素n重叠于第m级传输线tlm,其中1<m<n。

[0080]

第m级传输线tlm电性连接至第m级扫描线slm,且第m级扫描线slm的充电时间不重叠于第3级传输线tl3的充电时间。

[0081]

在图6中,子像素a的像素电极pe上具有电压p(a),标准子像素n的像素电极pe上具有电压p(n)。当启动第3级扫描线sl3时,子像素a的像素电极pe以及标准子像素n的像素电极pe开始充电。在关闭第3级扫描线sl3时(在时间范围x之中),子像素a的像素电极pe上的电压以及标准子像素n的像素电极pe上的电压会下降。

[0082]

当未对子像素a加上补偿设计时(即补偿前),子像素a的像素电极pe的电压下降的幅度会不同于标准子像素n的像素电极pe的电压下降的幅度,使得电压p(a)与电压p(n)在后续的电压保持阶段(holding time)时彼此不同,这容易导致显示面板亮度分布不均的问题。

[0083]

当对子像素a加上补偿设计时(即补偿后),由于子像素a的电容cgd1小于标准子像素n的电容cgd0,子像素a的像素电极pe在关闭第3级扫描线sl3时(在时间范围x之中)电压下降的程度能够接近标准子像素n的像素电极pe在电压下降的程度,使得电压p(a)与电压p(n)在后续的电压保持阶段(holding time)时彼此相近,借此改善显示面板亮度分布不均的问题。

[0084]

请参考图4a与图4c,图4c的子像素d与图4a的标准子像素n有类似的结构,差异在于子像素d重叠于第3-y级传输线tl3-y,且子像素d的漏极de重叠于栅极ge的长度l5小于标准子像素n的漏极de重叠于栅极ge长度l。在本实施例中,y等于1,且子像素d重叠于第2级传输线tl2。

[0085]

在本实施例中,子像素d的开关元件t5的栅极ge电性连接至第3级扫描线sl3,且开关元件t5的漏极de与开关元件t5的栅极ge(或第3级扫描线sl3)之间的电容为cgd5。

[0086]

开关元件t5的漏极de重叠于栅极ge的长度l5小于标准开关元件t的漏极de重叠于栅极ge的长度l,使开关元件t5的漏极de与栅极ge之间的重叠面积小于标准开关元件t的漏极de与栅极ge之间的重叠面积。因此,开关元件t5的电容cgd5小于标准开关元件t的电容cgd0。

[0087]

子像素d除了开关元件t5的漏极de会与栅极ge产生电容cgd5之外,子像素d的像素

电极pe也会与第2级传输线tl2之间产生电容cvg2。然而,标准子像素n的像素电极pe并非重叠于第2级传输线tl2,导致子像素d与标准子像素n容易出现亮度不一致的问题。在本实施例中,通过使开关元件t5的电容cgd5小于标准开关元件t的电容cgd0能够改善前述亮度不一致的问题。

[0088]

请参考图4b与图4c,开关元件t1的漏极de重叠于栅极ge的长度l1小于开关元件t5的漏极de重叠于栅极ge的长度l5,使开关元件t1的漏极de与栅极ge之间的重叠面积小于开关元件t5的漏极de与栅极ge之间的重叠面积。因此,开关元件t1的电容cgd1小于开关元件t5的电容cgd5。

[0089]

请参考图4a与图4d,图4d的子像素e与图4a的标准子像素n有类似的结构,差异在于子像素e重叠于第3-x级传输线tl3-x,且子像素e的漏极de重叠于栅极ge的长度l3小于标准子像素n的漏极de重叠于栅极ge的长度l。在本实施例中,x等于2,且子像素e重叠于第1级传输线tl1。

[0090]

在本实施例中,子像素e的开关元件t3的栅极ge电性连接至第3级扫描线sl3,且开关元件t3的漏极de与开关元件t3的栅极ge(或第3级扫描线sl3)之间的电容为cgd3。

[0091]

开关元件t3的漏极de重叠于栅极ge的长度l3小于标准开关元件t的漏极de重叠于栅极ge的长度l,使开关元件t3的漏极de与栅极ge之间的重叠面积小于标准开关元件t的漏极de与栅极ge之间的重叠面积。因此,开关元件t3的电容cgd3小于标准开关元件t的电容cgd0。

[0092]

子像素e除了开关元件t3的漏极de会与栅极ge产生电容cgd3之外,子像素e的像素电极pe也会与第1级传输线tl1之间产生电容cvg3。然而,标准子像素n的像素电极pe并非重叠于第1级传输线tl1,导致子像素e与标准子像素n容易出现亮度不一致的问题。在本实施例中,通过使开关元件t3的电容cgd3小于标准开关元件t的电容cgd0能够改善前述亮度不一致的问题。

[0093]

请参考图4c与图4d,开关元件t5的漏极de重叠于栅极ge的长度l5小于开关元件t3的漏极de重叠于栅极ge的长度l3,使开关元件t5的漏极de与栅极ge之间的重叠面积小于开关元件t3的漏极de与栅极ge之间的重叠面积。因此,开关元件t5的电容cgd5小于开关元件t3的电容cgd3。

[0094]

请参考图4a与图4e,图4e的子像素b与图4a的标准子像素n有类似的结构,差异在于子像素b重叠于第3+y级传输线tl3+y,且子像素b的开关元件t6的漏极de重叠于栅极ge的长度l6小于标准子像素n的标准开关元件t的漏极de重叠于栅极ge的长度l。在本实施例中,y等于1,且子像素b重叠于第4级传输线tl4。

[0095]

在本实施例中,子像素b的开关元件t6的栅极ge电性连接至第3级扫描线sl3,且开关元件t6的漏极de与开关元件t6的栅极ge(或第3级扫描线sl3)之间的电容为cgd6。

[0096]

开关元件t6的漏极de重叠于栅极ge的长度l6小于标准开关元件t的漏极de重叠于栅极ge的长度l,使开关元件t6的漏极de与栅极ge之间的重叠面积小于标准开关元件t的漏极de与栅极ge之间的重叠面积。因此,开关元件t6的电容cgd6小于标准开关元件t的电容cgd0。

[0097]

子像素b除了开关元件t6的漏极de会与栅极ge产生电容cgd6之外,子像素b的像素电极pe也会与第4级传输线tl4之间产生电容cvg4。然而,标准子像素n的像素电极pe并非重

叠于第4级传输线tl4,导致子像素b与标准子像素n容易出现亮度不一致的问题。在本实施例中,通过使开关元件t6的电容cgd6小于标准开关元件t的电容cgd0能够改善前述亮度不一致的问题。

[0098]

请参考图4d与图4e,开关元件t3的漏极de的长度l3小于开关元件t6的漏极de长度l6,使开关元件t3的漏极de与栅极ge之间的重叠面积小于开关元件t6的漏极de与栅极ge之间的重叠面积。因此,开关元件t3的电容cgd3小于开关元件t6的电容cgd6。

[0099]

请参考图4a与图4f,图4f的子像素c与图4a的标准子像素n有类似的结构,差异在于子像素c重叠于第3+x级传输线tl3+x,且子像素c的开关元件t2的漏极de重叠于栅极ge的长度l2小于标准子像素n的标准开关元件t的漏极de重叠于栅极ge的长度l。在本实施例中,x等于2,且子像素c重叠于第5级传输线tl5。

[0100]

在本实施例中,子像素c的开关元件t2的栅极ge电性连接至第3级扫描线sl3,且开关元件t2的漏极de与开关元件t2的栅极ge(或第3级扫描线sl3)之间的电容为cgd2。

[0101]

开关元件t2的漏极de重叠于栅极ge的长度l2小于标准开关元件t的漏极de重叠于栅极ge的长度l,使开关元件t2的漏极de与栅极ge之间的重叠面积小于标准开关元件t的漏极de与栅极ge之间的重叠面积。因此,开关元件t2的电容cgd2小于标准开关元件t的电容cgd0。

[0102]

子像素c除了开关元件t2的漏极de会与栅极ge产生电容cgd2之外,子像素c的像素电极pe也会与第5级传输线tl5之间产生电容cvg2。然而,标准子像素n的像素电极pe并非重叠于第5级传输线tl5,导致子像素c与标准子像素n容易出现亮度不一致的问题。在本实施例中,通过使开关元件t2的电容cgd2小于标准开关元件t的电容cgd0能够改善前述亮度不一致的问题。

[0103]

请参考图4e与图4f,开关元件t6的漏极de重叠于栅极ge的长度l6小于开关元件t2的漏极de重叠于栅极ge的长度l2,使开关元件t6的漏极de与栅极ge之间的重叠面积小于开关元件t2的漏极de与栅极ge之间的重叠面积。因此,开关元件t6的电容cgd3小于开关元件t2的电容cgd2。

[0104]

在本实施例中,长度l1小于长度l5小于长度l3小于长度l6小于长度l2小于长度l。长度l1与长度l的差值介于0.5微米至1微米。长度l1与长度l2的差值介于0.5微米至1微米。

[0105]

子像素a的电容cgd1小于子像素d的电容cgd5小于子像素e的电容cgd3小于子像素b的电容cgd6小于子像素c的电容cgd2,因此,降低像素阵列基板电容分布不均匀的问题。

[0106]

在一些实施例中,子像素的像素电极与其所重叠的传输线之间的重叠面积相同,因此电容cvg1、电容cvg2、电容cvg3、电容cvg4以及电容cvg5大约彼此相同。

[0107]

图7a与图7b分别是依照本发明的一实施例的不同个子像素俯视图。在此必须说明的是,图7a和图7b的实施例沿用图4a至图4f的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

[0108]

请参考图7a和图7b,在本实施例中,标准子像素n的标准开关元件t与第一子像素a的第一开关元件t1电性连接至第3级扫描线sl3。第一子像素a重叠于第3级传输线tl3,标准子像素n重叠于第m级传输线tlm,其中1<m<n。第m级扫描线slm的充电时间不重叠于第3级扫描线sl3的充电时间。

[0109]

在本实施例中,标准开关元件t的漏极de的宽度w1大于第一开关元件t1的漏极de的宽度w2。借此使开关元件t1的电容cgd1小于标准开关元件t的电容cgd0,并改善显示面板亮度不一致的问题。

[0110]

图8a与图8b分别是依照本发明的一实施例的不同个子像素俯视图。在此必须说明的是,图8a和图8b的实施例沿用图4a至图4f的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

[0111]

请参考图8a和图8b,在本实施例中,标准子像素n的标准开关元件t与第一子像素a的第一开关元件t1电性连接至第3级扫描线sl3。第一子像素a重叠于第3级传输线tl3,标准子像素n重叠于第m级传输线tlm,其中1<m<n。第m级扫描线slm的充电时间不重叠于第3级扫描线sl3的充电时间。

[0112]

在本实施例中,第一子像素a的像素电极pe重叠于第一开关元件t1的栅极ge的面积小于标准子像素n的像素电极pe重叠于标准开关元件t的栅极ge的面积。举例来说,像素电极pe具有重叠于栅极ge的延伸部ep,而标准子像素n的延伸部ep的面积大于第一子像素a的延伸部ep的面积。

[0113]

在一些实施例中,标准子像素n的像素电极pe重叠于标准开关元件t的栅极,而第一子像素a的像素电极pe未重叠于第一开关元件t1的栅极ge。举例来说,第一子像素a的像素电极pe不具有延伸部ep。

[0114]

通过调整像素电极pe的面积使开关元件t1的电容cgd1小于标准开关元件t的电容cgd0,并改善显示面板亮度不一致的问题。

[0115]

图9是依照本发明的一实施例的一种像素阵列基板的显示区俯视图。在此必须说明的是,图9的实施例沿用图4a至图4f的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

[0116]

请参考图9,在本实施例中,像素阵列基板20还包括子像素f。子像素f重叠于传输线中的两者。举例来说,在本实施例中,电性连接至第3级扫描线sl3的部分子像素f重叠于第3级传输线sl3以及第2传输线sl2,电性连接至第3级扫描线sl3的另一部分子像素f重叠于第4级传输线sl4以及第5传输线sl5。

[0117]

以电性连接至第3级扫描线sl3的子像素为例,子像素f的开关元件的漏极与栅极之间的电容为cgd4,而标准子像素n的开关元件的漏极与栅极之间的电容为cgd0。通过前述任一实施例的补偿设计来调整电容cgd4,使电容cgd4小于电容cgd0,借此改善显示画面亮度分布不均的问题。

[0118]

在一些实施例中,以电性连接至第3级扫描线sl3的子像素为例,子像素a的电容cgd1大于子像素f的电容cgd4,借此进一步改善显示画面亮度分布不均的问题。

[0119]

图10是依照本发明的一实施例的一种像素阵列基板的俯视图。在此必须说明的是,图10的实施例沿用图1的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

[0120]

请参考图10,在像素阵列基板30中,每条扫描线sl电性连接至多条传输线tl。举例

来说,第一级扫描线电性连接至三条第一级传输线,三条第一级传输线分别电性连接至不同个驱动电路dr。

[0121]

利用多条传输线提供信号给同一条扫描线,借此能改善扫描线电阻过大造成的问题。

[0122]

虽然在本实施例中,每条扫描线电性连接至三条传输线,但本发明不以此为限。在其他实施例中,每条扫描线电性连接至四条以上的传输线。

[0123]

图11a和图11b分别是依照本发明的一实施例的不同个子像素俯视图。在此必须说明的是,图11a和图11b的实施例沿用图4a至图4f的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

[0124]

为了方便说明,图11a和图11b示出了开关元件、扫描线以及数据线,并省略示出其他构件,关于其他构件的描述可参考前述实施例,在此不赘述。

[0125]

图11b的子像素a与图11a的标准子像素n有类似的结构,差异在于子像素a的漏极de重叠于栅极ge的长度l1小于标准子像素n的标准开关元件t的漏极de重叠于栅极ge的长度l。

[0126]

在本实施例中,子像素a的栅极ge的宽度x1小于标准子像素n的标准开关元件t的栅极ge的宽度x。通过调整栅极ge的宽度x1来改变漏极de重叠于栅极ge的长度l1。

[0127]

在本实施例中,开关元件t1的漏极de重叠于栅极ge的长度l1小于标准开关元件t的漏极de重叠于栅极ge的长度l,使开关元件t1的漏极de与栅极ge之间的重叠面积小于标准开关元件t的漏极de与栅极ge之间的重叠面积。因此,开关元件t1的电容cgd1小于标准开关元件t的电容cgd0。

[0128]

在本实施例中,通过使开关元件t1的电容cgd1小于标准开关元件t的电容cgd0能够改善显示装置亮度不一致的问题。

[0129]

图12是依照本发明的一实施例的一种像素阵列基板的俯视图。在此必须说明的是,图12的实施例沿用图10的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

[0130]

为了方便说明,图12示出了传输线、扫描线以及数据线,并省略示出其他构件,关于其他构件的描述可参考前述实施例,在此不赘述。

[0131]

请参考图12,在本实施例中,像素阵列基板40的传输线tla电性连接驱动电路dr至对应的扫描线sl,且驱动电路dr与对应的扫描线sl之间的传输线tla的长度为y1。在本实施例中,传输线tlb电性连接驱动电路dr至对应的扫描线sl,且驱动电路dr与对应的扫描线sl之间的传输线tlb的长度为y2。在本实施例中,传输线tlc电性连接驱动电路dr至对应的扫描线sl,且驱动电路dr与对应的扫描线sl之间的传输线tlc的长度为y3。在本实施例中,长度y3大于长度y2大于长度y1。

[0132]

由于长度y3、长度y2以及长度y1彼此不同,因此,电性连接至传输线tla的子像素、电性连接至传输线tlb的子像素以及电性连接至传输线tlc的子像素具有不同程度的补偿设计。在一些实施例中,电性连接至传输线tlc的子像素的补偿设计的程度大于电性连接至传输线tlb的子像素的补偿设计的程度,电性连接至传输线tlb的子像素的补偿设计的程度

大于电性连接至传输线tlc的子像素的补偿设计的程度。举例来说,电性连接至传输线tla的第一开关元件的漏极与栅极的重叠面积为a1,电性连接至传输线tlb的第二开关元件的漏极与栅极的重叠面积为a2,电性连接至传输线tlc的第三开关元件的漏极与栅极的重叠面积为a3,通过调整漏极的长度、漏极的宽度及/或栅极的宽度,使面积a1>面积a2>面积a3。换句话说,子像素的补偿设计的补偿值越大,漏极与栅极的重叠面积越小。举例来说,第一开关元件的漏极的长度大于第二开关元件的漏极的长度大于第三开关元件的漏极的长度。举例来说,第一开关元件的漏极的宽度大于第二开关元件的漏极的宽度大于第三开关元件的漏极的宽度。

[0133]

举例来说,电性连接至传输线tla的第一开关元件的漏极与栅极之间的电容为cgda,电性连接至传输线tlb的第二开关元件的漏极与栅极之间的电容为cgdb,电性连接至传输线tlb的第二开关元件的漏极与栅极之间的电容为cgdc,其中cgda>cgdb>cgdc。

[0134]

在其他实施例中,也可以通过调整像素电极重叠于开关元件的栅极的面积来改变子像素的补偿设计的程度(如图8a与图8b)。举例来说,电性连接至传输线tla的第一开关元件的栅极与第一像素电极的重叠面积为b1,电性连接至传输线tlb的第二开关元件的栅极与第二像素电极的重叠面积为b2,电性连接至传输线tlc的第三开关元件的栅极与第三像素电极的重叠面积为b3,面积b1>面积b2>面积b3。换句话说,子像素的补偿设计的补偿值越大,像素电极与栅极的重叠面积越小。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1