混合CMOS兼容电光器件的制作方法

混合cmos兼容电光器件

技术领域

1.本发明涉及一种电光器件,特别是但不限于一种混合带状加载电光调制器。

背景技术:

2.硅光子学具有使其成为光学调制器的理想选择的显著优势,尤其是用于短距离的那些调制器。这些优势包括成熟的制造工艺、利用cmos处理优势的能力、廉价的低成本大规模制造以及通过载流子注入/耗尽效应实现的电光可调谐性。硅光子波导是亚微米级的,并且具有较高的折射率对比度,这允许尖锐弯曲和具有较小占用空间的紧凑结构。然而,对于调制,硅光子学也具有一些缺点,例如较慢的速度(由于pn结/载流子耗尽的速度)以及一些电非线性(这会降低无杂散动态范围等缺点)。

3.对于不同的应用,一些材料优于其它材料。

4.例如,诸如铌酸锂(linbo3)的非线性晶体材料(有时称为χ2材料)在设计调制器时很受关注,特别是对于长距离光通信。它们具有低插入损耗、低传播损耗和高速调制的优点。然而,限定波导的传统方法是钛扩散和质子交换,并且这些方法会导致低折射率变化。因此,单模波导处于5微米级,并且弯曲损耗极高。这意味着例如铌酸锂器件的占地面积很大。而且,电极的放置必须被很好地分开,因为模式的拖尾很长,从而导致降低的调制效率。这些因素对调制速度施加了远低于“理论”限制的“实用”限制。

5.在cmos制造工艺中使用铌酸锂有几个问题。

6.一般而言,铌酸锂与标准cmos制造不兼容。一个问题是由于铌酸锂的蚀刻副产物导致的污染。此外,铌酸锂难以各向异性地进行蚀刻,并且会产生粗糙的侧壁,这导致较高的传播损耗。铌酸锂已被用于形成脊形波导,然而铌酸锂的光滑侧壁的蚀刻是持续的问题。最先进的蚀刻技术产生高度倾斜的侧壁(~45度),并且这会对模式分布产生负面影响。已经提出一些建议来克服使用铌酸锂的一些问题,但是没有一种建议产生最佳或实用的解决方案。

7.已知现有技术具有许多问题,这些问题包括:

8.·

与非cmos兼容材料的蚀刻相关联的问题,

9.·

与主要存在于χ2材料外部的光传播模式相关联的问题,和/或

10.·

与用于调制器件的适当方法相关联的问题。

11.结果,现有技术要么不能在标准硅光子学制造工艺中实施,要么由于χ2区域外部的高光功率而不能获得足够的效率。

12.本发明试图解决这些问题中的至少一些或全部。

13.用于设计和制造调制器的一个可能的改进是将硅光子学与铌酸锂结构相结合。从上文可以清楚地看出,这并不简单。本发明寻求找到这些问题中的至少一些的解决方案。

14.本发明的一个目的是将硅和铌酸锂结合以形成光子器件。

15.另外的目的是改进结合硅和铌酸锂的工艺。

16.另外的目的是生产改进的调制器。

17.下面描述的实施例不限于解决现有技术的任一或所有缺点的实施方式。

技术实现要素:

18.提供发明内容是为了以简化的形式介绍在下面的详细描述中被进一步描述的一系列概念的选择。本发明内容不旨在标识所要求保护的主题的关键特征或必要特征,也不旨在用作确定所要求保护的主题的范围中的辅助手段。

19.根据本发明的一方面,提供了一种混合光子芯片,该混合光子芯片包括被布置成限定提供功能的芯片的多种半导体材料,其中芯片的至少第一部分由可以使用cmos技术制造的材料形成;并且芯片的至少第二部分不易在cmos技术期间被制造;其中与第一部分结合的芯片的第二部分被配置为支持传播的低损耗单模波导。

20.优选地,芯片的至少第二部分包括非线性晶体材料(χ2材料或任何其它电光材料)。

21.优选地,非线性晶体材料可以是χ2材料或任何其它电光材料,例如:铌酸锂(linbo3)、钽酸锂(litao3)、铌酸钾(knbo3)、钛酸钡(batio3)、磷酸氧钛钾(ktiopo4)、硼酸钡(bab2o4)。

22.优选地,芯片的第一部分包括绝缘体上硅soi平台上的不单独支持单模传播的一个或多个硅带。

23.优选地,芯片的第二部分和一个或多个硅带一起支持单模传播。

24.优选地,混合芯片是调制器。

25.优选地,芯片的第二部分是被配置为基本上支持主要在非线性晶体材料中的光学模式的波导。

26.优选地,调制器是马赫曾德(mach zehnder)调制器。

27.优选地,芯片的第一部分包括电极。

28.优选地,电极位于芯片的第一部分的掩埋氧化物的间隙中,以容纳来自芯片的第二部分的键合点。

29.优选地,芯片的第二部分通过倒装芯片键合技术施加到芯片的第一部分。

30.优选地,在倒装芯片键合技术期间,电极连接到芯片的第二部分。

31.根据本发明的第二方面,提供了一种制造混合光子芯片的方法,该方法排除了非线性晶体材料的蚀刻,该方法包括:使用cmos制造工艺在绝缘体上硅soi平台上由半导体材料形成芯片的第一部分;将芯片的没有进行cmos处理步骤的第二部分施加到芯片的第一部分上;芯片的第二部分由被配置为基本上支持芯片的单个传播模式的材料制成。

32.优选地,在soi平台上形成不单独支持单模传播的一个或多个硅带。

33.优选地,形成作为调制器的混合芯片。

34.优选地,将芯片的第二部分形成为被配置成基本上支持单个传播模式的波导。

35.优选地,将调制器形成为mach zehnder调制器。

36.优选地,将电极形成为芯片的第一部分的一部分。

37.优选地,将间隙蚀刻到soi平台的掩埋氧化物层中;形成位于芯片的第一部分的掩埋氧化物中的间隙中的电极,以容纳来自芯片的第二部分的键合点。

38.优选地,以倒装芯片键合技术将芯片的第二部分施加到芯片的第一部分。

39.优选地,在倒装芯片键合技术期间,电极连接到芯片的第二部分。

40.根据本发明的第三方面,提供了用于形成光子集成芯片的工艺设计套件,当在芯片制造系统中处理时,该工艺设计套件使得芯片制造系统构成另一方面的光子集成芯片。

41.根据本发明的第四方面,提供了一种其上存储有芯片的计算机可读描述的计算机可读存储介质,当在芯片制造系统中进行处理时,该计算机可读描述使得芯片制造系统制造另一实施例的光子集成芯片。

附图说明

42.本发明的实施例将参照以下附图通过示例的方式进行描述,在附图中:

43.图1a和图1b示出了根据本发明的实施例的两种不同材料组合中的电场强度的表示。

44.图2a和图2b示出了根据本发明的实施例的两种可能的调制器的示意性截面图。

45.图3示出了根据本发明的实施例的全调制器的器件的示意图。

46.图4是示出根据本发明的实施例的另外的器件的图。在该图中,电极在χ2材料下方。

47.图5a至图5f是示出根据本发明的实施例的器件的制造工艺的图。

48.图6a至图6e示出了用于形成图4器件的制造步骤。

49.图7a至图7d是示出根据本发明的实施例的器件的性能参数中的一些的一组曲线图。

50.图8是如前图所示的双纳米带状加载铌酸锂波导的光学模式分布。

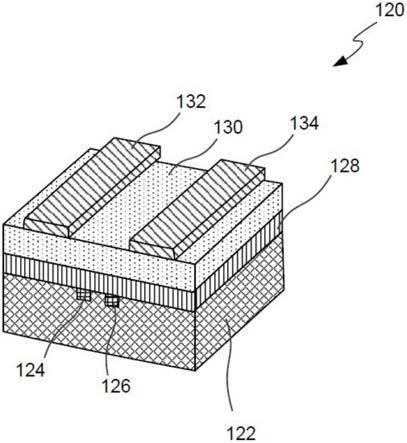

51.所有附图中使用共同的附图标记来表示相似的特征。

具体实施方式

52.下面仅通过示例的方式描述本发明的实施例。这些实施例代表了申请人目前已知的将本发明付诸实践的最佳方式,尽管它们不是实现这一目标的唯一方式。该描述阐述了示例的功能以及构建和操作示例的步骤的顺序。然而,相同或等效的功能和顺序可以通过不同的示例来实现。

53.本发明涉及通过优化每个平台的强度并减轻硅光子学平台与铌酸锂的弱点来组合硅光子学平台与铌酸锂。为了实现这一点,本发明涉及一种例如倒装芯片键合(flip-chip bonding)的工艺,例如将铌酸锂键合在诸如波导的cmos制造的器件的绝缘体上。如本领域技术人员将理解的那样,cmos器件可以由包括硅、氮化硅和许多其他材料制成。该工艺需要精心工程设计,这允许波导模式主要存在于铌酸锂区域(或χ2材料区域),而不是存在于cmos制造的波导区域(或硅区域)。这很重要,因为χ2材料是电光活性的,而硅不是。波导模式到非电光活性区域中的任何重叠都会降低调制器的效率。这在图1中示出,其中经过精心设计,高比例的功率驻留在铌酸锂而不是硅中。铌酸锂层在图1a和图1b中被标记为10和12。

54.参照图2a,器件总体上以100示出。器件100是调制器。调制器包括掩埋氧化物层102和硅波导104,在这个示例中,该硅波导被称为具有两个肋部106和108的肋型硅波导。另外的二氧化硅层110位于波导上。铌酸锂112连接到波导106和108的肋部以及二氧化硅层

110。二氧化硅层114位于铌酸锂上方,并且电极116和118位于器件的顶部处。这个器件在本文中被称为混合硅χ2调制器。铌酸锂是χ2材料。

55.两个硅带或硅肋连同薄铌酸锂层可以支持传播的光学单模。每个元件不能单独支持传播的单模。在本发明中,光学模式的功率主要存在于电光活性区域,而不是硅带或硅肋。本发明描述了所需的精心工程设计,使得大部分光学模式包含在铌酸锂区域内。重要的是,单独的任何元件都不能独立支持单模。否则,诸如在其它设计中,大量不适合的模式将存在于硅带中。

56.χ2材料是拥有χ2非线性的材料。这意味着这些材料对电场具有非线性极化密度响应。结果,这些材料表现出电光效应,其中折射率由于所施加的电场的存在而改变。这些材料有时被称为非线性晶体材料,例如包括:铌酸锂(linbo3)、钽酸锂(litao3)、铌酸钾(knbo3)、钛酸钡(batio3)、磷酸氧钛钾(ktiopo4)、硼酸钡(bab2o4)等。

57.电光效应的示例是普克尔斯(pockels)效应,其中折射率随所施加的电场而线性变化。

58.如所讨论那样,铌酸锂是难以处理(尤其是蚀刻)的材料,并且与标准的cmos制造不兼容。因此,本发明不包括铌酸锂层的任何处理,如将在下面更详细地描述的那样。结果,这允许与标准cmos制造集成,并提供了本发明的优点中的一个。

59.现在回到图2b,这示出了有时被称为脊型调制器的第二类型的调制器120。这个器件包括波导124和126形成在其中的掩埋氧化物层122。铌酸锂128被定位并与波导相接触。二氧化硅层130位于铌酸锂上方,并且电极132和134位于器件的顶部处。该器件是另一种混合硅χ2调制器。

60.图2a和图2b仅作为示例呈现,并且可以设想其它类似的器件。除调制器之外的其它类型的混合硅χ2器件可以如本文所述进行设计和制造。此外,该处理可以用于由其中至少一种材料与cmos兼容且至少一种材料与cmos不兼容的材料制成的任何混合芯片。由此,所得到的器件可以包括cmos兼容的元件或层以及cmos不兼容的元件或层。

61.图3示出了具有类似优点的另外的器件200。器件200是具有两个移相器的mach-zehnder推挽配置调制器。该器件包括掩埋氧化物层202,波导204位于掩埋氧化物层202上方。波导包括输入206和输出208以及连接在输入和输出之间的两个平行臂或路径210、212。铌酸锂214位于波导和掩埋氧化物层上方。然后施加二氧化硅层216和电极218。

62.图4是又一器件300,其中电极被结合到该器件中并且通过不同的机制被施加,如将在下面的图6中描述的那样。在图4中,波导被定位在铌酸锂层下方。器件300包括基底层302,该基底层可以是二氧化硅或硅,在该基底层上图案化另外的掩埋氧化物304以留下随后可以容纳电极308的空间306。然后,该结构可以包括任何合适的器件,例如如图2a、图2b和图3所示。在图4中,该器件类似于图2b,并且包括波导124和126形成在其中的掩埋氧化物层304。铌酸锂128被定位并与波导相接触。另外的二氧化硅层130位于铌酸锂上方。

63.现在将参照图5描述用于制造图2b器件的工艺。在第一步骤中,如图5a所示,获取绝缘体上硅(silicon on insulator,soi)晶片。soi晶片400包括硅层402、掩埋氧化物层404和较薄的硅层406。在图5b中,硅波导408被光刻限定,并且附加的二氧化硅410被沉积。在图5c中,沉积的二氧化硅随后被平坦化。在图5d中,绝缘体芯片412上铌酸锂是键合到基底上的晶片或倒装芯片。该芯片包括一层铌酸锂层414、二氧化硅层416和基底418。如图5e

所示,铌酸锂芯片412尽可能靠近顶部二氧化硅层向下研磨。任何剩余的硅可以被蚀刻,直到暴露出二氧化硅层的顶部为止。在图5f中,电极420被沉积和图案化。

64.如参考图6所述,键合过程还可以包括电极,其中这些电极被定位在适合线键合的位置。

65.在第一步骤中,如图6a所示,获取绝缘体上硅(silicon on insulator,soi)晶片。soi晶片500包括硅层502、掩埋氧化物层504和较薄的硅层506。在图6b中,硅波导508被光刻限定,并且二氧化硅510被沉积。在图6c中,所沉积的二氧化硅随后被平坦化。在图6d中,两个间隙512被蚀刻到二氧化硅中。掩模用于在所产生的间隙内沉积电极514。在图6e中,绝缘体芯片516上的铌酸锂是键合到基底上的倒装芯片。该芯片包括一层铌酸锂层518、掩埋氧化物层520和硅基底522。此外,芯片包括键合点524,该键合点旨在允许凸点下金属化以将芯片连接到电极514。图6f示出了连接到电极514的铌酸锂芯片的最终位置。然后可以进行进一步的处理,例如研磨和蚀刻以去除硅(如果需要的话),或者对所需的器件进行任何其它合适的处理。

66.这些器件提供了许多优点。作为示例,这些优点包括:可获得比硅光子学平台更高的调制速度;模式被限制在χ2区域内,从而允许更高的调制效率;没有铌酸锂的处理(蚀刻);并且该工艺是cmos兼容的。该工艺可以应用于其它混合芯片,其中混合芯片的一部分是通过cmos制造工艺制造的,而另一部分是倒装芯片到cmos部分上。混合芯片是一种具有cmos兼容的元件和cmos不兼容的元件的混合芯片。作为示例,cmos不兼容的材料包括χ2材料。

67.在硅光子学中,共面波导(coplanar waveguide,cpw)加载有pn结。这可以显著降低-3db带宽(并且因此降低调制速度)。铌酸锂上的行波cpw将显著快于硅光子学的行波cpw,因为其只是没有加载pn结的cpw。存在于铌酸锂中的pockels效应或线性电光效应也是场效应,因此显著快于硅光子学的载流子耗尽效应。利用上述结构,图7的曲线图示出了某些基于有限元方法(finite element method,fem)的模拟,示出了超过60ghz的s21-3db点。一般而言,电光-3db响应接近电-6db点,其超过100ghz,如图7b所示。图7a示出s11反射可以被很好地控制并且少于-20db。图7c示出微波模式的有效折射率可以与混合波导的有效折射率相匹配。图7d示出端口阻抗也可以同时匹配到50欧姆。

68.如上所述,该模式被限制于非线性χ2区域。通过设计硅波导,我们可以将大部分模式分配到铌酸锂中。这很重要,因为典型的加载波导只有在附加的加载区段中才具有大部分模式。通过优化硅纳米带的数量、几何形状和间隔来帮助设计。在图2b中具有两个硅带124和126的这种配置中,每个个体都不能支持单模。然而,由于它们被放置在优化的几何形状中,因此与硅相反,可以支持主要在非线性区域(即铌酸锂)中的非辐射单模。结果,导致光学模式驻留在铌酸锂层804中,而不是在硅带800、802中。这在图8中被形象地示出。

69.由于不需要蚀刻非线性χ2材料,因此实现了另外的优点。在任何情况下,蚀刻铌酸锂都是困难的步骤,如果将其添加到标准的cmos处理中,则更是如此,因为蚀刻副产物可能会污染腔室。这对于感应耦合等离子体反应离子蚀刻(inductively coupled plasma reactive-ion etching,icp/rie)工艺尤其成问题。由于没有任何涉及铌酸锂的处理步骤,cmos处理线不会暴露于任何附加污染物。此外,铌酸锂是难以蚀刻的材料,并且通常产生大量的侧壁粗糙度以及较浅的侧壁角度。避免铌酸锂的任何处理有助于减少任何粗糙度引起

的传播损耗。

70.该器件产生高电场强度(与传统扩散式铌酸锂调制器相比)。由于结构的有利几何形状和光学模式的较小尺寸,电极可以更靠近得放置在一起。例如,电极间隔可以低至5μm,而不会造成显著的金属吸收损耗。例如,电场模拟示出,对于端口上1w的应用、对于11μm的间隙,活性区上的归一化电场被平均为例如598 800v/m。对于所施加的每伏电压,该归一化电场为85 542v/m。共面波导设计可以被修改以适应更近的电极间距。这给出了更小的器件占地面积的另外的优点。

71.与常规铌酸锂设计相比,根据本发明的器件需要相对较低的驱动电压。

72.上述实施例和优点是示例性的。存在可以实施并且仍然形成本发明的范围的一部分的许多变化。以下修改是这方面的某个示例。

73.soi基底可以用波导可以被限定在其中的任何类型的基底代替例如sin、sio2上聚合物等。非线性光学材料可以是任何非线性材料,例如铌酸锂、电光聚合物、钽酸锂、其它χ2材料和其它电光材料。带状加载非线性薄膜的方法可以被任何其它波导制造技术替代。行波电极可以在倒装芯片键合工艺之前或之后限定,并且硅波导可以是电极设计的一部分。电极也可以通过蚀刻凹入到顶部硅中。通过将电极放置得更靠近波导,可以降低所需的驱动电压。

74.本发明可以包括上述示例的多种变化和替代性方案。这些旨在包含在本发明的范围内。

75.示例实施例包括以下内容。

76.一种混合光子芯片,该混合光子芯片包括被布置成限定提供功能的芯片的多种半导体材料,其中芯片的至少第一部分由可以使用cmos技术制造的材料形成;并且芯片的至少第二部分不易在cmos技术期间被制造;其中与第一部分结合的芯片的第二部分被配置为支持传播的低损耗单模波导。

77.优选地,芯片的至少第二部分包括非线性晶体材料(χ2材料或任何其它电光材料)。

78.优选地,非线性晶体材料(χ2材料和任何其它电光材料)包括以下材料中的至少一种:铌酸锂(linbo3)、钽酸锂(litao3)、铌酸钾(knbo3)、钛酸钡(batio3)、磷酸氧钛钾(ktiopo4)、硼酸钡(bab2o4)。

79.优选地,芯片的第一部分包括绝缘体上硅soi平台上的不单独支持单模传播的一个或多个硅带。

80.优选地,芯片的第二部分和一个或多个硅带一起支持单模传播。

81.优选地,混合芯片是调制器。

82.优选地,芯片的第二部分是被配置为基本上支持主要在非线性晶体材料中的光学模式的波导。

83.优选地,调制器是马赫曾德调制器。

84.优选地,芯片的第一部分包括电极。

85.优选地,电极位于芯片的第一部分的掩埋氧化物的间隙中,以容纳来自芯片的第二部分的键合点。

86.优选地,芯片的第二部分通过倒装芯片键合技术被施加到芯片的第一部分。

87.优选地,在倒装芯片键合技术期间,电极连接到芯片的第二部分。

88.一种制造混合光子芯片的方法,该方法不包括非线性晶体材料的蚀刻,该方法包括:使用cmos制造工艺在绝缘体上硅soi平台上由半导体材料形成芯片的第一部分;将芯片的没有进行cmos处理步骤的第二部分施加到芯片的第一部分上;芯片的第二部分由被配置为基本上支持芯片的单个传播模式的材料制成。

89.优选地,在soi平台上形成不单独支持单模传播的一个或多个硅带。

90.优选地,形成作为调制器的混合芯片。

91.优选地,将芯片的第二部分形成为被配置成基本上支持单个传播模式的波导。

92.优选地,将调制器形成为马赫曾德调制器。

93.优选地,将电极形成为芯片的第一部分的一部分。

94.优选地,将间隙蚀刻到soi平台的掩埋氧化物层中;形成位于芯片的第一部分的掩埋氧化物中的间隙中的电极,以容纳来自芯片的第二部分的键合点。

95.优选地,以倒装芯片键合技术将芯片的第二部分施加到芯片的第一部分。

96.优选地,在倒装芯片键合技术期间,电极连接到芯片的第二部分。

97.一种用于形成光子集成芯片的工艺设计套件,当在芯片制造系统中处理该芯片时,该工艺设计套件使得芯片制造系统构成任一实施例中的光子集成芯片。

98.一种其上存储有芯片的计算机可读描述的计算机可读存储介质,当在芯片制造系统中处理该芯片时,使得芯片制造系统制造另一实施例的光子集成芯片。

99.对本领域技术人员来说,在不损失所寻求的效果的情况下,扩展或改变本文给出的任何范围或器件值都是显而易见的。

100.应当理解的是,上述益处和优点可以涉及一个实施例或者可以涉及几个实施例。实施例不限于解决任何或所有所述问题的那些实施例,或者具有任何或所有所述益处和优点的那些实施例。

101.对“一”项的任何引用都是指这些项中的一个或多个。术语“包括”在本文中用于表示包括所标识的方法块或元件,但是这些块或元件不包括排他性列表,并且方法或设备可以包含附加的块或元件。

102.如本文所用的术语计算机程序代码和计算机可读指令是指用于处理器的任何种类的可执行代码,包括以机器语言、解释语言或脚本语言表达的代码。可执行代码包括二进制代码、机器代码、字节代码、限定集成电路的代码(诸如硬件描述语言或网表)、以及以编程语言代码(诸如c、java或opencl)表示的代码。例如,可执行代码可以是任何种类的软件、固件、脚本、模块或库,当在虚拟机或其它软件环境处被适当地执行、处理、解释、编译、执行时,该软件、固件、脚本、模块或库使得支持可执行代码的计算机系统的处理器执行由代码指定的任务。

103.它还旨在涵括限定如本文所述的硬件的配置的软件,诸如用于设计集成电路或用于配置可编程芯片以实行期望功能的hdl(hardware description language,硬件描述语言)软件。也就是说,可以提供一种计算机可读存储介质,其上编码有呈集成电路限定数据集形式的计算机可读程序代码,当在工艺设计套件中被处理时,该计算机可读程序代码配置系统以制造本文中的器件中的一些或全部。

104.本文描述的方法的步骤可以以任何合适的顺序进行,或者在合适的情况下同时实

行。此外,在不脱离本文所述主题的精神和范围的情况下,可以从任何方法中删除单独的块。上述示例中的任何一个的各方面都可以与所描述的其它示例中的任何一个的各方面相结合,以形成另外的示例,而不会失去所寻求的效果。

105.可以提供一种在如本文所述的工艺设计套件处进行制造方法。此外,可以提供工艺设计套件数据集,当在芯片制造系统中被处理时,该数据集引出如本文所述的制造pic和/或不对称对准布置的方法。

106.应当理解的是,优选实施例的以上描述仅作为示例给出,并且可以由本领域技术人员进行各种修改。尽管上面已经以一定程度的特殊性或者参考一个或多个单独的实施例描述了各种实施例,但是本领域技术人员可以在不背离本发明的精神或范围的情况下对所公开的实施例做出多种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1