基于深硅刻蚀的光纤与硅光芯片高精度耦合实现方法

本发明涉及的是一种光芯片领域的技术,具体是一种基于深硅刻蚀的光纤与硅光芯片高精度耦合实现方法。

背景技术:

1、集成光子学领域取得了巨大的发展。由于具有低成本、高性能、小尺寸和半导体大规模制造兼容性等优点,硅基光电子器件成为了集成光子学的研究热点。但由于光纤的芯径与芯片内波导的截面尺寸相差较大,芯片内光信号与片外光信号的耦合连接成为了硅基光电芯片封装技术的关键部分。以c波段(约1550nm)光波导为例,其理论宽度为450nm、厚度为220nm,其中传输的光场的模场直径(mfd)约为0.3μm,而单模光纤的模场直径约为9μm,二者之间存在巨大的模场失配。目前常用的平面波导类耦合方法是通过光纤阵列(fa,fiberarray)与芯片端面波导对准耦合。但由于该方法所选用的硬胶会随环境变化而产生较大应力,因此并不适用于悬臂梁波导芯片耦合。此外,若芯片端面底部有凸起则无法使用常规光纤阵列,要定制特定规格光纤阵列用于耦合对准,该类光纤阵列制作工艺复杂,加工难度较高,

2、成本昂贵,与芯片耦合工艺复杂。

技术实现思路

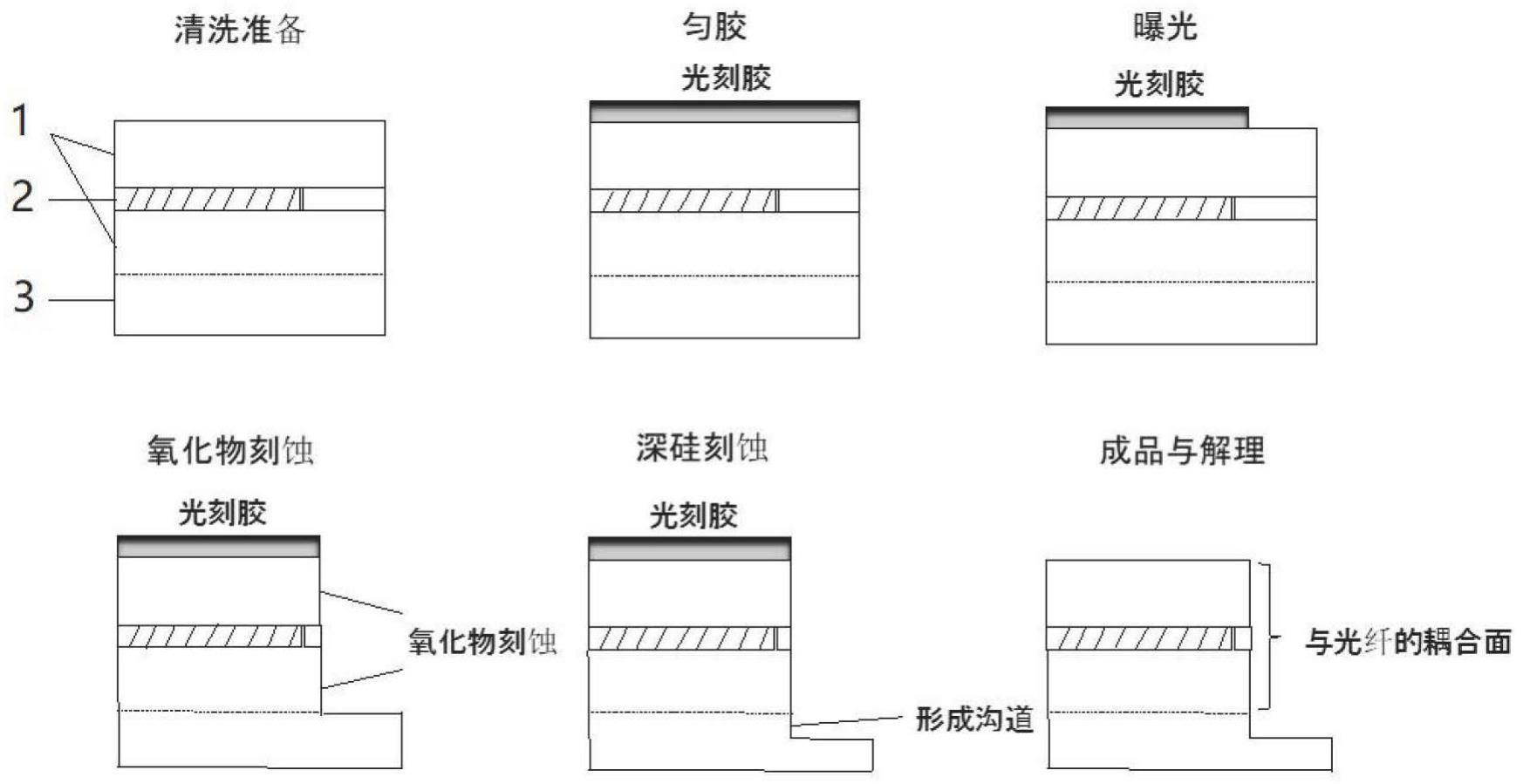

1、本发明针对现有技术存在的上述不足,提出一种基于深硅刻蚀的光纤与硅光芯片高精度耦合实现方法,通过特定深度深硅刻蚀槽图形,运用光刻、包层刻蚀及深硅刻蚀手段制备特定深度的深硅刻蚀槽,利用光刻和刻蚀的高精度从而实现光纤到芯片上波导耦合条件,如高度、距离等的精确控制,有效提高耦合容差和耦合鲁棒性。

2、本发明是通过以下技术方案实现的:

3、本发明涉及一种基于深硅刻蚀的光纤与硅光芯片高精度耦合实现方法,通过在在衬底上旋涂光刻胶后进行掩膜对准式曝光;然后采用包层刻蚀去除顶部和底部包层材料后利用c4f8和sf6进行深硅刻蚀实现高深宽比、侧壁陡直的硅刻蚀;最后将晶片解理成独立芯片,其台阶状的沟道用于与光纤进行耦合。

4、所述的耦合的位置由光刻、包层刻蚀及深硅刻蚀得到的深硅刻蚀槽的位置决定,利用光刻和刻蚀的参数实现耦合参数的精确控制。

5、所述的旋涂,使用光刻胶如(megapositspr220-4.5)作为蚀刻掩模,将光刻胶以2500转/分的速度旋转60秒,得到厚度约5μm的光刻胶,随后在115℃下烘烤3分钟,将光刻胶中的溶剂蒸发,增强光刻胶对芯片的附着力。

6、所述的掩膜对准式曝光,使用掩膜对准曝光机,应用紫外光源曝光20-25秒,曝光后进行烘烤和显影以降低曝光导致的驻波效应;最后进行水合处理使水扩散回光刻胶。

7、所述的烘烤,在115℃下进行曝光后烘烤约3分钟。

8、所述的包层刻蚀,采用但不限于氧化物刻蚀。

9、所述的氧化物刻蚀采用的反应气体为chf3、o2或者ar,对上、下包层的材料进行全刻蚀。

10、所述的深硅刻蚀的深度为使用光纤的半径减去底部包层材料的厚度。

11、所述的深硅刻蚀,采用基于刻蚀和钝化交替进行,具体步骤包括:

12、a)碳氟聚合物沉积形成钝化层:使用c4f8气体作为沉积气体,沉积过程中形成等离子体附着在硅上并形成钝化膜,防止侧壁被蚀刻。

13、b)硅刻蚀:使用sf6气体作为硅蚀刻的蚀刻气体,sf6气体在等离子体中离解形成sf4或sf2以及能够参与硅蚀刻反应反应的原子氟。

14、所述的交替进行是指:碳氟聚合物沉积形成钝化层与钝化层与硅刻蚀工艺进行快速切换,每个阶段持续0.1-9s并重复多次刻蚀-钝化,导致各向同性蚀刻步骤仅蚀刻底部而不影响侧壁。

15、本发明涉及上述方法制备得到的基于深硅刻蚀的光纤硅光芯片耦合结构,包括衬底和位于其上的sio2包层、si3n4或硅波导和光纤,其中:sio2包层包覆于si3n4或硅波导外部,si3n4或硅波导与光纤耦合连接。

技术特征:

1.一种基于深硅刻蚀的光纤与硅光芯片高精度耦合实现方法,其特征在于,通过在在衬底上旋涂光刻胶后进行掩膜对准式曝光;然后采用包层刻蚀去除顶部和底部包层材料后利用c4f8和sf6进行深硅刻蚀实现高深宽比、侧壁陡直的硅刻蚀;最后将晶片解理成独立芯片,其台阶状的沟道用于与光纤进行耦合。

2.根据权利要求1所述的基于深硅刻蚀的光纤与硅光芯片高精度耦合实现方法,其特征是,所述的耦合的位置由光刻、包层刻蚀及深硅刻蚀得到的深硅刻蚀槽的位置决定,利用光刻和刻蚀的参数实现耦合参数的精确控制。

3.根据权利要求1所述的基于深硅刻蚀的光纤与硅光芯片高精度耦合实现方法,其特征是,所述的深硅刻蚀,采用基于刻蚀和钝化交替进行,具体步骤包括:

4.一种根据权利要求1-3中任一所述方法制备得到的光纤硅光芯片耦合结构,其特征在于,包括衬底和位于其上的sio2包层、si3n4或硅波导和光纤,其中:sio2包层包覆于si3n4或硅波导外部,si3n4或硅波导与光纤耦合连接。

技术总结

一种基于深硅刻蚀的光纤与硅光芯片高精度耦合实现方法,通过在在衬底上旋涂光刻胶后进行掩膜对准式曝光;然后采用包层刻蚀去除顶部和底部包层材料后利用C<subgt;4</subgt;F<subgt;8</subgt;和SF<subgt;6</subgt;进行深硅刻蚀实现高深宽比、侧壁陡直的硅刻蚀;最后将晶片解理成独立芯片,其台阶状的沟道用于与光纤进行耦合。本发明通过特定深度深硅刻蚀槽图形,运用光刻及深硅刻蚀手段制备特定深度的深硅刻蚀槽,利用光刻和刻蚀的高精度从而实现光纤到芯片上波导耦合条件,如高度、距离等的精确控制,有效提高耦合容差和耦合鲁棒性。

技术研发人员:纪幸辰,刘芳瑜,王硕,苏翼凯

受保护的技术使用者:上海交通大学

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!