多晶SiC成型体及其制造方法与流程

本发明涉及由cvd-sic形成的多晶sic成型体及其制造方法。

背景技术:

1、多晶sic成型体的耐热性、耐腐蚀性及强度等各种特性优异,用于各种用途。多晶sic成型体通过cvd法在基材的表面析出多晶sic,成膜后除去基材而得到。

2、例如,在专利文献1中,已知用于半导体制造装置用的部件、蚀刻装置、cvd装置等的部件。

3、现有技术文献

4、专利文献

5、专利文献1:日本特开2014-31527号公报。

技术实现思路

0、发明概述

1、多晶sic成型体根据用途要求有各种各样的特性。

2、例如,如专利文献1所述,在将多晶sic成型体作为等离子体蚀刻用部件使用的情况下,为了释放静电或均匀地产生等离子体气体,多晶sic成型体必须是低电阻率且是均匀电阻率。

3、本发明的目的在于稳定地供给低电阻率且电阻率均匀的半导体制造装置用部件。以往,多晶sic成型体在厚度方向上的电阻率偏差大,不能充分发挥作为多晶sic成型体的性能。

4、具体而言,在用四端子法或四探针法测量的方法中,是在几毫米至几十毫米级的宏观级区域进行评估,而直接获知在微米级的厚度方向上的电阻分布,现在也非常困难。

5、另一方面,在拉曼光谱中可以评估微米级的分布,即使在以往的cvd-sic中认为电阻率的偏差小,已经判明在微米级也足够大。厚度方向的电阻率的偏差由于部件消耗而使部件表面的电阻率发生变动,因此需要调整装置的运转条件,由此引起装置的吞吐量降低。从这点出发,低电阻率且厚度方向上的均匀电阻率的半导体制造装置用部件令人期待。

6、因此,本发明的课题在于提供一种低电阻率且厚度方向的电阻率的偏差小的多晶sic成型体及其制造方法。

7、为了解决上述课题,本发明包含以下事项。

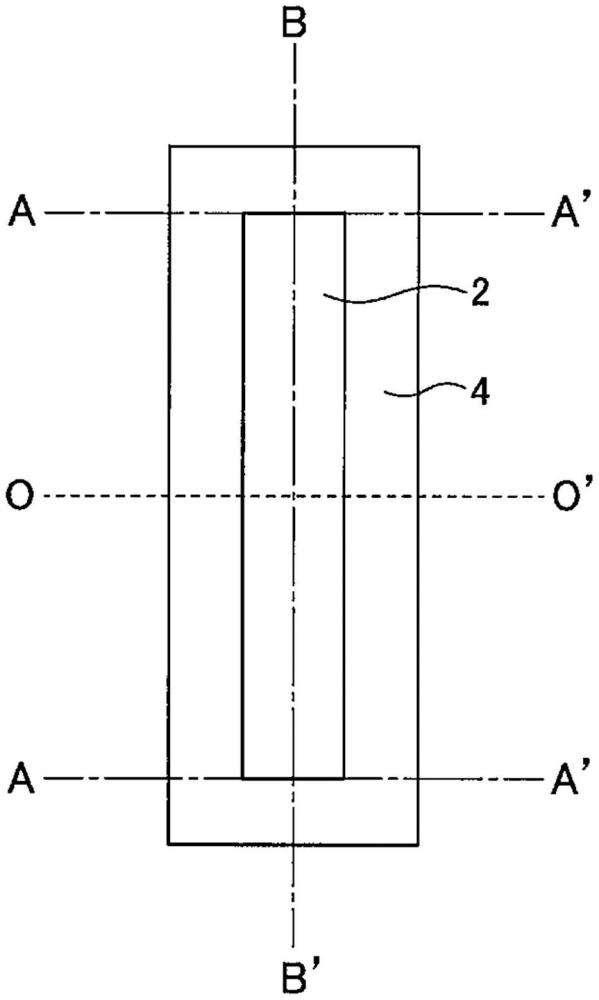

8、[1]一种多晶sic成型体,其特征在于:

9、电阻率为0.050ωcm以下,

10、当将拉曼光谱中的波数950~970cm-1范围内的峰值强度设为“a”,将拉曼光谱中的波数780~800cm-1范围内的峰值强度设为“b”时,峰值强度比率(a/b)的平均值为0.040以下,生长面侧的峰值强度比率的平均值与基材面侧的峰值强度比率之差为0.040以下。

11、[2]根据[1]所述的多晶sic成型体,其中,氮含量为200ppm(质量百万分率)以上。

12、[3]一种根据[1]或[2]所述的多晶sic成型体的方法,其为通过cvd法制造多晶sic成型体的方法,包括:

13、在反应室内,与原料气体及载气一起导入含氮原子化合物气体,

14、使从成膜开始到反应结束的含氮原子化合物气体的浓度以一定速度上升。

15、[4]根据[3]所述的多晶sic成型体的制造方法,其中,从成膜开始到反应结束的含氮原子化合物气体的流量的上升率为1.0%/hr以上且10.0%/hr以下。

16、根据本发明,提供一种低电阻率且厚度方向的电阻率的偏差小的多晶sic成型体及其制造方法。

技术特征:

1.一种多晶sic成型体,其特征在于:

2.根据权利要求1所述的多晶sic成型体,其中,

3.一种根据权利要求1或2所述的多晶sic成型体的制造方法,其为通过cvd法制造多晶sic成型体的方法,包括:

4.根据权利要求3所述的多晶sic成型体的制造方法,其中,

技术总结

本发明提供一种低电阻率、其厚度方向的电阻率的偏差小的多晶SiC成型体及其制造方法。多晶SiC成型体的电阻率为0.050Ωcm以下,当将拉曼光谱中的波数950~970cm<supgt;‑1</supgt;范围内的峰值强度设为“A”,将拉曼光谱中的波数780~800cm<supgt;‑1</supgt;范围内的峰值强度设为“B”时,峰值强度比率(A/B)的平均值为0.040以下,生长面侧的峰值强度比率的平均值与基材面侧的峰值强度比率的平均值之差为0.040以下。

技术研发人员:杉原孝臣,牛岛裕次

受保护的技术使用者:东海炭素株式会社

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!