基于压电片可控纳米间隙的单分子结制备方法和应用

1.本发明属于纳米电极的技术领域,具体涉及一种基于压电片可控纳米间隙的单分子结制备方法。

背景技术:

2.随着半导体工艺特征尺寸缩小至十纳米以下,电极之间由隧穿效应所导致的漏电流将成为制约器件进一步小型化的关键技术挑战。分子具有合成成本低、结构多样性,可自组装等优点,利用单个分子自身特性来构建出具有特殊功能的分子器件成为当前分子电子学的研究热点。实现单分子功能器件的一个先决条件是能将微观的分子连接到宏观电路中测量并控制通过分子的电荷输运,因此制备电极-分子-电极结构的分子结成为首要任务。

3.而构建单分子结的关键就是使电极与分子之间通过化学键来稳定高效地连接起来。通常,单分子结的电极主要是由金属来充当,形成金属-单分子-金属结。金属点电极的加工工艺复杂,且难以精确控制电极的形貌及所测量的分子的数目。

4.目前获得单分子结的主要方法有机械可控裂结技术,扫描探针显微技术,纳米间隙电极的电化学沉积技术和电迁移技术。但是这些方法中,机械可控裂结技术可在针尖形的电极间提供连续可调的纳米间隙,具有高度的机械稳定性,但是机械可控裂结技术装置需要借助压电陶瓷或步进电机通过弯曲基片以改变电级间的距离,无法实现片上集成。

5.因此,如何提供一种片上可控纳米裂结的单分子结制备方法是本领域技术人员急需解决的问题。

技术实现要素:

6.鉴于此,本发明提供了一种基于压电片可控纳米间隙的单分子结制备方法,通过使用水平可膨胀压电片构建具有埃级调制分辨率的原位可调片上金属纳米间隙,进一步发展为平面内的断裂及连接,其中该纳米间隙可以重复断裂和连接数百万次,实现具有自由调节间隙尺寸的片上裂结;以单分子作为构建模块制造具有集成潜力的高产量片上分子器件提供技术支撑。

7.为实现上述目的,本发明采用如下技术方案:

8.一种基于压电片可控纳米间隙的单子分结制备方法,包括:压电片、驱动电极、绝缘层、带有预环切的金线;

9.其中,所述压电片为基片/衬底;所述压电片的上下表面均设置有驱动电极;

10.所述绝缘层位于所述驱动电极的上层;所述带有预环切的金线固定在所述绝缘层上;

11.当驱动电压施加至所述驱动电极时,夹在所述驱动电极中间的所述压电片将发生横向/水平变形,固定在所述绝缘层上的所述金线被相应拉伸,精确控制纳米间隙大小。

12.优选的,所述带有预环切的金线的制备方法如下:

13.1)在金线一的中间部分进行环切形成凹槽,将所述金线一切割成相对对称的沙漏

形;

14.2)将经过步骤1)处理的所述金线一固定在涂有绝缘胶的压电片上;

15.3)将金线二置于压电片的上层,且所述金线二的一端置于接近所述金线一的凹槽中心;

16.4)将电解质滴在所述凹槽附近的所述压电基片上,以浸没所述金线二的末端位置和金线一的凹槽部分;

17.5)在所述金线二上施加低电位,使其作为电化学反应的阴极,在所述金线一上施加高电位,使其作为阳极,通过电化学反应进行蚀刻;随着阳极的逐渐腐蚀,所述凹槽的直径减小。

18.优选的,步骤1)所述环切后凹槽直径为10-15μm;且经过步骤5)化学腐蚀后凹槽直径减小到≤1μm。

19.和/或,步骤2)所述压电基片为压电陶瓷基片;所述金线一通过环氧树脂固定在所述压电基片上;

20.和/或,步骤4)所述电解质为含有0.01摩尔每毫升的氯金酸和氯化硼1:1的水溶液。

21.优选的,所述压电片为纵向极化的矩形压电陶瓷片。

22.优选的,所述驱动电极为银膜,所述银膜分别镀在所述压电片的上下表面。

23.优选的,所述金线是通过粘结的方式固定在所述绝缘层上。

24.优选的,所述金线的拉伸断裂过程中通过电流信号分析仪测量通过所述金线的电流进行监控。

25.优选的,当驱动电压增加时,所述金线的凹槽部分将受到张力,凹槽的横截面减小,直至断裂,形成纳米间隙。

26.优选的,所述金线凹槽部分的最小直径为初始直径为1%,且悬空部分长度为初始直径的两倍,纳米桥的总拉伸长度为悬置部分长度的0.1%,其最大应变力产生在凹槽的最细部分。

27.本发明的另一目的是提供一种基于压电片可控纳米裂结制备单分子结的应用;将上述基于压电片可控纳米裂结的制备方法获得的单分子结在制备分子裂结阵列方面的应用。

28.经由上述的技术方案,与现有技术相比可知,本发明至少具有以下技术效果:

29.1)本发明考虑到面内集成和间隙可调的要求,提出了通过可横向膨胀的压电片实现片上可调纳米间隙的方法;

30.2)本发明原则上可以在基片/衬底上制作成千上万的平行电极对,为制作分子结阵列提供了技术支持;

31.3)本发明设计的方案每对电极的分离距离可以通过改变电极对的初始相对位置来独立调节,因此间隙尺寸调制精度及总间隙尺寸变化范围可以根据实际应用的需要进行微调;

32.4)芯片上的间隙可以调整并保持在亚纳米分辨率,提供了在极限光学的应用,例如尖端增强拉曼光谱、局域表面等离激元中的应用。

附图说明

33.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单的介绍,显而易见地,下面描述中的附图仅仅是本发明一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他附图。

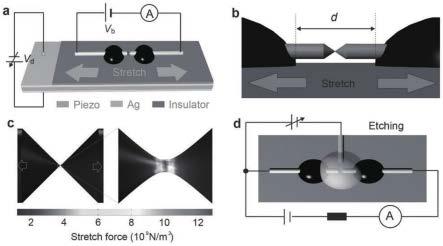

34.图1为本发明实施例1基于压电片可控纳米间隙的工作原理图。

35.图2为本发明实施例2不同驱动电压下不同电极间距的扫描电镜图像。

36.图3为本发明实施例3基于电子束光刻的可调片上纳米间隙的原理图。

具体实施方式

37.下面将对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

38.实施例1

39.本实施例提供了一种基于压电片可控纳米间隙的单子分结制备方法,包括:压电片、驱动电极、绝缘层、带有预环切的金线;

40.其中,压电片为基片/衬底;压电片的上下表面均设置有驱动电极;

41.绝缘层位于驱动电极的上层;带有预环切的金线固定在绝缘层上;

42.当驱动电压施加至驱动电极时,夹设在驱动电极中间的压电片将方法是横向/水平变形,固定在绝缘层上的金线被相应拉伸,精确控制纳米间隙大小。

43.为了进一步优化上述技术方案,带有预环切的金线的制备方法如下:

44.1)在金线一的中间部分进行环切,将金线一切割成相对对称的沙漏型;

45.2)将经过步骤1)处理的金线一固定在绝缘的压电片上;

46.3)将金线二置于压电片的上层,且金线二的一端置于接近金线一的凹槽中心;

47.4)将电解质滴在凹槽附近的压电片上,以浸没金线二的末端位置和金线一的凹槽部分;

48.5)在金线二上施加低电位,使其作为电化学反应的阴极,在金线一上施加高电位,使其作为阳极,通过电化学反应进行蚀刻;随着阳极的逐渐腐蚀,凹槽的直径减小。

49.为了进一步优化上述技术方案,步骤1)环切后凹槽直径为10-15μm;

50.和/或,步骤2)压电片为压电陶瓷片;金线一通过环氧树脂固定在压电片上;

51.和/或,步骤4)电解质为含有0.01摩尔每毫升的氯金酸和氯化硼1:1的水溶液。

52.为了进一步优化上述技术方案,压电片为纵向极化的矩形压电陶瓷片。

53.为了进一步优化上述技术方案,驱动电极为银膜,银膜分别镀在压电片的上下表面。

54.为了进一步优化上述技术方案,金线是通过粘结的方式固定在绝缘层上。

55.为了进一步优化上述技术方案,金线的拉伸断裂过程中通过电流信号分析仪测量通过金线的电流进行监控。

56.为了进一步优化上述技术方案,当驱动电压增加时,金线的凹槽部分将受到张力,

凹槽的横截面减小,直至断裂,形成纳米间隙。

57.为了进一步优化上述技术方案,金线凹槽部分的最小直径为初始直径为1%,且悬空部分长度为初始直径的两倍,纳米桥的总拉伸长度为悬空部分长度的0.1%,其最大应变力产生在凹槽的最细部分。

58.更进一步,金线的初始直径为100μm,凹槽的最小直径≤1μm,且悬空部分长度为200μm,纳米桥的总拉伸长度为200nm,其最大应变力产生在凹槽的最细部分,最大应变力为1.35

×

10

10

n/m2。

59.附图图1基于压电片可控纳米间隙的工作原理图。

60.其中a图为片上裂结技术的工作原理;纵向极化的压电陶瓷被用作衬底。当在衬底上施加驱动电压(vd)时,将产生横向形变,进而拉伸固定与其上方的金线,以产生分离的电极对。通过观测金线两端的电流监控金线的伸长程度。

61.b图为悬空部分金线的放大区域,具有凹槽的金线通过两滴黑胶固定在衬底上,初始间隔距离为d。凹槽部分将被拉长,直到下面的基底达到一定横向变形时最终断裂。

62.c图为模拟凹槽部分金线被拉伸时其周围的应力分布,具体为使用comsol软件包拉伸金线时的应力分布。

63.d图为减少凹槽部分的金线直径的蚀刻过程示意图。

64.实施例2

65.本实施例是在实施例1的基础上进一步验证:

66.控制间隙尺寸调制的精确度的能力对于建立分子器件是非常重要的。本实施例采用16位电压输出模块(0v~10v)来控制施加在压电片上的电压,即压电陶瓷片的横向变形。该电压通过线性放大器放大并施加到压电片上,以产生横向拉伸形变。压电陶瓷的形变与施加的驱动电压成线性比例,在最大驱动电压(v

max

)下,最大横向变形是压电片总长度(l)的0.1%。在施加的驱动电压(vd)下,两个黑胶固定金线点(d)之间的线的伸长率(δd)可以估计为:

67.δd=(l

×

0.1%)

×

(vd/v

max

)

×

(d/l)=vd/v

max

×

0.1%

×dꢀꢀ

(1)

68.那么所施加的驱动电压(v

min

)的最小步长是由输出模块确定的1mv,因此线的最小/最大伸长可以计算为:

69.δd

min

=v

min

/v

max

×

0.1%

×

d=1mv/10v

×

0.1%

×

d=10-7

×dꢀꢀ

(2)

70.δd

max

=v

max

/v

max

×

0.1%

×

d=10-3

×dꢀꢀ

(3)

71.附图2中可知:不同驱动电压下不同间距的金电极对的扫描电镜图像。

72.其中,a-c图为在粗略调节模式下,当施加1v、4v和10v的驱动电压时,电极分离的sem图像,分别获得约0.4μm,2.4μm和5.2μm的间隙尺寸。比例尺:2μm。箭头表示间隙尺寸增加的方向。此时,固定金线的两黑胶之间的初始距离d大约为8毫米。

73.d-f图为在精细调控模式下,当施加1v、4v和10v的驱动电压时,分别获得约82nm、124nm和232nm的间隙尺寸。比例尺:200nm。

74.基于公式(2),电极分离的最小步长(δd

min

)线性地依赖于两个固定点之间的初始距离(d),这为间隙尺寸控制提供了可调节的精度。

75.在精细模式下,金线由两滴距离较近的黑胶(例如,d≈1mm)固定,依据公式(2)可以得到δd

min

=10-7

×

d≈0.1nm,也就是说可以亚纳米精度精确调节间隙大小。在粗调模式

下,金线由相距较远的两滴黑胶(例如,d≈10mm)固定,根据公式(3),可以得到δd

max

=10-3

×

d≈10μm,也就是说,我们可以获得微米级别间隙变化范围。

76.实施例3

77.本实施例是在实施例1-2的基础上制作电极阵列

78.实施例1-2证明了在压电陶瓷上固定金属电极可以得到从亚纳米到微米的间隙尺寸,并具有可调的控制精度。

79.然而,产生数千个这样的电极阵列仍然是一个巨大的挑战,这对于实现高度集成的功能器件是必不可少的。为了制作电极阵列,实施例3利用光刻技术在压电陶瓷片上制作了纳米级金属桥。随着施加在压电陶瓷片即基板上的电压(vd)增加,固定在基板上的纳米桥将被拉长,直到最终断裂,如图3a所示。

80.为了制造样品,首先将聚(均苯四甲酸二酐-co-4,4

’‑

氧化二苯胺)酰胺酸(paa)溶液旋涂在压电陶瓷顶电极的上层,这可以将金纳米结构与压电陶瓷电绝缘,随后进行加热处理以固化绝缘层。接下来,采用标准光刻和反应离子蚀刻技术,在绝缘层上获得了具有对称凹槽(约80nm宽和约40nm厚)的悬浮纳米桥(d~2μm),如图3b所示。图3c-3e展示出了在不同驱动电压下凹槽位置的放大sem图像。它表明,当没有施加驱动电压时,可以观察到绝缘层上未拉伸的纳米桥(图3c)。当向压电片施加5v的驱动电压时,观察到纳米桥断裂和尺寸约为25nm的间隙(图3d)。当驱动电压增加到10v时,间隙尺寸扩大到大约42nm。

81.附图3a基于电子束光刻的可调片上纳米间隙的工作原理。

82.附图3b为样品的sem图像,比例尺:2μm。

83.附图3c悬浮纳米桥位于衬底上层,没有驱动电压(vb=0v),比例尺:200nm。

84.附图3d纳米桥被拉伸,当驱动电压(vb=5v)施加在下面的压电基板上时,观察到纳米间隙(~25nm),比例尺:200nm。

85.附图3e当施加驱动电压(~10v)时,纳米间隙增加到~42nm。比例尺:200nm。

86.对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1