电流检测芯片、电池及电子设备的制作方法

1.本技术涉及快速充电技术领域,具体涉及一种电流检测芯片、电池及电子设备。

背景技术:

2.随着智能时代的到来,软硬件的不断提升大大增加了手机等电子设备的功耗,由此,快充技术应运而生。在电池快充技术中,电池的电压快速变化,导致电池保护电路中的晶体管的导通阻抗变化,从而造成电池在充放电过程中的电流检测,影响用户的使用。

技术实现要素:

3.本技术提供一种提高电池在充放电过程中电流检测准确性的电流检测芯片、电池及电子设备。

4.第一方面,本技术实施例提供了一种电流检测芯片,用于电池在充放电过程中进行电流检测,包括:

5.电流补偿电路,用于生成第一补偿电流,所述第一补偿电流随着来自电池的电源电压的变化而线性变化;

6.比较电路,包括第一输入端及第二输入端;

7.选择电路,用于接收所述第一补偿电流,并选择所述第一补偿电流输入至所述比较电路的第一输入端或所述比较电路的第二输入端;

8.所述比较电路用于比较所述比较电路的第一输入端的电流和所述比较电路的第二输入端的电流,并根据比较结果输出指示信号,所述指示信号用于指示所述电池的充放电过程是否过流。

9.第二方面,本技术实施例提供了一种电池,包括电芯及所述的电流检测芯片,所述电流检测芯片电连接所述电芯,所述电流检测芯片用于在所述电芯的充放电过程进行电流检测。

10.第三方面,本技术实施例提供了一种电子设备,包括所述的电池。

11.通过设计电流检测芯片,使选择电路接收所述第一补偿电流,并选择所述第一补偿电流输入至所述比较电路的第一输入端或所述比较电路的第二输入端,如此,只需一个电流补偿电路产生第一补偿电流,通过选择电路选择性地将第一补偿电流输入至比较电路的第一输入端或比较电路的第二输入端,在较少的电流补偿电路的情况下,减小了在充电和放电回路中mos晶体管的导通阻抗变化导致第二输入端的电流检测不准确的问题。

附图说明

12.为了更清楚地说明本技术实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

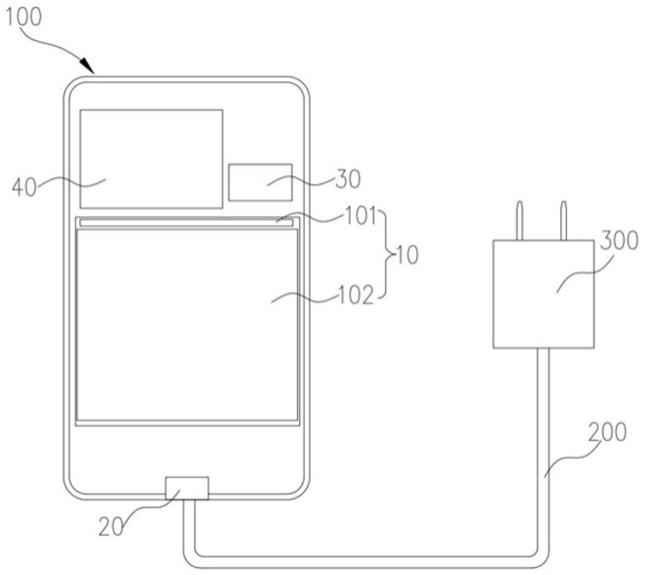

13.图1是本技术实施例提供的一种电子设备的应用场景的示意图;

14.图2是本技术实施例提供的一种电池的结构示意图;

15.图3是本技术实施例提供的一种电池保护板的电路结构示意图;

16.图4是本技术实施例提供的第一种放电模式下的电流检测的电路示意图;

17.图5是传统技术中放电模式下的电流检测的电路示意图;

18.图6是本技术实施例提供的一种充电模式下的电流检测的电路示意图;

19.图7是本技术实施例提供的第一种电流补偿电路的电路框图;

20.图8是本技术实施例提供的第一种电流补偿电路的结构示意图;

21.图9是本技术实施例提供的第一种放电模式下的电流检测的电路示意图;

22.图10是本技术实施例提供的第二种电流补偿电路的电路框图;

23.图11是本技术实施例提供的第二种电流补偿电路的局部结构示意图;

24.图12是本技术实施例提供的第三种电流补偿电路的局部结构示意图;

25.图13是本技术实施例提供的第四种电流补偿电路的结构示意图;

26.图14是本技术实施例提供的第五种电流补偿电路的局部结构示意图;

27.图15是本技术实施例提供的第二种电流补偿电路的电路框图;

28.图16是本技术实施例提供的第六种电流补偿电路的局部结构示意图。

具体实施方式

29.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。本技术所列举的实施例在没有相互违背的情况下可以适当的相互结合。

30.随着科技的发展,电子设备(例如智能手机、穿戴式设备、平板电脑等电子设备)的功能变得越来越强大,用户可以通过电子设备进行办公、娱乐,以至于电子设备已经成为人们日常生活中不可或缺的一部分。然而,电子设备的续航能力是有限的,需要用户不断的给电子设备充电。为了保证用户能够正常使用电子设备,快速充电成为一种充电的主流方案。

31.目前常见的快充技术主要可分为两大类:低压大电流快速充电技术、高压小电流快速充电技术。不论低压大电流快速充电还是高压小电流快速充电,在电子设备充电电路中输入到电池时都会被转换为更大的充电电流(该充电电流不能超过电池承载的最大安全充电电流或不损害电池寿命的安全充电电流),此时在对电池进行大电流充电如何保证快速充电的充电安全性就尤为重要。

32.请参阅图1,图1是适用于本技术实施例的一种应用场景。在图1所示的场景中,包括电子设备100、充电线200和充电器300。电子设备100包括但不限于手机、笔记本电脑、掌上电脑、可充电耳机、可充电音箱、可充电穿戴设备、机器人、可充电家电、可充电交通工具、可充电运输工具等可充电电子产品。充电器300通过充电线200与电子设备100电连接。电子设备100至少包括电池10、连接接口20、充电管理芯片30和负载40等。连接接口20与充电管理芯片30电连接。电池10分别与充电管理芯片30和负载40电连接。其中,电池10包括电池保护板101和电芯102。负载40可以是电子设备100中的耗电设备,例如,负载40可以是麦克风、摄像头、显示屏、马达等各种耗电设备。充电管理芯片30为管理所述电池10充电的芯片。充电时,电流流向为:充电器300

→

充电线200

→

连接接口20

→

充电管理芯片30

→

电池保护板101

→

电芯102。放电时,电流流向为:电芯102

→

电池保护板101

→

负载40。

33.电池10的充放电过程中,特别是对于快充技术领域,对于电池10的电流检测成为研究重点。一般通过设计电流检测芯片对电池10的充放电过程中的电流进行检测。电池10包括但不限于锂离子电池、金属锂电池等。

34.请参阅图2,电流检测芯片1可设于电池10的电池保护板101上,也可以设于电子设备100中且位于电池10外(例如电子设备100的主板上),还可以设于充电器300中。本技术实施例将该电流检测芯片1设于电池保护板101上为例进行说明。电流检测芯片1用于监测电池10的电流信息,当电流达到保护阈值时关断相应的充放电晶体管,达到对电池10保护的目的。

35.相关技术中,在不同的电源电压下,充放电mos(metal-oxide-semiconductor,金属-氧化物-半导体)晶体管会随着电源电压的高低而发生变化,导致电池保护板101所检测到的电流值不准确,进而导致电池保护板101对电池的过流保护不准确。电源电压为电连接电芯正极端的端口的电压。

36.本技术提供一种提高电池10在充放电过程中电流检测准确性的电流检测芯片。本技术中的应用场景包括电芯102、电池保护板101、放电负载(未图示)或外部充电设备(未图示)。电池保护板101上设有电流检测芯片1。当然,电池保护板101上还设有用于电压检测等功能的芯片。这些芯片可以相互独立的封装成多个芯片,芯片的引脚之间相互连接,或者,这些芯片可为共同封装成一个整体,换言之,本技术所述的电流检测芯片1可以为一个独立的芯片封装体也可以是一个芯片封装体内的一部分。为了便于被描述,请参阅图3,电池保护板101上还设有第一电池端接口bat+、第二电池端接口bat-、第一外部接口eb+及第二外部接口eb-。第一电池端接口bat+电连接电芯102正极端,第二电池端接口bat-电连接电芯102负极端,第一外部接口eb+电连接放电负载正极或外部充电设备的正极,第二外部接口eb-电连接负载负极或外部充电设备的负极。

37.请参阅图4,电流检测芯片1至少包括比较电路2、电流补偿电路3及选择电路4。

38.请参阅图4,比较电路2包括第一输入端21及第二输入端22。比较电路2的第一输入端21可为正极输入端,及比较电路2的第二输入端22可为负极输入端;或者,比较电路2的第一输入端21可为负极输入端,及比较电路2的第二输入端22可为正极输入端。本技术中,比较电路2的第一输入端21可为正极输入端,及比较电路2的第二输入端22可为负极输入端。

39.请参阅图3及图4,在放电模式下,电流依次流经电芯102正极端、第一电池端接口bat+、第一外部接口eb+、负载正极、负载负极、第二外部接口eb-、比较电路2的第二输入端22、比较电路2的第一输入端21、第二电池端接口bat-及电芯102负极端。在充电模式下,电流依次流经外部充电设备正极、第一外部接口eb+、第一电池端接口bat+、电芯102正极端、电芯102负极端、比较电路2的第一输入端21、比较电路2的第二输入端22、第二电池端接口bat-。

40.比较电路2为电流模比较电路。所述比较电路2用于在电池10充电和放电过程中,比较所述比较电路2的第一输入端21的电流和所述比较电路2的第二输入端22的电流,并根据比较结果输出指示信号,所述指示信号用于指示所述电池10的充放电过程是否过流。

41.具体的,比较电路2可对第一输入端21接收的电流信号以及所述第二输入端22接收的电流信号进行比较,并在第一输入端21的电流信号值大于第二输入端22的电流信号时输出指示信号。该指示信号可为高电平或低电平。当指示信号为高电平信号时,指示信号用

于控制电池10充放电回路的充电晶体管断开,及放电晶体管导通,以使电池10结束充电模式且转换成可放电模式,以对电池10进行充电过流保护;当指示信号为低电平信号时,指示信号用于控制电池10充放电回路的放电晶体管断开,及充电晶体管导通,以使电池10结束放电模式且转换成可充电模式,以对电池10进行放电过流保护。

42.可以理解的,充电回路和放电回路中皆具有mos晶体管。在mos晶体管的导通阻抗与驱动栅极的电压有关系。当电源电压vdd(vdd为图3中vdd端的电压)降低时,mos晶体管的驱动电压变小,导致mos晶体管的导通阻抗变大,当电源电压vdd增加时,驱动mos晶体管的电压变大,导致mos晶体管的导通阻抗变小,会造成比较电路2中的电流检测不准确,引起误触发过流保护的现象。

43.基于上述问题,本技术提供的电流检测芯片1包括电流补偿电路3及选择电路4。电流补偿电路3用于生成第一补偿电流。所述第一补偿电流随着电源电压vdd的变化而线性变化,以弥补mos晶体管的导通阻抗随着电源电压vdd的变化而变化产生的影响。

44.选择电路4用于接收所述第一补偿电流,并选择所述第一补偿电流输入至所述比较电路2的第一输入端21或所述比较电路2的第二输入端22。具体的,在放电回路中,mos晶体管的导通阻抗变化引起比较电路2的第一输入端21的电流检测不准确,选择电路4选择第一补偿电流对比较电路2的第一输入端21进行补偿,以减少mos晶体管的导通阻抗变化导致比较电路2的电流检测不准确,引起误触发过流保护的现象的问题。在充电回路中,mos晶体管的导通阻抗变化引起第二输入端22的电流检测不准确,选择电路4选择第一补偿电流对第二输入端22进行补偿,以减少mos晶体管的导通阻抗变化导致第二输入端22的电流检测不准确,引起误触发过流保护的现象的问题。如此,只需一个电流补偿电路3产生第一补偿电流,通过选择电路4选择性地将第一补偿电流输入至比较电路2的第一输入端21或比较电路2的第二输入端22,在较少的电流补偿电路3的情况下,减小了在充电和放电回路中mos晶体管的导通阻抗变化导致第二输入端22的电流检测不准确,引起误触发过流保护的现象的问题。

45.本技术针对电源电压vdd降低,导致mos晶体管的导通阻抗变大;电源电压vdd升高,导致mos晶体管的导通阻抗变小,故mos晶体管的导通阻抗随着电源电压vdd的变化呈反向变化的问题,通过补偿与电源电压vdd的变化线性相关的第一补偿电流,一方面以减小mos晶体管的导通阻抗变化对电流检测的影响,另一方面第一补偿电流对于mos晶体管的导通阻抗影响的补偿与电源电压vdd线性相关,即当mos晶体管的导通阻抗随着电源电压vdd增加较多时,第一补偿电流随着电源电压vdd增加较多以针对性地弥补mos晶体管的导通阻抗的影响。换言之,本技术使第一补偿电流随着电源电压vdd动态变化趋势,与mos晶体管的导通阻抗随着电源电压vdd的动态变化趋势相同或相近,以提高对mos晶体管的导通阻抗的影响的补偿准确性。在调节第一补偿电流的大小的过程中,第一补偿电流具有更好的线性度,能够更容易调节至抵消mos晶体管的导通阻抗全部影响的电流。

46.在一种可能的实施方式中,请参阅图3,电流检测芯片1包括电源电压端vdd、第一接地端gnd、充电管理端do、放电管理端co及第二接地端vm。

47.电池保护板101上还设有第一电阻r1、第一电容c1、第二电阻r2、放电mos晶体管q1、第一寄生二极管d1、充电mos晶体管q2、第二寄生二极管d2。

48.第一电阻r1的一端电连接电芯102正极端,第一电阻r1的另一端电连接电源电压

端vdd。电源电压端vdd的电压为电源电压vdd。

49.第一接地端gnd电连接电芯102负极端。第一电容c1的两端分别连接电源电压端vdd和第一接地端gnd。第一电阻r1及第一电容c1起滤波作用。第一电阻r1也有分压保护作用。

50.所述放电mos晶体管q1的源极与电芯102的负极端相连,所述放电mos晶体管q1的栅极为放电保护控制端,且与放电管理端co相连。

51.所述放电mos晶体管q1的漏极与充电mos晶体管q2的漏极相连,所述充电mos晶体管q2的源极与第二外部接口eb-相连,所述充电mos晶体管q2的栅极为充电保护控制端,与充电管理端do相连。放电mos晶体管q1可以根据其控制端的信号的控制导通或截止来导通或截至放电回路,因此,放电mos晶体管q1也可以被称为放电控制开关;充电mos晶体管q2可以根据其控制端的信号的控制导通或截止来导通或截至充电回路,因此,充电mos晶体管q2也可以被称为充电控制开关。

52.第二接地端vm为放电负载的地或者外部充电设备的地,由第二电阻r2与负载或者外部充电设备的地连接。

53.比较电路2的第一输入端21电连接第一接地端gnd,比较电路2的第二输入端22电连接第二接地端vm,比较电路2的输出端通过逻辑电路电连接充电管理端do、放电管理端co。比较电路2通过比较第一输入端21与第二输入端22之间的电流差值输出指示信号。例如,第一输入端21的电流值大于第二输入端22的电流值时,指示信号为高电平。第一输入端21的电流值小于或等于第二输入端22的电流值时,指示信号为低电平。该指示信号可控制放电mos晶体管q1断开及充电mos晶体管q2导通;或者控制放电mos晶体管q1导通及充电mos晶体管q2断开。

54.传统技术中,在放电模式下,比较电路2的等效电路图如图5所示,其中,电阻r提供比较器的固定失调电压vos。r为固定电阻。当放电电流大于k(vm-gnd)/r时,其中,k为实际电流与检测电流的比例系数,gnd为第一接地端gnd的电压,vm为第二接地端vm的电压。比较电路2的输出端out输出为高电平,触发过流保护;当放电电流小于k(vm-gnd)/r时,比较电路2的输出端out输出为低电平,不触发过流保护。

55.请参阅图4,当放电回路中的放电mos晶体管q1、充电mos晶体管q2的导通阻抗的影响等效为在比较电路2的第一输入端21与第一接地端gnd之间设置可变电阻r0,导致比较电路2的第一输入端21与第一接地端gnd之间存在一个变化的与栅压有关的

△

v(vdd),当放电电流大于k{vm-[gnd+

△

v(vdd)]}/r0时,比较电路2的输出端out输出为高电平,触发过流保护,当放电电流小于k{vm-[gnd+

△

v(vdd)]}/r0,比较电路2的输出端out输出为低电平,不触发过流保护。如此,过流保护的电流阈值发生变化,以引起过流保护不准的问题。请参阅图6,充电模式中,放电mos晶体管q1、充电mos晶体管q2的导通阻抗的影响等效为在比较电路2的第二输入端22与第二接地端vm之间设置可变电阻r0,在此不再赘述。

[0056]

本技术实施例的电流检测芯片1,在放电模式下,选择电路4将电流补偿电路3的输出端与比较电路2的第一输入端21导通。在放电过程中,电流补偿电路3产生的第一补偿电流会动态调整过放电流触发门限,防止过流保护的误触发的发生。电源电压vdd越低,充放电mos晶体管导通阻抗越大,给可变电阻r0补偿的电流越大,使触发过流的阈值越高,如此,抵消因充放电mos晶体管导通阻抗增大而对于放电流触发门限的影响;电源电压vdd越高,

充放电mos晶体管导通阻抗越小,给可变电阻r0补偿的电流越小,触发过流的阈值降低,以抵消因充放电mos晶体管导通阻抗减小而对于放电流触发门限的影响,如此,以实现随着电源电压vdd动态调整触发过流保护的阈值,以尽可能地消除充放电mos晶体管导通阻抗的变化对于过流保护的阈值的影响。

[0057]

换言之,当电源电压vdd改变时,放电mos晶体管q1和充电mos晶体管q2的导通电阻变化,等效于第二接地端vm与第一接地端gnd之间有一个可变电阻r0的存在,导致第二接地端vm与第一接地端gnd之间存在一个变化的与栅压有关的

△

v(vdd)。电源电压vdd越高,充放电mos晶体管的导通电阻越小,

△

v(vdd)变小。电源电压vdd降低,充放电mos晶体管的导通电阻变大,

△

v(vdd)变大。当比较电路2的第一输入端21加入第一补偿电流后,电源电压vdd越高,等效于在第二接地端vm补偿的电压

△

v越小;电源电压vdd越低,在第二接地端vm补偿的电压

△

v越大;当放电电流大于k{(vm+

△

v)-[gnd+

△

[0058]

v(vdd)]}/r0时,比较电路2的输出端out输出为高电平,触发过流保护;当放电电流小于k{(vm+

△

v)-[gnd+

△

v(vdd)]}/r0,比较电路2的输出端out输出为低电平,不触发过流保护。

[0059]

在一种可能的实施方式中,请参阅图7,所述电流补偿电路3包括第一电压生成模块31、补偿负载模块32和第二电压生成模块33。

[0060]

所述第一电压生成模块31用于接收第一输入电压并根据所述第一输入电压输出第一输出电压。第一输入电压与电源电压vdd线性相关。所述第一输出电压与第一输入电压线性相关。故第一输出电压与所述电源电压vdd线性相关。进一步地,所述第一输入电压为所述电源电压vdd的a倍。所述a的取值范围为0~1。

[0061]

所述第二电压生成模块33用于接收第二输入电压并根据所述第二输入电压输出第二输出电压。所述第二输入电压为基准电压vref。第二输出电压与第二输入电压线性相关。基准电压vref是内部带隙基准(bandgap)产生参考电压。换言之,第二输出电压与基准电压vref线性相关。

[0062]

所述第二输出电压加载于所述补偿负载模块32的输入端。所述第一输出电压加载于所述补偿负载模块32的输出端,以生成第二补偿电流i2。其中,所述第一补偿电流i1根据所述第二补偿电流i2得到。换言之,根据第二补偿电流i2可生成第一补偿电流i1。

[0063]

本实施方式实现在补偿负载模块32的相对两端分别加载第一输出电压和第二输出电压,以生成第二补偿电流i2,由于第一输出电压与所述电源电压vdd线性相关,第二输出电压与基准电压vref线性相关,进而第二补偿电流i2与电源电压vdd线性相关,如此,通过第二补偿电流i2生成的第一补偿电流i1也与电源电压vdd线性相关。以上可形成与电源电压vdd线性相关的第一补偿电流i1。

[0064]

在一种可能的实施方式中,请参阅图8,所述第一电压生成模块31包括第一运算放大器a1及第一晶体管p1。第一晶体管p1可为pmos晶体管或nmos晶体管。本实施例中,第一晶体管p1为pmos晶体管。所述第一运算放大器a1的第一输入端a1+用于加载所述第一输入电压。所述第一运算放大器a1的输出端电连接所述第一晶体管p1的栅极。所述第一运算放大器a1的第二输入端a1-连接所述第一晶体管p1的源极及所述补偿负载模块32的输出端。所述第一晶体管p1的漏极接地。

[0065]

在第一运算放大器a1为理想情况下,第一运算放大器a1的第二输入端a1-的电压

与第一运算放大器a1的第一输入端a1+的电压值相等,第一输出电压与第二输入端22的电压相等。补偿负载模块32的输出端的电压为a倍的电源电压vdd。通过设置第一运算放大器a1及第一晶体管p1,以将第一运算放大器a1的输入电压在理想情况下完全输出,以使补偿负载模块32的输出端的电压为a倍的电源电压vdd。在非理想的情况下,补偿负载模块32的输出端的电压为与a倍的电源电压vdd线性相关的电压值。

[0066]

请参阅图8,所述第二电压生成模块33包括第二运算放大器a2及第二晶体管n1。第二晶体管n1可为pmos晶体管或nmos晶体管。本实施例中,第二晶体管n1为nmos晶体管。所述第二运算放大器a2的第一输入端a2+用于加载所述第二输入电压。所述第二运算放大器a2的输出端电连接所述第二晶体管n1的栅极。所述第二运算放大器a2的第二输入端a2-连接所述第二晶体管n1的源极及所述补偿负载模块32的输入端。

[0067]

在第二运算放大器a2为理想情况下,第二运算放大器a2的第二输入端a2-的电压与第二运算放大器a2的第一输入端a2+的电压值相等,第二输出电压与第二输入端22的电压相等。补偿负载模块32的输入端的电压为基准电压vref。通过设置第二运算放大器a2及第二晶体管n1,以将第二运算放大器a2的输入电压在理想情况下完全输出,以使补偿负载模块32的输入端的电压为基准电压vref。在非理想的情况下,补偿负载模块32的输入端的电压为与基准电压vref线性相关的电压值。

[0068]

通过以上的设计,以实现在补偿负载模块32的输入端加载基准电压vref,在补偿负载模块32的输出端加载a倍的电源电压vdd,如此,生成与电源电压vdd线性相关的第二补偿电流i2。

[0069]

当然,在其他实施方式中,可在补偿负载模块32的输入端加载a倍的电源电压vdd,在补偿负载模块32的输出端加载基准电压vref,如此,生成与电源电压vdd线性相关的第二补偿电流i2。

[0070]

请参阅图7及图8,所述电流补偿电路3还包括电流镜像模块34。所述电流镜像模块34包括呈镜像对称且电连接的第一输出单元341及第二输出单元342。所述第一输出单元341的输入端和所述第二输出单元342的输入端皆加载所述电源电压vdd。所述第一输出单元341的输出端输出第二补偿电流i2。所述第二输出单元342的输出端用于输出所述第一补偿电流i1。所述第一补偿电流i1与所述第二补偿电流i2呈线性相关。

[0071]

具体的,第一输出单元341和第二输出单元342皆为晶体管,其中,第一输出单元341和第二输出单元342的类型可为pmos晶体管或nmos晶体管。本实施例中,第一输出单元341和第二输出单元342皆为pmos晶体管。

[0072]

由于第一输出单元341与第二输出单元342镜像对称设置,第二输出单元342的输出端的电流与第一输出单元341的输出端的电流相等,如此,根据第二补偿电流i2生成第一补偿电流i1,第一补偿电流i1的大小与第二补偿电流i2的大小相同。

[0073]

具体的,请参阅图8,电流补偿电路3至少包括:第一晶体管p1、第三晶体管p2、第四晶体管p3、第二晶体管n1、第三电阻r3、第一运算放大器a1、第二运算放大器a2。第三晶体管p2的栅极和第四晶体管p3的栅极相接,第三晶体管p2的源极和第四晶体管p3的源极都接电源电压vdd。第四晶体管p3的漏极接输出第一补偿电流i1,第三晶体管p2的漏极接第二晶体管n1漏极,第二晶体管n1的漏极接第三晶体管p2的漏极,第二晶体管n1的栅极接第二运算放大器a2的输出段,第二晶体管n1的栅极接第二运算放大器a2的第二输入端a2-,第二运算

放大器a2的第一输入端a2+接基准电压vref,第二运算放大器a2的第二输入端a2-接第二晶体管n1的源极,第二运算放大器a2的输出端接第二晶体管n1的栅极。第三电阻r3一端接第二晶体管n1的源极,一端接第一晶体管p1的源极。第一晶体管p1的源极接第一运算放大器a1的第二输入端a1-,第一晶体管p1的漏极接地,第一晶体管p1的栅极接第一运算放大器a1的输出端。第一运算放大器a1的第二输入端a1-接第一晶体管p1的源极,第一运算放大器a1的第二输入端a1-接电源电压vdd的分压电路,分压电路的输入电压为vbat,vbat的大小为a*vdd,其中a为vdd分压比例,第二补偿电流i2大小为i2=(vref-a*vdd)/r3。补偿后可以得到,当放电电流大于k{(vm+i1*r0)-[gnd+

△

v(vdd)]}/r0时,比较电路2的输出端out输出为高电平,触发过流保护;当放电电流小于k{(vm+i1*r0)-[gnd+

△

v(vdd)]}/r0,比较电路2的输出端out输出为低电平,不触发过流保护。其中,i1*r0可抵消因充放电mos晶体管的导通阻抗变化而引起的影响电压

△

v(vdd),如此,可提高过流保护的准确性。

[0074]

请参阅图9,所述选择电路4包括第一控制模块41、第一开关模块42和第二开关模块43。所述第一开关模块42电连接所述比较电路2的第一输入端21与所述第二输出单元342的输出端。所述第二开关模块43电连接所述比较电路2的第二输入端22与所述第二输出单元342的输出端。所述第一控制模块41用于在放电模式下控制所述第一开关模块42导通且所述第二开关模块43断开,以使所述比较电路2的第一输入端21接收所述第一补偿电流i1,进而在放电模式下进行电流补偿,以提高过流保护的准确性。

[0075]

所述第一控制模块41用于在充电模式下控制所述第二开关模块43导通且所述第一开关模块42断开,以使所述比较电路2的第二输入端22接收所述第一补偿电流i1,进而在充电模式下进行电流补偿,以提高过流保护电流检测的准确性。

[0076]

需要说明的是,在第一补偿电流i1进行补偿时,可进行多次检测,不同次的检测的第一补偿电流i1的大小不同,换言之,在多次检测过程中不断地调节第一补偿电流i1的大小,根据比较电路2的输出值确定较佳的第一补偿电流i1,以更多地抵消mos晶体管的导通阻抗带来的影响,提高过流保护中电流检测的准确性。

[0077]

在一种可能的实施方式中,请参阅图10及图11,所述第二输出单元342的数量为多个。每个第二输出单元342皆与第一输出单元341镜像对称设置。所述多个第二输出单元342并联设置。所述电流补偿电路3还包括输出选择模块35。所述输出选择模块35的一端电连接每个所述第二输出单元342的输出端。所述输出选择模块35的另一端电连接所述第一开关模块42和所述第二开关模块43。所述第一控制模块41用于控制所述输出选择模块35选择接收一个或多个第二输出单元342的所述第一补偿电流i1。

[0078]

请参阅图11,所述输出选择模块35包括多个第一开关单元351,每个第一开关单元351的一端电连接一个第二输出单元342。每个第一开关单元351的另一端电连接第一开关模块42和第二开关模块43。第一开关单元351可以为晶体管,第一控制模块41用于控制每个所述第一开关单元351的栅极电平,以控制第一开关单元351导通的数量。请结合参阅图9,第一开关模块42包括第二开关单元421,第二开关模块43包括第三开关单元431。第二开关单元421的一端与输出选择模块35的输出端连接,第三开关单元431的一端与输出选择模块35的输出端连接,第二开关单元421与比较电路2的第一输入端21电连接,第三开关单元431与比较电路2的第二输入端22电连接。

[0079]

在放电模式中,第一控制模块41控制第二开关单元421导通,及第三开关单元431

断开,并控制第一开关单元351导通的数量,以控制比较电路2的第一输入端21接收的补偿电流。举例而言,第一控制模块41控制一个第一开关单元351导通,以控制比较电路2的第一输入端21接收的补偿电流为一个输出单元输出的第一补偿电流i1;第一控制模块41控制2个第一开关单元351导通,以控制比较电路2的第一输入端21接收的补偿电流为2倍的第一补偿电流i1。在充电模式,第一控制模块41控制第三开关单元431导通,及第二开关单元421断开,并控制第一开关单元351导通的数量,以控制比较电路2的第二输入端22接收的补偿电流。

[0080]

通过设置多个并联的第二输出单元342,并控制输出选择模块35选择多个第二输出单元342中输出的第一补偿电流i1的分支数量,以使比较电路2的第一输入端21或第二输入端22接收n倍的第一补偿电流i1,n为正整数,从而基于第二补偿电流i2调大比较电路2的第一输入端21或第二输入端22接收的补偿电流。

[0081]

在另一种可能的实施方式中,请参阅图12,本实施方式与上述实施方式大致相同,与上述实施方式不同的是,所述多个第二输出单元342串联设置。所述输出选择模块35的一端电连接每个所述第二输出单元342的输出端。所述输出选择模块35的另一端电连接所述第一开关模块42和所述第二开关模块43。所述第一控制模块41用于控制所述输出选择模块35选择接收一个或多个第二输出单元342的所述第一补偿电流i1。

[0082]

在放电模式中,第一控制模块41控制第二开关单元421导通,及第三开关单元431断开,并控制第一开关单元351导通的数量,以控制比较电路2的第一输入端21接收的补偿电流。举例而言,第二输出单元342的数量总数为10个,10个第二输出单元342依次串联,且第二输出单元342的栅极皆电连接第一输出单元341的栅极。第一控制模块41控制第一个第一开关单元351导通,以控制比较电路2的第一输入端21接收的补偿电流为1倍的第一补偿电流i1;第一控制模块41控制前5个第一开关单元351导通,以控制比较电路2的第一输入端21接收的补偿电流为0.5倍的第一补偿电流i1;第一控制模块41控制10个第一开关单元351导通,以控制比较电路2的第一输入端21接收的补偿电流为0.1倍的第一补偿电流i1。充电模式的情形与放电模式相似,在此不再赘述。

[0083]

通过设置多个串联的第二输出单元342,并控制输出选择模块35选择多个第二输出单元342的有效数量,以使比较电路2的第一输入端21或第二输入端22接收n倍的第一补偿电流i1,n的范围为0~1,从而基于第二补偿电流i2调小比较电路2的第一输入端21或第二输入端22接收的补偿电流。

[0084]

在再一种可能的实施方式中,本实施方式与上述两种实施方式的主要的不同在于,所述多个第二输出单元342中一部分串联设置,另一部分并联设置。所述第一开关模块42电连接每个所述第二输出单元342的输出端。所述第一控制模块41用于控制所述第一开关模块42选择一个或多个第二输出单元342的输出端与所述比较电路2的第一输入端21或所述比较电路2的第二输入端22导通。

[0085]

通过设置多个串联和并联的第二输出单元342,并控制输出选择模块35选择多个第二输出单元342的有效数量,以使比较电路2的第一输入端21或第二输入端22接收n倍的第一补偿电流i1,n可大于1也可小于1,且n不限于为整数,从而基于第二补偿电流i2更为灵活比较电路2的第一输入端21或第二输入端22接收的补偿电流。本实施方式的比较电路2的第一输入端21或第二输入端22接收的补偿电流的调节范围相较于上述的两种实施方式更

加灵活,可调的参数范围相对更大。

[0086]

在一种可能的实施方式中,请参阅图13,所述第二输出单元342的数量为多个。所述多个第二输出单元342包括第一子输出单元343及第二子输出单元344。所述第一子输出单元343的输出端用于输出第一子补偿电流。所述第二子输出单元344的输出端用于输出第二子补偿电流。所述第一补偿电流i1根据所述第一子补偿电流或所述第二子补偿电流生成。第一子输出单元343与第一输出单元341镜像对称,且第一子输出单元343与第一输出单元341的栅极电连接,第一子输出单元343与第一输出单元341的源极电连接。第二子输出单元344与第一输出单元341镜像对称,且第二子输出单元344与第一输出单元341的栅极电连接,第二子输出单元344与第一输出单元341的源极电连接。第一子输出单元343、第二子输出单元344皆可为晶体管。第一子补偿电流的大小与第二补偿电流i2的大小相同,第二子补偿电流的大小与第二补偿电流i2的大小相同。

[0087]

进一步地,所述选择电路4包括第一控制模块41、第一开关模块42和第二开关模块43。所述第一开关模块42电连接所述比较电路2的第一输入端21与所述第一子输出单元343的输出端。所述第二开关模块43电连接所述比较电路2的第二输入端22与所述第二子输出单元344的输出端。所述第一控制模块41用于在放电模式下控制所述第一开关模块42导通且所述第二开关模块43断开,以使所述第一子补偿电流输入至所述比较电路2的第一输入端21;或者,所述第一控制模块41在充电模式下用于控制所述第二开关模块43导通且所述第一开关模块42断开,以使所述第二子补偿电流输入至所述比较电路2的第二输入端22。

[0088]

所述比较电路2的第一输入端21还用于接收第一输入电流。所述比较电路2的第二输入端22还用于接收第二输入电流。第一输入电流为第一接地端的电流,第二输入电流为第二接地端的电流。

[0089]

可选的,所述第一输入电流为从所述电池10端流出的电流。所述第二输入电流为流入负载端的电流。所述负载端为电池10放电的器件。所述第一输入电流用于与所述第一补偿电流i1合成所述比较电路2的第一输入端21的电流。

[0090]

再可选的,所述第一输入电流为流入所述电池10端的电流。所述第二输入电流为从充电设备端流出的电流。所述充电设备端为给所述电池10充电的外部充电设备。所述第二输入电流用于与所述第二补偿电流i2合成所述比较电路2的第二输入端22的电流。

[0091]

在一种可能的实施方式中,请参阅图14,所述补偿负载模块32包括多个第一负载单元321、第一负载选择模块322及第二控制模块323。所述多个第一负载单元321并联设置;或者,所述多个第一负载单元321串联设置;或者,所述多个第一负载单元321中一部分串联设置,另一部分并联设置。所述第一负载选择模块322电连接于所述第一电压生成模块31的第一输入端21与全部所述第一负载单元321的输出端。所述第二控制模块323用于控制所述第一负载选择模块322选择一个或多个所述第一负载单元321与所述第一电压生成模块31导通。

[0092]

第一负载单元321可为电阻。第一负载选择模块322可为多个第四开关单元324,每个第四开关单元324电连接一个第一负载单元321和第一电压生成模块31的第一输入端21。第二控制模块323通过控制第四开关单元324的通断,以控制第一负载单元321的并联数量或串联数量,从而调节多个第一负载单元321的总阻值,从而调节第二补偿电流i2的大小,进而调节比较电路2的第一输入端21或第二输入端22接收的补偿电流。本实施方式可在补

偿负载模块32进行负载阻值调节,以实现不同的第二补偿电流i2的输出,无需增加第二输出单元342的数量,可减小电流镜像模块34的复杂度和占据的面积。

[0093]

在一种可能的实施方式中,请参阅图15,所述电流补偿电路3还包括输入电压调整电路36。所述输入电压调整电路36用于生成所述第一输入电压并调节所述第一输入电压的大小。

[0094]

请参阅图16,所述输入电压调整电路36包括多个第二负载单元361、第二负载选择模块362及第三控制模块363。所述多个第二负载单元361并联设置;或者,所述多个第二负载单元361串联设置;或者,所述多个第二负载单元361中一部分串联设置,另一部分并联设置;所述第二负载选择模块362电连接全部所述第二负载单元361的输出端与所述第一电压生成模块31的第二输入端22。所述第三控制模块363用于控制所述第二负载选择模块362选择一个或多个所述第二负载单元361与所述第一电压生成模块31导通。

[0095]

第二负载单元361可为电阻。第二负载选择模块362可为多个第五开关单元364,每个第五开关单元364电连接一个第二负载单元361和第一电压生成模块31的第二输入端22。第三控制模块363通过控制第五开关单元364的通断,以控制第二负载单元361的并联数量或串联数量,从而调节多个第二负载单元361的总阻值,从而调节分压电路的电压vbat,即调节a的值,进而调节第二补偿电流i2,以调节比较电路2的第一输入端21或第二输入端22接收的补偿电流。

[0096]

本实施方式通过设计分压电路,并设置第二控制模块323控制第二负载选择模块362中第五开关单元364的通断,形成不同的分压电阻,从而调节第一电压生成模块31的第一输入电压,进而调节第二补偿电流i2。本实施方式可对第一输入电压进行电压调节,以实现不同的第二补偿电流i2的输出,无需增加第二输出单元342的数量,可减小电流镜像模块34的复杂度和占据的面积。

[0097]

可以理解的,以上的补偿电流的调节方式可以相互结合,以实现更加灵活的调节。

[0098]

本技术提供的一种电流检测芯片1,在电源电压vdd过低时,对充放电mos晶体管进行内阻补偿,以防止保护电路误触发。在电源电压vdd过低时,对充放电mos晶体管进行内阻补偿,使其随栅压变化的幅度变小,以防止保护电路误触发。

[0099]

本技术实施例还提供了一种电池10,包括电芯102及上述任意一实施方式所述的电流检测芯片1。所述电流检测芯片1电连接所述电芯102。所述电流检测芯片1用于在所述电芯102的充放电过程进行电流检测。

[0100]

本技术实施例还提供了一种电子设备100,电子设备100包括所述的电池10。

[0101]

以上所述是本技术的部分实施方式。应当指出。对于本技术领域的普通技术人员来说。在不脱离本技术原理的前提下。还可以做出若干改进和润饰。这些改进和润饰也视为本技术的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1