用于芯片测试的射频校准装置及其校准方法与流程

1.本发明涉及射频测量技术领域,尤其涉及一种用于芯片测试的射频校准装置及其校准方法。

背景技术:

2.通常在射频芯片的测试前,需要对射频通路进行校准。然而现有的校准方式由于仪器的外接线缆均为同轴线缆,因此校准的层次仅仅能达到测试机接口到承载板(load board)的水平。并未考虑到承载板中射频走线、夹具及其探针的性能对射频通路的影响,尤其是探针在不同频点下的驻波比的很大差异对于测试的准确度有很大的影响。对此,在一些高端射频芯片的测试中,常常需要采用更高端的配套承载板与探针来减少影响,但效果并不理想,系统引起的较大且无法估计的系统误差仍未消除,且更换高端测试用具造成的测试成本依旧很大。

技术实现要素:

3.本发明的目的在于提供一种用于芯片测试的射频校准装置,不仅制作成本低,还能减少系统误差。

4.本发明的另一目的在于提供一种射频校准装置的校准方法,能够减少系统误差。

5.为实现上述目的,本发明提供一种用于芯片测试的射频校准装置,用于测量测试机至探针之间的校准值,其包括:

6.第一基板,所述第一基板包括多个第一下接触盘和与多个所述第一下接触盘对应导通的多个第一上接触盘,多个所述第一下接触盘被配置为与各探针对应接触;

7.第一电路板,多个所述第一上接触盘焊接在所述第一电路板,所述第一电路板设置有多个第一测试接口,多个所述第一测试接口分别与多个所述第一上接触盘电性连接,多个所述第一测试接口被配置为与测试机或测试仪器连接。

8.较佳地,所述第一基板为陶瓷基板,所述陶瓷基板通过制作过孔、抛光减薄、双面覆铜、刻蚀后形成,所述陶瓷基板上的多个过孔处相应地形成有所述第一上接触盘和所述第一下接触盘。

9.较佳地,所述第一基板的尺寸与待测芯片的尺寸相当。

10.较佳地,所述第一测试接口为rf线缆接口。

11.较佳地,所述射频校准装置还包括第二基板,所述第二基板包括第二下接触盘和与所述第二下接触盘对应导通的第二上接触盘,所述第二下接触盘连接有第二测试接口,所述第二上接触盘焊接在所述第一电路板;

12.所述第一电路板还设有第三测试接口,所述第三测试接口与所述第二上接触盘电性连接;

13.所述第二测试接口和所述第三测试接口被配置为与测试机或测仪仪器连接。

14.较佳地,所述射频校准装置还包括第二基板和第二电路板;

15.所述第二基板包括第二下接触盘和与所述第二下接触盘对应导通的第二上接触盘,所述第二下接触盘连接有第二测试接口,所述第二上接触盘焊接在所述第二电路板;

16.所述第二电路板设有第三测试接口,所述第三测试接口与所述第二上接触盘电性连接;

17.所述第二测试接口和所述第三测试接口被配置为与测试机或测仪仪器连接。

18.较佳地,所述第二测试接口和所述第三测试接口为rf线缆接口。

19.较佳地,所述第一测试接口、所述第二测试接口、所述第三测试接口以及所述测试机的测试接口相同或者造成大致相同的测试误差。

20.为了实现上述另一目的,本发明提供一种如上所述的射频校准装置的校准方法,其包括:

21.将所述射频校准装置连接至探针,多个所述第一测试接口、所述第二测试接口和所述第三测试接口分别连接至测试机或测试仪器;

22.测试机发送激励至各探针,测量所述第一测试接口的输出信号大小以获取初始校准值;

23.测试机发送激励至所述第二测试接口和所述第三测试接口之一者,测量所述第二测试接口和所述第三测试接口之另一者的输出信号大小以获取补偿值;

24.根据所述初始校准值和所述补偿值得到补偿后校准值。

25.较佳地,所述校准方法还包括利用分类机模拟真实芯片测试的环境去压住所述射频校准装置。

26.与现有技术相比,本发明射频校准装置将多个与各探针对应接触的第一下接触盘集成在同一第一基板,并通过多个第一上接触盘将第一基板与第一电路板连接,多个第一测试接口分别与对应的第一上接触盘电性连接,形成多个测试通路。在进行射频校准时,将射频校准装置安装在底座(socket)上,即可将各第一下接触盘与各个探针对应接触,同时将多个第一测试接口分别与测试机或测试仪器连接,当测试机发送激励至各探针时,即可通过与各第一测试接口连接的测试机或测试仪器测量输出数值。由此可知,本发明射频校准装置采用简单结构即可完成测量,有效降低制作成本,还能减少系统误差。

附图说明

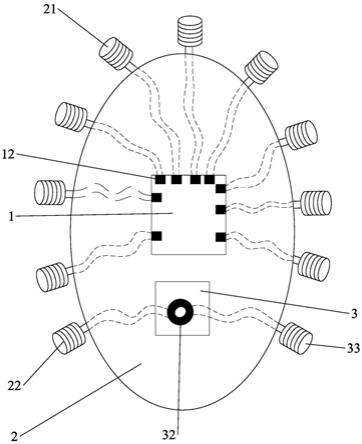

27.图1是本发明实施例射频校准装置的结构示意图。

28.图2是本发明实施例射频校准装置的侧视图。

29.图3是本发明另一实施例的侧视图。

30.图4是本发明实施例射频校准装置的校准方法的流程示意图。

具体实施方式

31.为了详细说明本发明的技术内容、构造特征,以下结合实施方式并配合附图作进一步说明。

32.在本发明的描述中,需要理解的是,术语“上”、“下”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为便于描述本发明和简化描述,因而不能理解为对本发明保护内容的限制。

33.请参阅图1和图2,本发明提供一种用于芯片测试的射频校准装置,用于测量测试机至探针之间的校准值,其包括第一基板1和第一电路板2。第一基板1包括多个第一下接触盘11和与多个第一下接触盘11对应导通的多个第一上接触盘12,多个第一下接触盘11被配置为与各探针对应接触。多个第一上接触盘12焊接在第一电路板2,第一电路板2设置有多个第一测试接口21,多个第一测试接口21分别与多个第一上接触盘12电性连接,多个第一测试接口21被配置为与测试机或测试仪器连接。

34.本发明射频校准装置将多个与各探针对应接触的第一下接触盘11集成在同一第一基板1,并通过多个第一上接触盘12将第一基板1与第一电路板2连接,多个第一测试接口21分别与对应的第一上接触盘12电性连接,形成多个测试通路。在进行射频校准时,将射频校准装置安装在底座(socket)上,即可将各第一下接触盘11与各个探针对应接触,同时将多个第一测试接口21分别与测试机或测试仪器连接,当测试机发送激励至各探针时,即可从第一测试接口21测量输出数值。由此可知,本发明射频校准装置采用简单结构即可完成测量,有效降低制作成本,还能减少系统误差。

35.具体地,各探针设置在底座(socket)上,底座的底部连接有承载板(load board),承载板与各探针导通,且承载板设置有与测试机或测试仪器连接的测试接口。当测试机发送激励至各探针时,从第一测试接口21测量的输出数值涵盖承载板中射频走线、底座及其探针对射频通路造成的误差。

36.下面,以具体实施例为例并结合附图对本发明射频校准装置进行详细说明。

37.请参阅图1和图2,在一些实施例中,第一基板1为陶瓷基板,陶瓷基板通过制作过孔、抛光减薄、双面覆铜、刻蚀后形成,陶瓷基板上的多个过孔13处相应地形成有第一上接触盘12和第一下接触盘11。

38.通过上述技术手段,采用先进的工业制程,较好地将第一上接触盘12和第一下接触盘11配置在第一基板1,能够减少元件间的损耗,使测量更加精确。

39.在一些实施例中,第一基板1的尺寸与待测芯片的尺寸相当。通过上述技术手段,有利于第一基板1固定在底座的测试区,使各第一下接触盘11更好地与对应的探针接触,更好地达到模拟待测芯片的效果。

40.在一些实施例中,第一测试接口21为rf线缆接口。通过上述技术手段,有利于减少线材带来的误差,同时增加装置的实用性,可与市面上较多的测试机或测试仪器连接使用。

41.在一些实施例中,射频校准装置还包括第二基板3,第二基板3包括第二下接触盘31和与第二下接触盘31对应导通的第二上接触盘32,第二下接触盘31连接有第二测试接口33,第二上接触盘32焊接在第一电路板2。第一电路板2还设有第三测试接口22,第三测试接口22与第二上接触盘32电性连接。第二测试接口33和第三测试接口22被配置为与测试机或测仪仪器连接。

42.在使用过程当中,将测试机或测试仪器分别与第二测试接口33和第三测试接口22连接,当测试机发送激励至第二测试接口33和第三测试接口22之一者,便可测量第二测试接口33和第三测试接口22之另一者的输出信号大小,即可测量出装置的补偿值。

43.通过上述技术手段,第二测试接口33至第三测试接口22之间构建测量该装置补偿值的通路,通过与测试机或测试仪器连接可直接测量,简单且便捷,提高了测试效率。

44.另外,第二基板3可采取与第一基板1的形状、材料及大小相似的基板,当然第二基

板3也可以与第一基板1结构不一致,在此不作限定。

45.请参阅图1和图3,在一些实施例中,射频校准装置还包括第二基板3和第二电路板4。第二基板3包括第二下接触盘31和与第二下接触盘31对应导通的第二上接触盘32,第二下接触盘31连接有第二测试接口33,第二上接触盘32焊接在第二电路板4。第二电路板4设有第三测试接口22,第三测试接口22与第二上接触盘32电性连接。第二测试接口33和第三测试接口22被配置为与测试机或测仪仪器连接。

46.进一步地,第二测试接口33和第三测试接口22为rf线缆接口。通过上述技术手段,有利于减少线材带来的误差,同时增加装置的实用性,可与市面上较多的测试机或测试仪器连接使用。

47.进一步地,第一测试接口21、第二测试接口33和第三测试接口22相同或者造成大致相同的测试误差。通过上述技术手段,有利于更加准确地利用第二测试接口33、第三测试接口22以及第二基板3等来获取补偿值以补偿射频校准装置自身引起的系统误差。

48.请参阅图4,本发明还提供一种上述射频校准装置的校准方法,其包括以下步骤:

49.s1、将射频校准装置连接至探针,多个第一测试接口21、第二测试接口33和第三测试接口22分别连接至测试机或测试仪器。

50.具体地,探针设置在底座(socket)的测试区中,射频校准装置与测试区连接。底座的底部连接有承载板(load board),承载板与各探针导通,且承载板设置有与测试机或测试仪器连接的测试接口,测试机或测试仪器与承载板的测试接口连接以发送激励。

51.s2、测试机发送激励至各探针,测量第一测试接口21的输出信号大小以获取初始校准值。

52.s3、测试机发送激励至第二测试接口33和第三测试接口22之一者,测量第二测试接口33和第三测试接口22之另一者的输出信号大小以获取补偿值。

53.具体地,补偿值是为了补偿装置自身引起的系统误差。

54.s4、根据初始校准值和补偿值得到补偿后校准值。

55.具体地,补偿后校准值为初始校准值与补偿值的差值。

56.通过上述方法,能够快速得出测试机至探针之间的校准值,而且能够利用补偿值对射频校准装置的自身误差进行修正,有利于在低成本下极大改善射频产品测试时的校准。

57.进一步地,校准方法还包括利用分类机(handler)模拟真实芯片测试的环境去压住射频校准装置。

58.通过上述方法,能够达到更好地模拟待测芯片的效果,增加测试的可靠性。

59.以上所揭露的仅为本发明的较佳实例而已,不能以此来限定本发明之权利范围,因此依本发明权利要求所作的等同变化,均属于本发明所涵盖的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1