一种3D堆叠封装集成电路芯片及其失效定位方法和装置与流程

一种3d堆叠封装集成电路芯片及其失效定位方法和装置

技术领域

1.本发明实施例涉及半导体器件检测技术领域,尤其涉及一种3d堆叠封装集成电路芯片及其失效定位方法和装置。

背景技术:

2.随着半导体晶圆制造趋向先进制程,摩尔定律面临巨大挑战。传统的覆晶封装、层叠封装等技术已不符合中央处理器(central processing unit,cpu)、图形处理器(graphics processing unit,gpu)、现场可编程逻辑门阵列(field programmable gate array,fpga)等高性能芯片的要求,因而2.5d/3d先进封装技术需求逐渐增加,成为解决高端产品应用和延续摩尔定律的核心技术之一。

3.但是,3d封装技术的发展,也给失效分析带来新的挑战。例如,对3d堆叠封装集成电路芯片的失效定位变得非常困难。器件包括很多层,可通过铟镓砷微光显微镜、增强型热成像仪等设备可有效地测量到失效信息,但无法确定这些信息来自哪个位置的膜层。因此如何对3d堆叠封装集成电路芯片进行失效定位,成为亟待解决的技术问题。

技术实现要素:

4.本发明实施例提供了一种3d堆叠封装集成电路芯片及其失效定位方法和装置,以实现对3d堆叠封装集成电路芯片的失效定位。

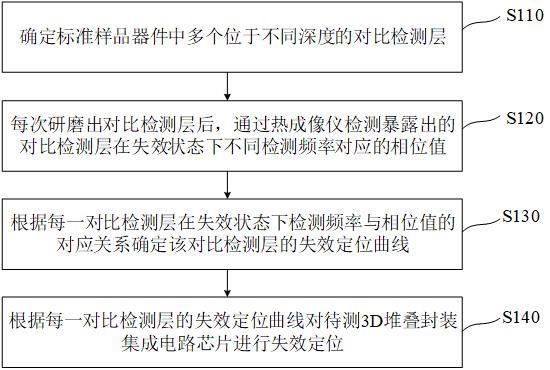

5.第一方面,本发明实施例提供了一种3d堆叠封装集成电路芯片的失效定位方法,包括:确定标准样品器件中多个位于不同深度的对比检测层;每次研磨出所述对比检测层后,通过热成像仪检测暴露出的所述对比检测层在失效状态下不同检测频率对应的相位值;根据每一对比检测层在失效状态下检测频率与相位值的对应关系确定该对比检测层的失效定位曲线;其中,所述失效定位曲线为对比检测层的相位值随检测频率变化的曲线;根据每一对比检测层的失效定位曲线对待测3d堆叠封装集成电路芯片进行失效定位;其中所述标准样品器件为所述待测3d堆叠封装集成电路芯片同类型未失效的3d堆叠封装集成电路芯片。

6.可选的,所述确定标准样品器件中多个位于不同深度的对比检测层,包括:根据所述标准样品器件的厚度确定多个位于不同深度的对比检测层;或者,根据所述标准样品器件所具有的功能膜层确定多个位于不同深度的对比检测层。

7.可选的,所述检测暴露出的所述对比检测层在失效状态下不同检测频率对应的相位值,包括:在暴露出的对比检测层的表面进行短路失效处理后,通过热成像仪从所述标准样

品器件远离研磨侧的一侧,检测暴露出的对比检测层在不同检测频率下的相位值。

8.可选的,根据所述标准样品器件的厚度确定多个位于不同深度的对比检测层,包括:根据预设厚度将所述标准样品器件划分为多层等厚度的备选对比层;间隔选取所述备选对比层作为所述对比检测层。

9.可选的,所述根据所述标准样品器件具有的功能膜层确定多个位于不同深度的对比检测层,包括:将所述标准样品器件具有的功能膜层确定为备选对比层;间隔选取所述备选对比层作为所述对比检测层。

10.可选的,所述标准样品器件的功能膜层包括:依次层叠设置的焊接球层、pcb基板、第一连接触点层、转接单元、第二连接触点层和顶层芯片;所述间隔选取所述备选对比膜层作为所述对比检测层包括:选取位于pcb基板远离所述转接单元的一侧的焊接球层、pcb基板与转接单元之间的第一连接触点层,以及所述转接单元与所述顶层芯片之间的第二连接触点层为对比检测层。

11.可选的,所述根据每一对比检测层的失效定位曲线对待测3d堆叠封装集成电路芯片进行失效定位之前,还包括:通过热成像仪检测所述待测3d堆叠封装集成电路芯片在不同检测频率下的相位值;其中,对所述待测3d堆叠封装集成电路芯片的检测频率范围位于对所述标准样品器件的检测频率范围内;根据所述待测3d堆叠封装集成电路芯片的检测频率与相位值的对应关系确定待测失效位置曲线;所述待测失效位置曲线为待测3d堆叠封装集成电路芯片的相位值随检测频率变化的曲线。

12.可选的,所述根据每一对比检测层的失效定位曲线对待测3d堆叠封装集成电路芯片进行失效定位,包括:根据每一对比检测层的失效定位曲线与所述待测失效位置曲线之间的相对距离,确定所述待测3d堆叠封装集成电路芯片失效膜层的位置。

13.第二方面,本发明实施例提供了一种3d堆叠封装集成电路芯片的失效定位装置,用于执行第一方面任一所述的3d堆叠封装集成电路芯片的失效定位方法,包括:对比检测层确定单元,用于确定标准样品器件中多个位于不同深度的对比检测层;相位值检测单元,用于在依次研磨出每层所述对比检测层后,通过热成像仪检测暴露出的所述对比检测层在失效状态下不同检测频率对应的相位值;失效定位曲线确定单元,用于根据每一对比检测层在失效状态下检测频率与相位值的对应关系确定该对比检测层的失效定位曲线;其中,所述失效定位曲线为对比检测层的相位值随检测频率变化的曲线;失效定位单元,用于根据每一对比检测层的失效定位曲线对待测3d堆叠封装集成电路芯片进行失效定位;其中所述标准样品器件为所述待测3d堆叠封装集成电路芯片同类型未失效的3d堆叠封装集成电路芯片。

14.第三方面,本发明实施例提供了一种3d堆叠封装集成电路芯片,包括多层层叠设置的膜层,通过第一方面任一所述的3d堆叠封装集成电路芯片的失效定位方法进行失效定位。

15.本发明实施例提供了一种3d堆叠封装集成电路芯片的失效定位方法,通过定义出标准样品器件中多个位于不同深度的对比检测层,并对标准样品器件进行研磨,依次研磨出所设定的对比检测层;在每次研磨出对比检测层后对对比检测层进行失效处理,使得对比检测层可以用来模拟3d堆叠封装集成电路芯片中发生失效的膜层,并在失效处理后通过热成像仪检测该对比检测层在失效状态下不同检测频率对应的相位值,从而可根据检测频率与相位值的对应关系确定出一条失效定位曲线;每层对比检测层均对应一条失效定位曲线;在对待测3d堆叠封装集成电路芯片进行失效对应时,无需对待测3d堆叠封装集成电路芯片进行研磨,通过匹配数据库,就可以推断失效位置所在层,达到失效分析准确定位的目的。

附图说明

16.图1是本发明实施例提供的一种3d堆叠封装集成电路芯片的失效定位方法的流程图;图2是本发明实施例提供的另一种3d堆叠封装集成电路芯片的失效定位方法的流程图;图3是本发明实施例提供的另一种3d堆叠封装集成电路芯片的失效定位方法的流程图;图4是本发明实施例提供的一种3d堆叠封装集成电路芯片的结构剖面图;图5是本发明实施例提供的一种不同深度对比检测层的相位值与检测频率关系图。

具体实施方式

17.下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

18.本发明实施例提供了一种3d堆叠封装集成电路芯片的失效定位方法,图1是本发明实施例提供的一种3d堆叠封装集成电路芯片的失效定位方法的流程图,参考图1,3d堆叠封装集成电路芯片的失效定位方法,包括:s110、确定标准样品器件中多个位于不同深度的对比检测层。

19.具体的,标准样品器件为待测3d堆叠封装集成电路芯片同类型未失效的3d堆叠封装集成电路芯片。同类型可以理解为标准样品器件的组成膜层以及每一组成膜层对应的位置与待测3d堆叠封装集成电路芯片的组成膜层以及每一组成膜层对应的位置相同。不同的膜层位于器件中不同的位置,即对应不同的深度。3d堆叠封装集成电路芯片发生失效可以理解为,3d堆叠封装集成电路芯片中某一位置的膜层发生短路等异常情况,从而影响了3d堆叠封装集成电路芯片正常工作的情况。

20.对比检测层可以为组成标准样品器件的功能膜层,例如标准样品器件包括从下至

上依次层叠设置的焊接球层、pcb基板、第一连接触点层、转接单元、第二连接触点层和多层顶层芯片构成,对比检测层可以为其中的全部或部分膜层。或者,也可以将标准样品器件根据预设厚度划分为多个膜层后,选取全部或部分的膜层作为对比检测层。预设厚度越小,选取的对比检测层的数量越多,对待测3d堆叠封装集成电路芯片的失效定位越精确。

21.s120、每次研磨出对比检测层后,通过热成像仪检测暴露出的对比检测层在失效状态下不同检测频率对应的相位值。

22.具体的,先进的封装应用、复杂的互连方案和更高性能的功率器件的快速增长给故障定位和分析带来了前所未有的挑战。有缺陷或性能不佳的半导体器件通常表现出局部功率损耗的异常分布,导致局部温度升高。例如3d堆叠封装集成电路芯片短路失效后,发生短路的位置会产生较高的温度成为热点,基于材料热传递性质,短路位置产生较高的温度会随着时间往低温处传递出去,进而传递到器件的外表面。

23.热成像仪(infrared thermal camera)是一种利用红外热成像技术,通过对被测目标的红外辐射探测,并加以信号处理、光电转换等手段,将被测目标的温度分布的图像转换成可视图像的设备。红外锁相热像检测技术是一种新型数字化无损检测技术,红外锁相热像检测技术是将红外热成像技术与数字锁相技术相结合,采用强度按正弦规律变化的外激励源对试件或材料进行激励,在构件表面引起的温度变化也为正弦规律变化,构件表面温度以加载频率振荡变化,其幅值与相位与材料特性有关,当样件结构内部存在缺陷时,则在样件有缺陷处与无缺陷处对应表面引起的温度变化将产生幅值和相位差异。通过增强型热成像仪监测幅值和相位的差异从而可有效地测量到失效信息,但无法确定这些信息来自哪个位置的膜层。

24.其中,lock-in thermography(锁相热成像)热传递相位差异与检测频率的理论关系基于以下确定:式中,为检测频率,为深度,为检测到的相位值。根据公式可知,在某一深度的热点,其相位和频率关系具有正相关关系,并且不同深度的热点,在同一检测频率下,对应的相位值不同。

25.基于此,根据相位值和频率关系可推知热点的深度。通过定义对比检测层,将对比检测层作为3d堆叠封装集成电路芯片位于不同关键深度的膜层。将未失效的3d堆叠封装集成电路芯片作为标准样品器件,从标准样品器件的底部开始研磨,研磨出第一个定义的对比检测层,然后对对比检测层进行失效处理,使该对比检测层处于失效状态下。对标准样品器件通电后,该对比检测膜层会产生热辐射。通过热成像仪检测暴露出的对比检测层在失效状态下不同检测频率对应的相位值。继续对标准样品器件进行研磨至第二个定义的对比检测层,然后对对比检测层进行失效处理,使该对比检测层处于失效状态下。对标准样品器件通电后,该对比检测膜层会产生热辐射。通过热成像仪检测暴露出的对比检测层在失效状态下不同检测频率对应的相位值。依次类推下去,直至研磨至最后一层定义的对比检测

层,对其进行失效处理以及相位角的检测。

26.s130、根据每一对比检测层在失效状态下检测频率与相位值的对应关系确定该对比检测层的失效定位曲线。

27.具体的,在获取不同层对比检测层的检测频率与相位值的对应关系时,采用的检测频率可以相同也可以不同。优选的,不同层对比检测层的检测频率与相位值的对应关系时,采用的检测频率相同。例如在均使用频率1hz、2hz、4hz和6hz进行收集相位值。可以在后续对待测3d堆叠封装集成电路芯片进行失效定位时,同样使用这些相同的检测频率进行检测相位值,使得定位结果更加准确。

28.另外,在获取不同层对比检测层的检测频率与相位值的对应关系时,在同一个检测频率下可以多次检测相位值。例如在1hz、2hz、4hz和6hz下均收集三次相位值。然后将三个相位值的平均值作为对应检测频率下的相位值,可以减小检测误差,提高定位结果的准确性。以检测频率为横坐标,相位值作为纵坐标建立直角坐标系。将一对检测频率和相位值表示在直角坐标系作为一个坐标点,连接坐标点从而确定失效定位曲线。即失效定位曲线为对比检测层的相位值随检测频率变化的曲线。或者,多次测量后,将检测频率对应的多个相位值均表示为直角坐标系中的坐标点,然后选取数据收敛的测试结果作为失效定位曲线,同样可以减小检测误差,提高定位结果的准确性。

29.s140、根据每一对比检测层的失效定位曲线对待测3d堆叠封装集成电路芯片进行失效定位。

30.示例性的,表1为使用频率1hz、2hz、4hz和6hz收集不同对比检测的相位值。参考表1,确定标准样品器件中三个位于不同深度的对比检测层。其中第一对比检测层在标准样品器件的深度大于第二对比检测层在标准样品器件中的深度,其中第二对比检测层在标准样品器件的深度大于第三对比检测层在标准样品器件中的深度。第一对比检测层在1hz、2hz、4hz和6hz的检测频率下收集到的相位值分别为124.72、166.25、224.89、258.22;第二对比检测层在1hz、2hz、4hz和6hz的检测频率下收集到的相位值分别为55.71、78.88、109.47、127.06;第三对比检测层在1hz、2hz、4hz和6hz的检测频率下收集到的相位值分别为37.74、50.26、71.67、86.56。可以根据这些数据确定不同对比检测层的相位与检测频率的失效定位曲线。

31.在对待测3d堆叠封装集成电路芯片进行失效对应时,无需对失效的待测3d堆叠封

装集成电路芯片进行研磨,直接进行检测。例如在4hz的检测频率下,检测到的相位值为120,则可以判断待测3d堆叠封装集成电路芯片发生失效的位置位于第一对比检测层和第二对比检测层之间,从而实现推断失效位置所在层以及深度,达到失效分析准确定位的目的。另外,根据每一对比检测层在失效状态下检测频率与相位值的对应关系确定该对比检测层的失效定位曲线,曲线可以确定3 hz 、5hz等对应的非实验采集的相位值。因此,例如在5hz的检测频率下对待测3d堆叠封装集成电路芯片进行检测,获得相位值也可以与失效定位曲线上5hz对应的非实验采集的相位值进行比较,从而实现推断失效位置所在层以及深度,达到失效分析准确定位的目的。优选的,对待测3d堆叠封装集成电路芯片的检测评率为对标准样品器件的检测评率中的一个或多个,可以提高对待测3d堆叠封装集成电路芯片失效定位的准确性。

32.本发明实施例提供的3d堆叠封装集成电路芯片的失效定位方法,通过定义出标准样品器件中多个位于不同深度的对比检测层,并对标准样品器件进行研磨,依次研磨出所设定的对比检测层;在每次研磨出对比检测层后对对比检测层进行失效处理,使得对比检测层可以用来模拟3d堆叠封装集成电路芯片中发生失效的膜层,并在失效处理后通过热成像仪检测该对比检测层在失效状态下不同检测频率对应的相位值,从而可根据检测频率与相位值的对应关系确定出一条失效定位曲线;每层对比检测层均对应一条失效定位曲线;在对待测3d堆叠封装集成电路芯片进行失效对应时,无需对待测3d堆叠封装集成电路芯片进行研磨,通过匹配数据库,就可以推断失效位置所在层,达到失效分析准确定位的目的。

33.图2是本发明实施例提供的另一种3d堆叠封装集成电路芯片的失效定位方法的流程图,参考图2,3d堆叠封装集成电路芯片的失效定位方法包括:s210、根据标准样品器件的厚度确定多个位于不同深度的对比检测层。

34.具体的,根据标准样品器件的厚度确定多个位于不同深度的对比检测层可以包括:根据预设厚度将标准样品器件划分为多层等厚度的备选对比层;间隔选取备选对比层作为对比检测层。示例性的,将标准样品器件划分从下至上的六层备选对比层,分别为第一备选对比层、第二备选对比层、第三备选对比层、第四备选对比层、第五备选对比层、第六备选对比层。选取第一、第三、第五备选对比层作为对比检测层。即第一备选层为上述的第一对比检测层,第三备选层为上述的第二对比检测层,第五备选层为上述的第三对比检测层。

35.当在对待测3d堆叠封装集成电路芯片进行失效对应时,例如在同一检测频率下,检测到的相位值与第一对比检测层的相位值相同,则说明待测3d堆叠封装集成电路芯片发生失效的位置位于第一备选层;检测到的相位值位于第一对比检测层和第二对比检测的相位值之间,则说明待测3d堆叠封装集成电路芯片发生失效的位置位于第二备选层;检测到的相位值与第二对比检测的相位值相同,则说明待测3d堆叠封装集成电路芯片发生失效的位置位于第三备选层;测到的相位值位于第二对比检测层和第三对比检测的相位值之间,则说明待测3d堆叠封装集成电路芯片发生失效的位置位于第四备选层;依次类推,通过间隔选取备选对比层作为对比检测层的方式,可以对整个待测3d堆叠封装集成电路芯片进行失效定位。

36.s220、依次研磨出每层对比检测层,在暴露出的对比检测层的表面进行短路失效处理后,通过热成像仪从标准样品器件远离研磨侧的一侧,检测暴露出的对比检测层在不同检测频率下的相位值。

37.具体的,研磨值不同的对比检测层位置,在对比检测层的表面进行失效处理,形成失效模拟热点。例如,可以使用银胶制造短路点,使对比检测层处于失效状态。然后通过热成像仪从标准样品器件远离研磨侧的一侧,检测暴露出的对比检测层在不同检测频率下的相位值。

38.s230、根据每一对比检测层在失效状态下检测频率与相位值的对应关系确定该对比检测层的失效定位曲线。

39.s240、通过热成像仪检测待测3d堆叠封装集成电路芯片在不同检测频率下的相位值;其中,对待测3d堆叠封装集成电路芯片的检测频率范围位于对标准样品器件的检测频率范围内。

40.s250、根据待测3d堆叠封装集成电路芯片的检测频率与相位值的对应关系确定待测失效位置曲线。

41.具体的,待测失效位置曲线为待测3d堆叠封装集成电路芯片的相位值随检测频率变化的曲线。例如同样使用频率1hz、2hz、4hz和6hz进行收集相位值,从而确定待测失效位置曲线。确定待测失效位置曲线的方式可参考步骤s130,这里不再赘述。通过使用不同检测频率下的相位值确定待测失效位置曲线,可以实现每一频率下的相位值与失效定位曲线的对比,从而可以进一步的提高失效定位的准确性。

42.s260、根据每一对比检测层的失效定位曲线与待测失效位置曲线之间的相对距离,确定待测3d堆叠封装集成电路芯片失效膜层的位置。

43.具体的,若待测失效位置曲线与其中一条失效定位曲线几乎重合,则可以认为待测3d堆叠封装集成电路芯片发生失效的位置位于该失效定位曲线所对应的膜层的位置。若待测失效位置曲线位于与两条条失效定位曲线之间,则可以确定待测3d堆叠封装集成电路芯片发生失效的位置位于该两条失效定位曲线所对应的膜层的之间。

44.并且,当待测失效位置曲线位于与两条失效定位曲线之间时,若待测失效位置曲线与其中一条失效定位曲线之间的距离,大于与另一条失效定位曲线之间的距离,则可以确定待测3d堆叠封装集成电路芯片发生失效的位置与距离较近的失效定位曲线对应的膜层较近。

45.图3是本发明实施例提供的另一种3d堆叠封装集成电路芯片的失效定位方法的流程图,参考图3,3d堆叠封装集成电路芯片的失效定位方法包括:s310、根据标准样品器件所具有的功能膜层确定多个位于不同深度的对比检测层。

46.具体的,根据标准样品器件具有的功能膜层确定多个位于不同深度的对比检测层可以包括:将标准样品器件具有的功能膜层确定为备选对比层;间隔选取所述备选对比层作为对比检测层。

47.图4是本发明实施例提供的一种3d堆叠封装集成电路芯片的结构剖面图,参考图4,标准样品器件的功能膜层包括:依次层叠设置的焊接球层100、pcb基板200、第一连接触点层300、转接单元400、第二连接触点层500和顶层芯片600。其中,焊接球层100可以包括多个焊接球a(示例性的画出一个),第一连接触点层300可以包括多个第一连接触点b(示例性的画出一个),第二连接触点层500包括可以多个第二连接触点c(示例性的画出两个)。间隔选取备选对比膜层作为所述对比检测层包括:选取位于pcb基板200远离转接单元400一侧

的焊接球层100、pcb基板200与转接单元400之间的第一连接触点层300,以及转接单元400与顶层芯片600之间的第二连接触点层500为对比检测层10。

48.其中,其中焊接球层100作为第一对比检测层11,第一连接触点层300作为第二对比检测层12,第二连接触点层500作为第三对比检测层13。第一对比检测层11在标准样品器件的深度大于第二对比检测层12在标准样品器件中的深度,第二对比检测层12在标准样品器件的深度大于第三对比检测层13在标准样品器件中的深度。

49.s320、依次研磨出每层对比检测层,在暴露出的对比检测层的表面进行短路失效处理后,通过热成像仪从标准样品器件远离研磨侧的一侧,检测暴露出的对比检测层在不同检测频率下的相位值。

50.具体的,研磨至不同的对比检测层10位置,在对比检测层10的表面进行失效处理,形成失效模拟热点。例如,可以使用银胶制造短路点,使对比检测层10处于失效状态。然后通过热成像仪从标准样品器件远离研磨侧的一侧(图4中第三对比检测层13远离第二对比检测层12的一侧),检测暴露出的对比检测层在不同检测频率下的相位值。

51.选取焊接球层100、第一连接触点层300以及转第二连接触点层500为对比检测层10的方式,满足间隔选取备选对比层作为对比检测层10的同时,由于焊接球层100包括多个焊接球a,第一连接触点层300以及第二连接触点层500均包括多个金属接触点,可以使用银胶直接连接焊接球层100中的两个焊接球a即可形成短路点,使用银胶直接连接第一连接触点层300中的两个第一连接触点b即可形成短路点,使用银胶直接连接第二连接触点层中的两个第二连接触点c即可形成短路点,从而简化了对对比检测层10进行失效处理的方式。

52.s330、根据每一对比检测层在失效状态下检测频率与相位值的对应关系确定该对比检测层的失效定位曲线。

53.s340、通过热成像仪检测待测3d堆叠封装集成电路芯片在不同检测频率下的相位值;其中,对待测3d堆叠封装集成电路芯片的检测频率范围位于对标准样品器件的检测频率范围内。

54.s350、根据待测3d堆叠封装集成电路芯片的检测频率与相位值的对应关系确定待测失效位置曲线。

55.s360、根据每一对比检测层的失效定位曲线与待测失效位置曲线之间的相对距离,确定待测3d堆叠封装集成电路芯片失效膜层的位置。

56.具体的,图5是本发明实施例提供的一种不同深度对比检测层的相位值与检测频率关系图,参考图5,结合图4,曲线a为焊接球层100对应的失效定位曲线;曲线b为第一连接触点层300对应的失效定位曲线;曲线c为第二连接触点层500对应的失效定位曲线。若通过检测待测3d堆叠封装集成电路芯片后获取的待测失效位置曲线与其中一条失效定位曲线几乎重合,则可以认为待测3d堆叠封装集成电路芯片发生失效的位置位于该失效定位曲线所对应的膜层的位置。若待测失效位置曲线位于与两条条失效定位曲线之间,则可以确定待测3d堆叠封装集成电路芯片发生失效的位置位于该两条失效定位曲线所对应的膜层的之间。例如,待测失效位置曲线位于与曲线a与曲线b之间,则可以确定待测3d堆叠封装集成电路芯片发生失效的位置位于pcb基板200。

57.综上,本发明实施例提供的技术方案,在材料热传递性质的基础上,根据相位/频率关系曲线图可推知热点深度。可以定义封装的不同关键位置(例如:焊接球层100、pcb基

板200、第一连接触点层300、转接单元400、第二连接触点层500和顶层芯片600,其中顶层芯片600之上还可以包括多层的芯片),将好的样品进行制样,研磨之不同的位置,然后以失效模拟热点(例如使用银胶制造的短路点),应用不同频率测量相位(phase)值,就可以取得这个深度位置的相位/频率曲线。那么,在实际的失效分析过程中,只需先取好片进行数据库建立,在对失效样品也在不同频率下进行测试,选取数据收敛的测试结果,然后到已经建立的不同位置的相位/频率关系曲线图中,就可以确定出失效的位置,达到失效层和位置的准确定位。需要说明的是,对于不同的产品,需要分别建立不同相位/频率关系曲线图,供实际失效分析时使用。

58.本发明实施例还提供了一种3d堆叠封装集成电路芯片的失效定位装置,用于执行上述任意实施例所述的3d堆叠封装集成电路芯片的失效定位方法,包括:对比检测层确定单元,用于确定标准样品器件中多个位于不同深度的对比检测层;相位值检测单元,用于在依次研磨出每层所述对比检测层后,检测暴露出的所述对比检测层在失效状态下不同检测频率对应的相位值;失效定位曲线确定单元,用于根据每一对比检测层在失效状态下检测频率与相位值的对应关系确定该对比检测层的失效定位曲线;失效定位单元,用于根据每一对比检测层的失效定位曲线对待测3d堆叠封装集成电路芯片进行失效定位;其中所述标准样品器件为所述待测3d堆叠封装集成电路芯片同类型未失效的3d堆叠封装集成电路芯片。

59.参考图4,本发明实施例还提供了一种3d堆叠封装集成电路芯片,包括多层层叠设置的膜层,通过上述任意实施例所述的3d堆叠封装集成电路芯片的失效定位方法进行失效定位。具有相同的技术效果,这里不再赘述。

60.注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1