一种基于FPGA的声纳信号匹配滤波处理方法及其系统与流程

本发明涉及声纳信号处理,尤其涉及一种基于fpga的声纳信号匹配滤波处理方法及其系统。

背景技术:

1、在雷达、声纳等系统中,往往利用发射宽带信号,并借助专门的脉冲压缩处理算法来实现所需的距离维高分辨力。匹配滤波常见的脉冲压缩处理算法,在各种宽带系统中得到普遍的使用。它本质上属于fir数字滤波器的一种,但特殊之处在于其滤波器系数刚好为发射信号的共轭,这样对于一个刚好为发射信号拷贝的回波信号,经过匹配滤波器之后的输出恰好为一个窄脉冲,其脉冲宽度由发射信号的带宽决定,如此即实现了距离上的高分辨力(详见图1)。

2、由于匹配滤波处理是一种fir数字滤波器,因此在一个异构嵌入式系统中,非常适合于在fpga内实现,以减少对dsp或arm处理器的算力占用。

3、目前fpga内实现匹配滤波算法分为频域乘法实现和时域乘累加实现。频域乘法实现首先对输入信号进行fft操作,然后将其与系统冲击响应进行相乘,最后对乘积进行ifft操作得到输出。由于调用了fpga的fft核,计算速度快。但是由于需要缓存一段数据进行fft操作,因此输出结果不是实时的,而且分段缓存之间可能存在拼接不连续问题。

4、相对而言,时域乘累加实现基于fir架构(详见图2),即

5、

6、其中为当前时刻缓存的前n个采样点的输入信号,为匹配滤波器系数,为匹配滤波输出。

7、可以直接调用fpga的fir滤波器的ip核来实现,更多的做法是将输入数据和滤波器系数分别存储在一片ram内,在每个采样时刻,用n个乘法器分别实现每个输入采样信号与系数的相乘,最后通过一个加法器得到输出。这种实现方法结构简单,且能够每个采样点实时输出滤波结果。

8、然后,常规时域乘累加实现匹配滤波处理的架构存在的主要问题有以下几点:

9、1、对fpga乘法器资源要求较大,假设匹配滤波器阶数为n,则每个采样点都需要做n点乘累加运算。当n为1024甚至更大时,显然常规时域乘累加做实现要大量的乘法器来实现,这可能突破了fpga资源限制,或者说导致其它模块无法实现。在多通道数据处理系统如多波束声纳系统中,往往存在256甚至更多的并行通道需要同时完成匹配滤波,则需要的资源更多。

10、2、采用ram做数据缓存,当一个新的采样输入时,要将ram内所有数据全部更新一遍,存在大量数据搬移工作。

11、3、在发射脉宽变化范围比较大的系统中,为满足最大发射脉宽的需求,匹配滤波器的阶数会比较大,这样在发射短脉宽时,匹配滤波器系数绝大部分都为0,这会导致匹配滤波器输出值大幅降低,影响输出数据的动态范围。

12、由此可以看出,急需一种匹配滤波处理的fpga实现方法来解决上述问题。

技术实现思路

1、本发明提供一种基于fpga的声纳信号匹配滤波处理方法及其系统。

2、根据本发明的一个较佳实施例,本发明提供一种基于fpga的声纳信号匹配滤波处理方法,包括下列步骤:

3、(a)移入采样信号数据xi至数据缓存移位寄存器,其中i=1,2,……,n;

4、(b)数据缓存移位寄存器根据时序控制模块输出的数据选择信号d_select,在不同的clk_ctrl时钟沿依次输出采样信号数据xi到乘累加器;

5、(c)滤波器系数存储ram根据时序控制模块输出的读地址add_r,在不同的clk_ctrl时钟沿依次输出匹配滤波器系数ci到乘累加器,其中i=1,2,……,n;

6、(d)乘累加器根据时序控制模块输出的节拍控制信号,完成当前缓存器内采样信号数据xi和匹配滤波器系数ci的复数乘累加,得到累加输出结果;

7、(e)求模模块利用乘累加器的累加输出结果和匹配滤波器系数矩阵中非0值的个数k,计算得到匹配滤波器最终的匹配滤波输出。

8、作为优选的技术方案,在所述基于fpga的声纳信号匹配滤波处理方法中,进一步包括步骤(f)当系统调整发射波形参数时,通过spi接口将新的匹配滤波器系数ci下发至系数更新模块,系数更新模块将写使能信号en_w设置为高电平,并在n个控制时钟周期内,通过地址总线add_w和数据总线data_w,将匹配滤波器系数ci依次写入系数更新模块,同时将匹配滤波器系数矩阵中非0值的个数k传递给求模模块。

9、作为优选的技术方案,在步骤(a)中,所述数据缓存移位寄存器中输入数据相匹配的采样率由采样时钟决定,每个采样时钟输入一个数据,每个数据位宽为2d,每个数据中高d位为实部,低d位为虚部。

10、作为优选的技术方案,在步骤(b)中,所述数据缓存移位寄存器输出数据相匹配的采样率与输入数据相同,每个采样时钟输出一个结果,每个结果位宽为d。

11、作为优选的技术方案,在上述方法中,每个clk_data上升沿时刻,数据向右移动一个存储空间,并移入一个新的数据,数据移入移出为时钟驱动自动进行。

12、作为优选的技术方案,在步骤(c)中,每个匹配滤波器系数ci为2d比特,其中高d位为实部,低d位为虚部,匹配滤波器系数ci经一次加载后,无需随每个采样点进行移位。

13、作为优选的技术方案,在步骤(d)中,用一个dsp乘法器完成匹配滤波所需的所有乘法计算,时序控制模块根据内部计数值,在不同时刻输出不同选择信号,改变乘法器的两个输入,得到相应乘法输出,并对输出分组进行累加,具体做法步骤如下:

14、(1)利用d_select信号和add_r,依次选择xi和ci进行相乘;

15、(2)每个数据可表示为,每个滤波器系数可表示为,两者的相乘可表示为:

16、

17、,

18、利用时序控制模块输出的x_select信号和c_select信号,分别选择和的实部与虚部,并经过四次乘法,分别得到;

19、(3)利用时序控制模块输出的z_dispac信号,将z_dispac信号分别输出至相应的累加模块,由四个累加模块最终得到四个累加值,其中,

20、

21、;

22、(4)在下一个采样数据输入之前,完成当前缓存器内采样信号数据xi和匹配滤波器系数ci的复数乘累加,得到累加输出结果:

23、;

24、。

25、作为优选的技术方案,在步骤(e)中,求模模块利用乘累加模块的四个累加值,以及匹配滤波器系数矩阵中非0值的个数k,得到匹配滤波器最终的匹配滤波输出,步骤如下:

26、(1)分别得到实部与虚部累加结果:

27、

28、(2)根据k值,对与分别左移位,得到与;k表示n个滤波器系数中非0值个数;

29、(3)分别对与进行平方操作,得到;

30、(4)对求和并开方,得到匹配滤波器最终匹配滤波输出y;

31、。

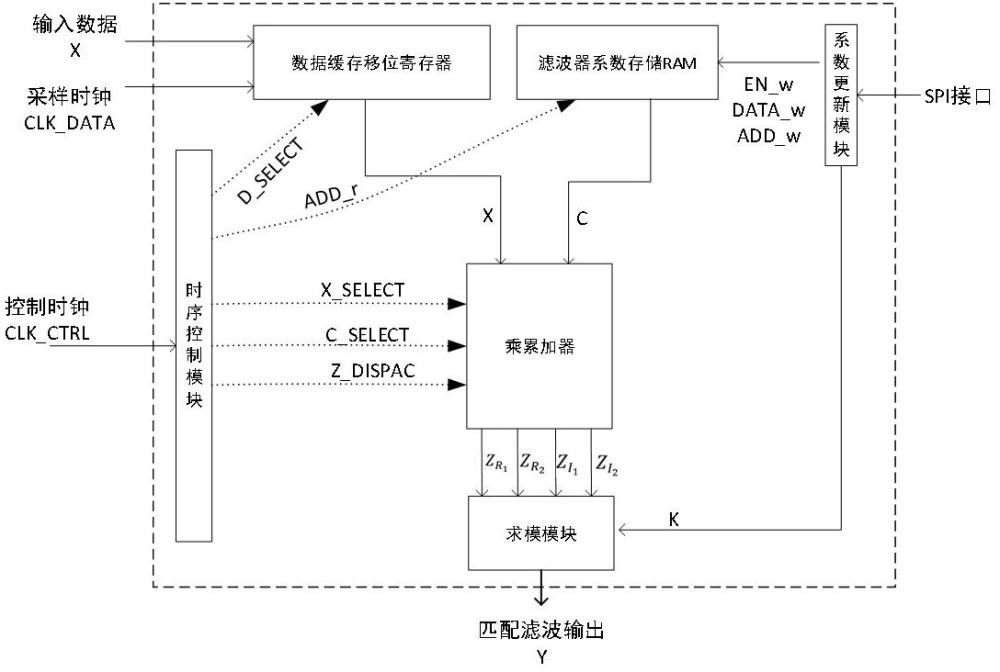

32、根据本发明的另一个较佳实施例,本发明提供一种基于fpga的声纳信号匹配滤波处理系统,其包括:

33、时序控制模块;

34、数据缓存移位寄存器,其中所述数据缓存移位寄存器和所述时序控制模块可通信地连接,所述数据缓存移位寄存器可接收采样信号数据xi,i=1,2,……,n;

35、滤波器系数存储ram,其中所述滤波器系数存储ram和所述时序控制模块可通信地连接;

36、乘累加器,其中所述乘累加器可通信地连接于数据缓存移位寄存器、所述滤波器系数存储ram以及所述时序控制模块,所述数据缓存移位寄存器根据时序控制模块输出的数据选择信号d_select,在不同的clk_ctrl时钟沿依次输出采样信号数据xi到所述乘累加器,滤波器系数存储ram根据时序控制模块输出的读地址add_r,在不同的clk_ctrl时钟沿依次输出匹配滤波器系数ci到乘累加器,其中i=1,2,……,n;乘累加器根据时序控制模块输出的节拍控制信号,完成当前缓存器内采样信号数据xi和匹配滤波器系数ci的复数乘累加,得到累加输出结果;

37、求模模块,其中所述求模模块可通信地连接于所述乘累加器,所述求模模块利用所述乘累加器的累加输出结果和匹配滤波器系数矩阵中非0值的个数k,得到匹配滤波器最终的匹配滤波输出。

38、作为优选的技术方案,所述基于fpga的声纳信号匹配滤波处理系统进一步包括系数更新模块和可通信地连接于所述系数更新模块的spi接口,所述spi接口包含时钟信号线、数据信号线与片选信号线,所述spi接口用于修改匹配滤波器系数矩阵,所述系数更新模块可通信地连接于所述求模模块。

39、作为优选的技术方案,所述乘累加器包括一个dsp乘法器和连接于所述dsp乘法器的多个累加模块,其中所述dsp乘法器和所述累加模块可通信地连接于所述时序控制模块。

40、作为优选的技术方案,数据缓存移位寄存器为n阶移位寄存器数组,每个寄存器为2d比特,其中高d位为输入信号实部,低d位为输入信号虚部。

41、作为优选的技术方案,时序控制模块的控制时钟为内部逻辑运行基准时钟,时序控制模块由一个主计数器驱动,并在计数器的不同计数值上,控制其它各模块进行相应的操作,计数器的驱动时钟为主控时钟clk_ctrl。

42、本发明的优点:

43、在fpga上实现了一种声纳信号匹配滤波处理方法。与现有方案需要消耗大量dsp乘法器资源,且无法保证发射脉宽变化时匹配滤波输出幅度稳定性相比,本发明通过合理设计时序,分时复用dsp乘法器资源,仅使用一个dsp乘法器即可完成整个匹配滤波处理,且能实现发射脉宽变化时匹配滤波输出幅度稳定。本发明还通过移位寄存器数组来自动实现采样数据的移入,避免采用bram的方式需要进行采样数据手动移入。

44、本发明利用时序控制模块实现单个dsp乘法器完成匹配滤波处理。

45、本发明通过对乘累加实部虚部自适应移位实现匹配滤波输出幅度稳定。

46、本发明利用寄存器数组实现采样数据的自动移入。

- 还没有人留言评论。精彩留言会获得点赞!