时间数字转换系统的制作方法

1.本发明涉及芯片设计领域,特别是涉及一种时间数字转换系统。

背景技术:

2.高精度(纳秒下,通常指100皮秒之1皮秒甚至亚皮秒)时间测量采用常规计量仪器如计数器无法实现,而时间数字转换(tdc)技术采用集成电路将时间间隔转换成二进制数字输出,可以获得很高精度。

3.目前tdc的一种实现方式是:利用可编程阵列(fpga)片内延时单元搭建多路延时链路对到达脉冲进行采样,对采样结果数据在fpga内或输出片外进行后处理,可以实现皮秒级的测量精度。

4.但由于fpga本征延时较大,单路延时链路难以达到10皮秒量级精度,要获得更高测量精度,就必须消耗更多硬件资源来搭建多路延时链路,导致功耗与成本迅速增加。

技术实现要素:

5.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种时间数字转换系统,用于解决现有采用fpga实现tdc时,因fpga的本征延时大导致难以达到10皮秒量级精度的问题。

6.为实现上述目的及其他相关目的,本发明提供一种时间数字转换系统,所述时间数字转换系统至少包括延时模块、量化模块及数据处理模块;

7.所述延时模块包括级联的粗延时锁相环和细延时锁相环,所述粗延时锁相环用于根据粗延时值对参考时钟进行多级延时并产生多相时钟,所述细延时锁相环用于根据细延时值对所述粗延时锁相环输出的任意相邻两相时钟分别进行延时并使总延时时间相同,以基于延时后两个时钟的相位差产生控制电压;

8.所述量化模块包括一路起始信号量化单元和至少一路终止信号量化单元,所述起始信号量化单元和所述终止信号量化单元的电路结构相同,均包括一级初量化电路、二级粗量化电路、同步电路和三级细量化电路;其中,

9.所述一级初量化电路连接所述粗延时锁相环的输出端,用于统计待测信号上升沿到达前第一相多相时钟上升沿的个数;

10.所述二级粗量化电路连接所述粗延时锁相环的输出端,用于测量待测信号上升沿到达前第一相多相时钟的最后一个上升沿与待测信号上升沿到达后多相时钟的第一个上升沿之间的时间差,并以此产生粗量化码;

11.所述同步电路连接所述粗延时锁相环的输出端和所述二级粗量化电路的输出端,用于提取待测信号的上升沿与其后的多相时钟的第一个上升沿之间的时间差,并作为提取信号送至所述三级细量化电路;

12.所述三级细量化电路连接所述细延时锁相环的输出端和所述同步电路的输出端,用于在所述控制电压的控制下,测量待测信号的上升沿与其后的多相时钟的第一个上升沿

之间的时间差,并以此产生细量化码;

13.所述数据处理模块连接各级量化电路的输出端,用于对各级量化电路的输出进行数据处理,以得到终止信号相对于起始信号的时间差。

14.可选地,所述粗延时锁相环至少包括输入缓冲级、压控粗延时单元、第一鉴频鉴相器、第一电荷泵及第一环路滤波器;

15.所述输入缓冲级用于对所述参考时钟进行缓冲后分两路输出;

16.所述压控粗延时单元连接所述输入缓冲级的一输出端,用于在延时调控电压的控制下,根据粗延时值对所述参考时钟进行多级延时并产生多相时钟;

17.所述第一鉴频鉴相器连接所述输入缓冲级的另一输出端和所述压控粗延时单元的最后一级输出,用于在粗延时使能信号有效时,比较参考时钟和反馈时钟的相位并产生二者的相位差;

18.所述第一电荷泵连接所述第一鉴频鉴相器的输出端,用于将所述相位差转换为所述延时调控电压;

19.所述第一环路滤波器连接所述第一电荷泵的输出端,用于滤除所述延时调控电压中的高频噪声。

20.可选地,所述粗延时锁相环还包括粗解除锁定单元,连接所述第一电荷泵的输出端,用于在所述粗延时使能信号无效时,将所述延时调控电压拉至工作电压。

21.可选地,所述粗延时锁相环还包括第一冗余匹配单元及第二冗余匹配单元;

22.所述第一冗余匹配单元连接于所述输入缓冲级的输出端和所述压控粗延时单元中第一级延时的输入端之间,用于对所述压控粗延时单元中第一级延时进行冗余匹配;

23.所述第二冗余匹配单元连接于所述第一冗余匹配单元的输出端和所述压控粗延时单元中最后一级延时的输出端之间,用于对所述压控粗延时单元中最后一级延时进行冗余匹配。

24.可选地,所述细延时锁相环至少包括:第一压控细延时单元、第二压控细延时单元、第二鉴频鉴相器、第二电荷泵及第二环路滤波器;

25.所述第一压控细延时单元连接所述粗延时锁相环输出的任一相多相时钟,用于经过大小为(粗延时值/细延时值+1)*cload的负载进行延时并产生第一延时时钟;

26.所述第二压控细延时单元连接所述粗延时锁相环输出的任一相多相时钟的下一相多相时钟,用于经过大小为1*cload的负载进行延时并产生第二延时时钟;

27.所述第二鉴频鉴相器连接所述第一压控细延时单元的输出端和所述第二压控细延时单元的输出端,用于在细延时使能信号有效时,比较所述第一延时时钟和所述第二延时时钟的相位并产生二者的相位差;

28.所述第二电荷泵连接所述第二鉴频鉴相器的输出端,用于将所述相位差转换为所述控制电压;

29.所述第二环路滤波器连接所述第二电荷泵的输出端,用于滤除所述控制电压中的高频噪声;

30.其中,cload为实现延时时间为细延时值的负载电容大小。

31.可选地,所述细延时锁相环还包括细解除锁定单元,连接所述第二电荷泵的输出端,用于在细延时使能信号无效时,将所述控制电压拉至工作电压。

32.可选地,所述一级初量化电路包括计数器及第一寄存器;

33.所述计数器连接所述粗延时锁相环的输出端,用于对所述第一相多相时钟的上升沿进行计数;

34.所述第一寄存器连接所述计数器的输出端,用于在所述待测信号的上升沿到达时,对所述计数器的计数进行锁存。

35.可选地,各所述一级初量化电路共用同一个计数器。

36.可选地,所述二级粗量化电路包括多个第一时间仲裁器;多个所述第一时间仲裁器的复位端均接入所述待测信号,多个所述第一时间仲裁器的置位端对应接入多相时钟,多个所述第一时间仲裁器的输出端作为所述二级粗量化电路的输出端。

37.可选地,所述起始信号量化单元和所述终止信号量化单元均还包括第二寄存器,所述第二寄存器连接各所述第一时间仲裁器的输出端,用于锁存所述粗量化码。

38.可选地,所述同步电路包括第一提取链路及第二提取链路;

39.所述第一提取链路至少包括多个第一pmos管和第一伪nmos逻辑或门;多个所述第一pmos管的栅端对应连接多个所述第一时间仲裁器的输出端,多个所述第一pmos管的漏端对应接入多相时钟,多个所述第一pmos管的源端连接所述第一伪nmos逻辑或门的输入端,所述第一伪nmos逻辑或门的输出端作为所述同步电路的一输出端;

40.所述第二提取链路至少包括第二时间仲裁器、第二pmos管及第二伪nmos逻辑或门;所述第二时间仲裁器的复位端接入所述待测信号,置位端接低电位,输出端连接所述第二pmos管的栅端;所述第二pmos管的漏端接入所述待测信号,源端连接所述第二伪nmos逻辑或门的输入端;所述第二伪nmos逻辑或门的输出端作为所述同步电路的另一输出端。

41.可选地,所述第一提取链路还包括多个第一提取缓冲器,多个所述第一提取缓冲器的输入端对应接入多相时钟,多个所述第一提取缓冲器的输出端对应连接多个所述第一pmos管的漏端;所述第二提取链路还包括第二提取缓冲器,所述第二提取缓冲器的输入端接入所述待测信号,输出端连接所述第二pmos管的漏端。

42.可选地,所述三级细量化电路包括列延时链路、行延时链路及时间仲裁器阵列;

43.所述列延时链路包括x个第一延时部,x个所述第一延时部的输入端均接入第一提取信号,x个所述第一延时部的输出端产生x个列输出信号;

44.所述行延时链路包括y个第二延时部,y个所述第二延时部的输入端均接入第二提取信号,y个所述第二延时部的输出端产生y个行输出信号;

45.所述时间仲裁器阵列包括x*y个第三时间仲裁器,所述第三时间仲裁器按x行y列排布,各所述第三时间仲裁器的复位端接入相应行所对应的列输出信号,各所述第三时间仲裁器的置位端接入相应列所对应的行输出信号,各所述第三时间仲裁器的输出端作为所述三级细量化电路的输出端;

46.其中,所述列延时链路中,后一个所述第一延时部相较于前一个所述第一延时部的延时时间增加1倍的细延时值,所述行延时链路中,后一个所述第二延时部相较于前一个所述第二延时部的延时时间增加x倍的细延时值,且x、y均为大于等于2的正整数。

47.可选地,所述第一延时部和所述第二延时部均是通过改变负载电容的连接个数来改变延时时间,且二者的电路结构相同。

48.可选地,所述起始信号量化单元和所述终止信号量化单元均还包括第三寄存器,

所述第三寄存器连接所述时间仲裁器阵列的输出端,用于锁存所述细量化码。

49.可选地,所述数据处理模块对所述二级粗量化电路和所述三级细量化电路的输出进行解码,之后基于各级量化电路的权重对各级量化电路的输出进行运算处理,得到起始信号相对于参考时钟的时间差及终止信号相对于参考时钟的时间差,并以此得到终止信号相对于起始信号的时间差。

50.如上所述,本发明的一种时间数字转换系统,通过延时模块、量化模块及数据处理模块的设计,打破了工艺限制,克服了cmos半导体固有的工艺偏差、电压波动和温度变化(pvt)所带来的影响,保证了输出数据的精确度,实现在各种工艺角、电压、温度条件下均能达到小于10ps的时间分辨率,实现高的时间分辨率和大的动态范围;而且,本发明的量化模块具有较强的鲁棒性,针对不同测量分辨率修改三级细量化电路中各延时部负载电容的个数不会显著影响测量精度。本发明能够实现多通道的时间数字转换,可以对随机到达脉冲进行高精度单击(single-shot)时间测量,在超声波流体仪表、医学正电子成像、高能粒子测量、量子信息技术等领域有着广泛应用。

附图说明

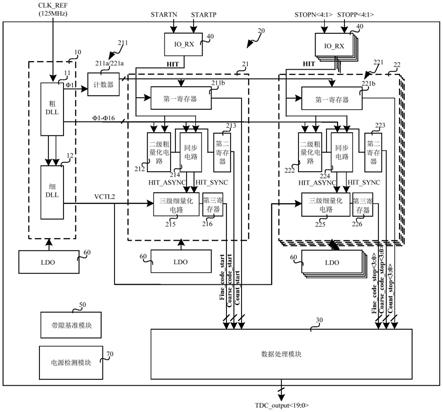

51.图1显示为本发明所述时间数字转换系统的电路框图。

52.图2显示为本发明所述粗延时锁相环的电路图。

53.图3显示为本发明所述细延时锁相环的电路图。

54.图4显示为本发明所述二级粗量化电路及所述同步电路的电路图。

55.图5显示为本发明涉及的时间仲裁器的电路图。

56.图6显示为本发明所述三级细量化电路的电路图。

57.图7显示为本发明所述三级细量化电路涉及的延时部的电路图。

58.图8显示为本发明所述二级粗量化电路的编码方式示意图。

59.图9显示为本发明所述三级细量化电路的编码方式示意图。

60.元件标号说明

61.10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

延时模块

62.11

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

粗延时锁相环

63.111

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输入缓冲级

64.112

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

压控粗延时单元

65.112a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

压控粗延时部

66.113

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一鉴频鉴相器

67.114

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一电荷泵

68.115

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一环路滤波器

69.116

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

粗解除锁定单元

70.117

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一冗余匹配单元

71.117a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一冗余粗延时部

72.117b

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二冗余粗延时部

73.118

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二冗余匹配单元

74.118a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三冗余粗延时部

75.118b

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第四冗余粗延时部

76.12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

细延时锁相环

77.121

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一压控细延时单元

78.122

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二压控细延时单元

79.123

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二鉴频鉴相器

80.124

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二电荷泵

81.125

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二环路滤波器

82.126

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

细解除锁定单元

83.20

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

量化模块

84.21

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

起始信号量化单元

85.22

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

终止信号量化单元

86.211、221

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

一级初量化电路

87.211a、221a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

计数器

88.211b、221b

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一寄存器

89.212、222

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

二级粗量化电路

90.213、223

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二寄存器

91.214、224

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

同步电路

92.214a、224a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一提取链路

93.214b、224b

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二提取链路

94.215、225

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

三级细量化电路

95.215a、225a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

列延时链路

96.215b、225b

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

行延时链路

97.215c、225c

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时间仲裁器阵列

98.216、226

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三寄存器

99.30

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

数据处理模块

100.40

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

高速输入模块

101.50

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

带隙基准模块

102.60

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

低压差线性稳压器模块

103.70

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电源检测模块

具体实施方式

104.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

105.请参阅图1至图9。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,虽图示中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的形态、数量及比例可为一种随意的改变,且其组件布局形态也可能更为复杂。

106.如图1所示,本实施例提供一种时间数字转换系统,所述时间数字转换系统至少包括:延时模块10、量化模块20及数据处理模块30。进一步的,所述时间数字转换系统还包括:高速输入模块40、带隙基准模块50、低压差线性稳压器模块(ldo)60及电源检测模块70。

107.所述延时模块10包括级联的粗延时锁相环11和细延时锁相环12,所述粗延时锁相环11用于根据粗延时值对参考时钟clk_ref进行多级延时并产生多相时钟,所述细延时锁相环12用于根据细延时值对所述粗延时锁相环11输出的任意相邻两相时钟分别进行延时并使总延时时间相同,以基于延时后两个时钟的相位差产生控制电压。

108.具体的,如图2所示,所述粗延时锁相环11至少包括:输入缓冲级111、压控粗延时单元112、第一鉴频鉴相器(pfd1)113、第一电荷泵(cp1)114及第一环路滤波器115。进一步的,所述粗延时锁相环11还包括粗解除锁定单元116。进一步的,所述粗延时锁相环11还包括:第一冗余匹配单元117及第二冗余匹配单元118。

109.所述输入缓冲级111用于对所述参考时钟clk_ref进行缓冲后分两路输出。

110.更具体的,所述输入缓冲级111包括第一输入缓冲器tin1及第二输入缓冲器tin2;所述第一输入缓冲器tin1和所述第二输入缓冲器tin2的输入端均接入所述参考时钟clk_ref,所述第一输入缓冲器tin1的输出端作为所述输入缓冲级111的一输出端,所述第二输入缓冲器tin2的输出端作为所述输入缓冲级111的另一输出端。

111.所述压控粗延时单元112连接所述输入缓冲级111的一输出端,用于在延时调控电压vctl1的控制下,根据粗延时值对所述参考时钟clk_ref进行多级延时并产生多相时钟,如参考时钟clk_ref的频率为125mhz,粗延时值为500ps(即每级延时时间为500ps),对参考时钟进行16级延时并产生16个多相时钟φ1-φ16。

112.更具体的,所述压控粗延时单元112采用压控延时线(vcdl)实现。其中,所述压控延时线包括多个压控粗延时部112a及多个粗缓冲器tc;多个所述压控粗延时部112a级联,第一个所述压控粗延时部112a的输入端连接所述输入缓冲级111的一输出端,最后一个所述压控粗延时部112a的输出端连接所述第一鉴频鉴相器113的另一输入端;多个所述粗缓冲器tc的输入端对应连接多个所述压控粗延时部112a的输出端,多个所述粗缓冲器的输出端对应产生多相时钟;其中,所述压控粗延时部112a的延时受控于所述延时调控电压vctl1。

113.所述第一鉴频鉴相器113连接所述输入缓冲级111的另一输出端和所述压控粗延时单元112的最后一级输出,用于在粗延时使能信号cdll_en有效时,比较参考时钟和反馈时钟的相位并产生二者的相位差。实际应用中,在所述粗延时使能信号cdll_en无效时(即从1变为0时),所述第一鉴频鉴相器113处于高阻状态;而在所述粗延时使能信号cdll_en有效时(即从0变为1时),所述第一鉴频鉴相器113开始工作。

114.所述第一电荷泵114连接所述第一鉴频鉴相器113的输出端,用于将所述参考时钟和所述反馈时钟的相位差转换为所述延时调控电压vctl1。

115.所述第一环路滤波器115连接所述第一电荷泵114的输出端,用于滤除所述延时调控电压vctl1中的高频噪声。

116.更具体的,所述第一环路滤波器115采用第一滤波电容c1实现,所述第一滤波电容c1连接于所述第一电荷泵114的输出端和地之间。

117.所述粗解除锁定单元116连接所述第一电荷泵114的输出端,用于在所述粗延时使

能信号cdll_en无效时,也即所述粗延时使能信号cdll_en的反相信号有效时,将所述延时调控电压vctl1拉至工作电压vdd,以保证所述压控粗延时单元112开始工作时,各所述压控粗延时部112a的延时最小,避免所述粗延时锁相环11出现错误锁定到125mhz的整数倍或者趋于向延时为0的方向锁定的可能。

118.更具体的,所述粗解除锁定单元116包括第一控制开关s1,所述第一控制开关s1的第一连接端接入工作电压vdd,第二连接端连接所述第一电荷泵114的输出端,控制端接入所述粗延时使能信号cdll_en的反相信号。所述第一控制开关s1在所述粗延时使能信号cdll_en的反相信号有效时导通,将所述延时调控电压vctl1拉至工作电压vdd。

119.所述第一冗余匹配单元117连接于所述输入缓冲级111的输出端和所述压控粗延时单元112中第一级延时(也即第一个压控粗延时部112a)的输入端之间,用于对所述压控粗延时单元112中第一级延时(也即第一个所述压控粗延时部112a)进行冗余匹配;而所述第二冗余匹配单元118连接于所述第一冗余匹配单元117的输出端和所述压控粗延时单元112中最后一级延时(也即最后一个压控粗延时部112a)的输出端之间,用于对所述压控粗延时单元112中最后一级延时(也即最后一个所述压控粗延时部112a)进行冗余匹配。

120.更具体的,所述第一冗余匹配单元117包括第一冗余粗延时部117a、第二冗余粗延时部117b、第一冗余粗缓冲器td1及第二冗余粗缓冲器td2;所述第一冗余粗延时部117a的输入端和所述第二冗余粗延时部117b的输入端对应连接所述输入缓冲级111的两个输出端,所述第一冗余粗延时部117a的输出端连接所述压控粗延时单元112中第一个所述压控粗延时部112a的输入端及所述第一冗余粗缓冲器td1的输入端,所述第一冗余粗缓冲器td1的输出端悬空,所述第二冗余粗延时部117b的输出端连接所述第二冗余匹配单元118的输入端及所述第二冗余粗缓冲器td2的输入端,所述第二冗余粗缓冲器td2的输出端悬空;其中,所述第一冗余粗延时部117a及所述第二冗余粗延时部117b的延时均受控于所述延时调控电压vctl1。

121.所述第二冗余匹配单元118包括第三冗余粗延时部118a、第四冗余粗延时部118b、第三冗余粗缓冲器td3及第四冗余粗缓冲器td4;所述第三冗余粗延时部118的输入端连接所述第二冗余粗延时部117b的输出端,所述第二冗余粗延时部117b的输出端连接所述第三冗余粗缓冲器td3的输入端,所述第三冗余粗缓冲器td3的输出端连接所述第一鉴频鉴相器113的一输入端;所述第四冗余粗延时部118b的输入端连接所述压控粗延时单元112中最后一个压控粗延时部112a的输出端,所述第四冗余粗延时部118b的输出端连接所述第四冗余粗缓冲器td4的输入端,所述第四冗余粗缓冲器td4的输出端连接所述第一鉴频鉴相器113的另一输入端;其中,所述第三冗余粗延时部118a及所述第四冗余粗延时部118b的延时均受控于所述延时调控电压vctl1。

122.本实施例中,所述输入缓冲级111、所述压控粗延时单元112、所述第一鉴频鉴相器113、所述第一电荷泵114及所述第一环路滤波器115形成一个环路,在该环路的作用下,通过不断调整所述延时调控电压vctl1,实现所述参考时钟与所述反馈时钟同相。

123.具体的,如图3所示,所述细延时锁相环12至少包括:第一压控细延时单元121、第二压控细延时单元122、第二鉴频鉴相器(pfd2)123、第二电荷泵(cp2)124及第二环路滤波器125。进一步的,所述细延时锁相环12还包括细解除锁定单元126。

124.所述第一压控细延时单元121连接所述粗延时锁相环11输出的任一相多相时,用

于经过大小为(粗延时值/细延时值+1)*cload的负载进行延时并产生第一延时时钟clkv;而所述第二压控细延时单元122连接所述粗延时锁相环11输出的任一相多相时钟的下一相多相时钟,用于经过大小为1*cload的负载进行延时并产生第二延时时钟clkr;其中,cload为实现延时时间为细延时值的负载电容大小。

125.所述第一压控细延时单元121和所述第二压控细延时单元122是通过改变各自延时单元中负载电容的大小来改变延时时间,从而使两个时钟的总延时时间相同;如粗延时值为500ps,细延时值为10ps,那么经过所述粗延时锁相环11后相邻两相时钟(和)的延时时间相差500ps,此时,第一压控细延时单元121中负载电容cload的个数为51个,以使前一个时钟(也即)延时510ps,第二压控细延时单元122中负载电容cload的个数为1个,以使后一个时钟(也即)延时10ps,从而使两个时钟的总延时时间相同。实际应用中,通常选用比较靠前的两个相邻多相时钟作为所述第一压控细延时单元121和所述第二压控细延时单元122的输入,以避免引入延时误差。

126.所述第二鉴频鉴相器123连接所述第一压控细延时单元121的输出端和所述第二压控细延时单元122的输出端,用于在细延时使能信号fdll_en有效时,比较所述第一延时时钟clkv和所述第二延时时钟clkr的相位并产生二者的相位差。实际应用中,在所述细延时使能信号fdll_en无效时(即从1变为0时),所述第二鉴频鉴相器123处于高阻状态;而在所述细延时使能信号fdll_en有效时(即从0变为1时),所述第二鉴频鉴相器123开始工作。

127.所述第二电荷泵124连接所述第二鉴频鉴相器123的输出端,用于将所述第一延时时钟clkv和所述第二延时时钟clkr的相位差转换为控制电压vctl2。

128.所述第二环路滤波器125连接所述第二电荷泵124的输出端,用于滤除所述控制电压vctl2中的高频噪声。

129.更具体的,所述第二环路滤波器125采用第二滤波电容c2实现,所述第二滤波电容c2连接于所述第二电荷泵124的输出端和地之间。

130.所述细解除锁定单元126连接所述第二电荷泵124的输出端,用于在细延时使能信号fdll_en无效时,也即细延时使能信号fdll_en的反相信号有效时,将所述控制电压vctl2拉至工作电压vdd,以保证所述第一压控细延时单元121和所述第二压控细延时单元122开始工作时,延时最小,避免所述细延时锁相环12出现错误锁定。

131.更具体的,所述细解除锁定单元126包括第二控制开关s2,所述第二控制开关s2的第一连接端接入工作电压vdd,第二连接端连接所述第二电荷泵124的输出端,控制端接入所述细延时使能信号fdll_en的反相信号。所述第二控制开关s2在所述细延时使能信号fdll_en的反相信号有效时导通,将所述控制电压vctl2拉至工作电压vdd。

132.本实施例中,所述第一压控细延时单元121、所述第二压控细延时单元122、所述第二鉴频鉴相器123、所述第二电荷泵124及所述第二环路滤波器125形成一个环路,在该环路的作用下,通过不断调整所述控制电压vctl2,实现所述第一延时时钟clkv和所述第二延时时钟clkr同相,从而得到所需要的分辨率(如10ps)和动态范围。

133.所述量化模块20包括一路起始信号量化单元21和至少一路终止信号量化单元22,所述起始信号量化单元21和所述终止信号量化单元22的电路结构相同,均包括一级初量化电路211/221、二级粗量化电路212/222、同步电路213/223和三级细量化电路214/224。实际应用中,可根据具体需求来设定所述终止信号量化单元22的数量,如设定所述终止信号量

化单元22的数量为4路,本实施例对此不做限制。

134.所述一级初量化电路211/221连接所述粗延时锁相环11的输出端,用于统计待测信号上升沿到达前第一相多相时钟上升沿的个数。需要注意的是,对于所述起始信号量化单元21而言,待测信号为输入至系统的起始信号;对于所述终止信号量化单元22而言,待测信号为输入至系统的终止信号。

135.具体的,所述一级初量化电路211/221包括计数器211a/221a及第一寄存器211b/221b;所述计数器211a/221a连接所述粗延时锁相环11的输出端,用于对所述第一相多相时钟的上升沿进行计数;所述第一寄存器211b/221b连接所述计数器211a/221a的输出端,用于在所述待测信号的上升沿到达时,对所述计数器211a/221a的计数进行锁存。可选地,各所述一级初量化电路211/221共用同一个计数器,以便于节省芯片面积。

136.更具体的,所述计数器211a/221a为同步计数器,其位数可根据参考时钟clk_ref的频率来设定;如参考时钟clk_ref的频率为125mhz时,可选用11位同步计数器,其时间分辨率为8ns,动态范围为16.384μs。

137.所述二级粗量化电路212/222连接所述粗延时锁相环11的输出端,用于测量待测信号上升沿到达前第一相多相时钟的最后一个上升沿与待测信号上升沿到达后多相时钟的第一个上升沿之间的时间差,并以此产生粗量化码。本实施例中,由于多相时钟相邻两相的延时差为500ps,也即所述二级粗量化电路212/222的分辨率为500ps,其动态范围为产生多相时钟的压控延时线的总延时,即为500ps*16=8ns。

138.具体的,如图4所示,所述二级粗量化电路212/222包括多个第一时间仲裁器arbiter1;多个所述第一时间仲裁器arbiter1的复位端均接入所述待测信号,多个所述第一时间仲裁器arbiter1的置位端对应接入多相时钟,多个所述第一时间仲裁器arbiter1的输出端作为所述二级粗量化电路212/222的输出端。

139.进一步的,所述起始信号量化单元21和所述终止信号量化单元22均还包括第二寄存器213/223,所述第二寄存器213/223连接各所述第一时间仲裁器arbiter1的输出端,用于锁存所述粗量化码。

140.所述同步电路214/224连接所述粗延时锁相环11的输出端和所述二级粗量化电路212的输出端,用于提取待测信号的上升沿与其后的多相时钟的第一个上升沿之间的时间差,并作为提取信号送至所述三级细量化电路215/225。

141.具体的,如图4所示,所述同步电路214/224包括第一提取链路214a/224a及第二提取链路214b/224b;所述第一提取链路214a/224a至少包括多个第一pmos管pm1和第一伪nmos逻辑或门,多个所述第一pmos管pm1的栅端对应连接多个所述第一时间仲裁器arbiter1的输出端,多个所述第一pmos管pm1的漏端对应接入多相时钟,多个所述第一pmos管pm1的源端连接所述第一伪nmos逻辑或门的输入端,所述第一伪nmos逻辑或门的输出端作为所述同步电路214/224的一输出端;所述第二提取链路214b/224b至少包括第二时间仲裁器arbiter2、第二pmos管pm2及第二伪nmos逻辑或门,所述第二时间仲裁器arbiter2的复位端接入所述待测信号,所述第二时间仲裁器arbiter2的置位端接低电位vss,所述第二时间仲裁器arbiter2的输出端连接所述第二pmos管pm2的栅端,所述第二pmos管pm2的漏端接入所述待测信号,所述第二pmos管pm2的源端连接所述第二伪nmos逻辑或门的输入端,所述第二伪nmos逻辑或门的输出端作为所述同步电路214/224的另一输出端。

142.所述第一提取链路214a/224a利用所述第一时间仲裁器arbiter1的结果,控制所述第一pmos管pm1的开、关,当待测信号上升沿到达时,所述第一时间仲裁器arbiter1输出为低电平,相应的所述第一pmos管pm1会打开,将对应的多相时钟输出,所述第一伪nmos逻辑或门将所有支路的结果进行逻辑或运算,最后得到的时钟上升沿即为第一个到达的多相时钟的上升沿,记为hit_sync信号;为了保证待测信号与hit_sync信号之间较小的误差,在待测信号后引入相同的逻辑单元,采用所述第二pmos管pm2和所述第二伪nmos逻辑或门得到待测信号,记为hit_async信号;以此实现待测信号与其后的多相时钟的第一个上升沿的提取,也即待测信号的上升沿与其后的多相时钟的第一个上升沿之间的时间差的提取。

143.进一步的,为了增加驱动同时保证开关逻辑的正确性,可在开关之前加入缓冲器,保证脉冲信号到达开关之前,开关已经导通。因此,所述第一提取链路214a/224a还包括多个第一提取缓冲器t1,多个所述第一提取缓冲器t1的输入端对应接入多相时钟,多个所述第一提取缓冲器t1的输出端对应连接多个所述第一pmos管pm1的漏端;所述第二提取链路214b/224b还包括第二提取缓冲器t2,所述第二提取缓冲器t2的输入端接入所述待测信号,输出端连接所述第二pmos管pm2的漏端。

144.更具体的,如图5所示,所述第一时间仲裁器arbiter1和所述第二时间仲裁器arbiter2的电路结构相同,均包括第一反相器inv1、第二反相器inv2、第三反相器inv3、第四反相器inv4、第一或非门nor1及第二或非门nor2;所述第一反相器inv1的输入端作为时间仲裁器的复位端,输出端连接所述第一或非门nor1的一输入端;所述第一或非门nor1的另一输入端连接第二或非门nor2的输出端,输出端连接所述第二反相器inv2的输入端;所述第二反相器inv2的输出端作为时间仲裁器的同相输出端;所述第三反相器inv3的输入端作为时间仲裁器的置位端,输出端连接所述第二或非门nor2的一输入端;所述第二或非门nor2的另一输入端连接第一或非门nor1的输出端,输出端连接所述第四反相器inv4的输入端;所述第四反相器inv4的输出端作为时间仲裁器的反相输出端。其中,所述时间仲裁器对应的真值表如下表1。需要注意的是,本实施例所述第一时间仲裁器arbiter1的输出端和所述第二时间仲裁器arbiter2的输出端均是指对应时间仲裁器的同相输出端。

145.表1

146.rsqn+1qbn+100xx0110100111qnqbn

147.更具体的,所述第一伪nmos逻辑或门包括:多个第一nmos管nm1、多个第二nmos管nm2、一个第三nmos管nm3、一个第三pmos管pm3及一个第四pmos管pm4;多个所述第一nmos管nm1的栅端接入工作电压vdd,多个所述第一nmos管nm1的漏端对应连接多个所述第二nmos管nm2的栅端,多个所述第一nmos管nm1的源端接地,多个所述第二nmos管nm2的栅端对应连接多个所述第一pmos管pm1的源端,多个所述第二nmos管nm2的漏端连接所述第三pmos管pm3的漏端,多个所述第二nmos管nm2的源端接地,所述第三pmos管pm3的栅端接低电位vss,所述第三pmos管pm3的漏端连接所述第四pmos管pm4的栅端及所述第三nmos管nm3的栅端,所述第三pmos管pm3的源端连接所述第四pmos管pm4的源端并接入供电电压vcc,所述第四

pmos管pm4的漏端连接所述第三nmos管nm3的漏端并作为所述第一伪nmos逻辑或门的输出端,所述第三nmos管nm3的源端接地;

148.所述第二伪nmos逻辑或门包括:一个第四nmos管nm4、多个第五nmos管nm5、一个第六nmos管nm6、一个第五pmos管pm5及一个第六pmos管pm6;所述第四nmos管nm4的栅端接入工作电压vdd,所述第四nmos管nm4的漏端连接第一个所述第五nmos管nm5的栅端,所述第四nmos管nm4的源端接地,第一个所述第五nmos管nm5的栅端连接所述第二pmos管pm2的源端,其他所述第五nmos管nm5的栅端均接地,多个所述第五nmos管nm5的漏端连接所述第五pmos管pm5的漏端,多个所述第五nmos管nm5的源端接地,所述第五pmos管pm5的栅端接低电位vss,所述第五pmos管pm5的漏端连接所述第六pmos管pm6的栅端及所述第六nmos管nm6的栅端,所述第五pmos管pm5的源端连接所述第六pmos管pm6的源端并接入供电电压vcc,所述第六pmos管pm6的漏端连接所述第六nmos管nm6的漏端并作为所述第二伪nmos逻辑或门的输出端,所述第六nmos管nm6的源端接地。

149.所述三级细量化电路215/225连接所述细延时锁相环12的输出端和所述同步电路214/224的输出端,用于在所述控制电压vctl2的控制下,测量待测信号的上升沿与其后的多相时钟的第一个上升沿之间的时间差,并以此产生细量化码。

150.具体的,如图6所示,所述三级细量化电路215/225包括列延时链路215a/225a、行延时链路215b/225b及时间仲裁器阵列215c/225c。

151.所述列延时链路215a/225a包括x个第一延时部,x个所述第一延时部的输入端均连接所述同步电路214/224的一输出端以接入第一提取信号hit_sync,x个所述第一延时部的输出端产生x个列输出信号;而所述行延时链路215b/225b包括y个第二延时部,y个所述第二延时部的输入端均连接所述同步电路214/224的另一输出端以接入第二提取信号hit_async,y个所述第二延时部的输出端产生y个行输出信号;其中,所述列延时链路215a/225a中,后一个所述第一延时部相较于前一个所述第一延时部的延时时间增加1倍的细延时值,所述行延时链路215b/225b中,后一个所述第二延时部相较于前一个所述第二延时部的延时时间增加x倍的细延时值,且x、y均为大于等于2的正整数。实际应用中,x和y的取值可根据具体需求来设定,其中y的取值决定了所述三级细量化电路215/225的动态范围,而x的取值则决定了所述行延时链路215b/225b中相邻两第二延时部之间的延时差,如x为9,y为6。

152.进一步的,为了消除第二提取信号hit_async与第一提取信号hit_sync之间由于非理想因素引起的延时差,在所述行延时链路215b/225b的首尾各增加一个第二延时部,此时,所述行延时链路215b/225b中第二延时部的数量为(y+2)个,如8个,以此避免tdc在量化过程中产生死区;通过在所述行延时链路215b/225b的首尾各增加一个第二延时部,使所述三级细量化电路215/225向两个方向共扩展了22位,即输出位数为72位,当第二提取信号hit_async与第一提取信号hit_sync的延时差为0时,所述三级细量化电路215/225输出9,为固定的延时差,后续终止信号与起始信号通道相减时可以抵消。更进一步的,为了实现版图对称,使x和y的值相同,如x为9,y也为9,也即在所述行延时链路215b/225b的最后再增加一个第二延时部,但该最后一个第二延时部的输出不接入所述时间仲裁器阵列中。

153.本实施例中,各延时部的延时均为10ps,也即所述三级细量化电路215/225的分辨率为10ps,考虑在第二提取信号hit_async与第一提取信号hit_sync之间由于非理想因素引起的延时差,同时实现版图对称,设x为9,y为9,但最后一个第二延时部的输出不接入时

间仲裁器阵列215c/225c中,此时,所述三级细量化电路215/225的动态范围为720ps(也即-90ps~630ps)。

154.更具体的,如图7所示,所述第一延时部和所述第二延时部的电路结构相同,二者均是通过改变负载电容的连接个数来改变延时时间,使最小延时可小于工艺的本征延时。电路结构包括:第五反相器inv5、第六反相器inv6、第七反相器in7、第八反相器inv8、第九反相器inv9、第十反相器inv10、第十一反相器inv11、第十二反相器inv12、第十三反相器nv13、第七pmos管pm7、第八pmos管pm8、第九pmos管pm9、第七nmos管nm7、第八nmos管nm8、第九nmos管nm9、第十nmos管nm10、第十一nmos管nm11、第十二nmos管nm12、第十三nmos管nm13及输出缓冲器tout;所述第五反相器inv5的输入端作为延时部的输入端,输出端通过级联的所述第六反相器inv6和所述第七反相器inv7连接所述第七pmos管pm7的栅端和所述第七nmos管nm7的栅端,同时通过所述第八反相器inv8连接第八pmos管pm8的栅端和所述第八nmos管nm8的栅端;所述第七pmos管pm7的源端接入供电电压vcc,漏端连接所述第七nmos管nm7的漏端及第一负载电容接入端;所述第七nmos管nm7的源端连接所述第九nmos管nm9的漏端及所述第十nmos管nm10的漏端;所述第九nmos管的nm9的栅端接入所述控制电压vctl2,源端连接所述第十nmos管nm10的源端并接地,所述第十nmos管nm10的栅端接入工作电压vdd;所述第八pmos管pm8的源端接入供电电压vcc,漏端连接所述第八nmos管nm8的漏端及第二负载电容接入端;所述第八nmos管nm8的源端连接所述第十一nmos管nm11的漏端及所述第十二nmos管nm12的漏端;所述第十一nmos管的栅端接入所述控制电压vctl2,源端连接所述第十二nmos管nm12的源端并接地,所述第十二nmos管的栅端接入工作电压vdd;所述第一负载电容接入端通过级联的所述第九反相器inv9及所述第十反相器inv10连接所述第九pmos管pm9的栅端,所述第二负载电容接入端通过级联的所述第十一反相器inv11、所述第十二反相器inv12及所述第十三反相器inv13连接所述第十三nmos管nm13的栅端;所述第九pmos管pm9的源端接入供电电压vcc,漏端连接所述第十三nmos管nm13的漏端及所述输出缓冲器的输入端,所述第十三nmos管nm13的源端接地,所述输出缓冲器的输出端作为所述延时器的输出端;其中,所述第一负载电容接入点和所述第二负载电容接入点均并联有n个第一电容c1和m个第二电容c2,其中m=65-n,n的取值介于1-63之间,包括端点值。

155.所述时间仲裁器阵列215c/225c包括x*y个第三时间仲裁器,所述第三时间仲裁器按x行y列排布,各所述第三时间仲裁器的复位端接入相应行所对应的列输出信号,各所述第三时间仲裁器的置位端接入相应列所对应的行输出信号,各所述第三时间仲裁器的输出端作为所述三级细量化电路的输出端。进一步的,在所述行延时链路215b/225b的首尾各增加一个第二延时部时,所述时间仲裁器阵列215c/225c中增加两列第三时间仲裁器。更进一步的,为了实现版图对称,在所述行延时链路215b/225b的最后继续增设第二延时部时,所述时间仲裁器阵列215c/225c中增加相应列数的第三时间仲裁器,只是对应列的所述第三时间仲裁器的置位端悬空。需要注意的是,所述第三时间仲裁器与所述第一时间仲裁器和所述第二时间仲裁器的结构相同,具体结构可参见前文,此处不再赘述;而且,所述第三时间仲裁器的输出端也是指时间仲裁器的同相输出端。

156.进一步的,所述起始信号量化单元21和所述终止信号量化单元22均还包括第三寄存器216/226,所述第三寄存器216/226连接所述时间仲裁器阵列215c/225c的输出端,用于锁存所述细量化码。

157.本实施例中,所述量化模块采用三级内插结构,其中第一级采用计数器实现初量化,第二级采用延时链实现粗量化,第三级采用小于门延时的并行尺度可调延时单元(parallel scaled delay elements)实现细量化,第三级量化的时间分辨率即为整个系统的时间分辨率;而且,为了抑制内部延时受pvt偏差的影响,粗量化所需的多相时钟和细量化所需的控制电压分别由粗延时锁相环和细延时锁相环提供;以此实现在各种工艺角、电压、温度(pvt)条件下,均能达到小于10ps的时间分辨率,实现高的时间分辨率(如10ps)和大的动态范围(如10μs)。

158.所述数据处理模块30连接各级量化电路的输出端,用于对各级量化电路的输出进行数据处理,以得到终止信号相对于起始信号的时间差。可选地,所述数据处理模块30采用处理器实现。

159.具体的,所述数据处理模块30对所述二级粗量化电路212/222和所述三级细量化电路214/224的输出进行解码,之后基于各级量化电路的权重对各级量化电路的输出进行运算处理,得到起始信号相对于参考时钟的时间差及终止信号相对于参考时钟的时间差,并以此得到终止信号相对于起始信号的时间差。

160.所述数据处理模块30在对所述二级粗量化电路212/222的输出进行解码时,主要是检测粗量化码中下降沿的位置,即从低位到高位由1变为0的位置;如待测信号的上升沿晚于第三相多相时钟的上升沿,但早于第四相多相时钟的上升沿,此时,所述二级粗量化电路212/222输出的粗量化码从高位到低位为8b’10000111,解码后粗量化码为3b’011(如图8所示)。

161.所述数据处理模块30在对所述三级细量化电路214/224的输出进行解码时,主要是采用整体相加的形式完成解码;r《0:8》、s《0:7》分别是hit_sync信号、hit_async信号经延时阵列产生的,t1、t2分别为10ps、90ps,将r《0:8》的上升沿分别与s《0:7》的上升沿进行比较得到细量化码,如r《0》与s《0:7》上升沿比较输出结果为8b’10000000,r《1》/r《2》/r《3》/r《4》/r《5》/r《6》/r《7》与s《0:7》上升沿比较的结果和r《0》一样,r《8》与s《0:7》上升沿比较输出结果为8b’11000000,将输出结果中的1的个数相加得到细量化码的解码结果为10,二进制表示为7b’0001010(如图9所示)。

162.完成解码后,基于公式(一级初量化电路211的输出*一级初量化电路211的权重+二级粗量化电路212的输出解码*二级粗量化电路212的权重-三级细量化电路214的输出解码*三级细量化电路214的权重)得到起始信号相对于参考时钟的时间差,基于公式(一级初量化电路221的输出*一级初量化电路221的权重+二级粗量化电路222的输出解码*二级粗量化电路222的权重-三级细量化电路224的输出解码*三级细量化电路224的权重)得到终止信号相对于参考时钟的时间差,最后二者相减,得到终止信号相对于起始信号的时间差。本实施例中,一级初量化电路211/221的权重为8ns/10ps,二级粗量化电路212/222的权重为500ps/10ps,三级细量化电路214/224的权重为10ps/10ps。

163.所述高速输入模块40与所述量化模块20中的各量化单元一一对应设置,用于接收外部输入的起始信号和终止信号并产生对应的待测信号。本实施例中,所述高速输入模块40为差分转单端结构。

164.所述带隙基准模块50用于提供参考电压。

165.所述低压差线性稳压器模块(ldo)60与所述延时模块10及所述量化模块20中的各

量化单元一一对应设置,且均连接所述带隙基准模块50的输出端,用于根据所述参考电压产生特定电压值的电源,并对应提供至所述延时模块10及所述量化模块20中的各量化单元。

166.所述电源检测模块70用于检测所述延时模块10及所述量化模块20中的各量化单元是否正常上电。

167.综上所述,本发明的一种时间数字转换系统,通过延时模块、量化模块及数据处理模块的设计,打破了工艺限制,克服了cmos半导体固有的工艺偏差、电压波动和温度变化(pvt)所带来的影响,保证了输出数据的精确度,实现在各种工艺角、电压、温度条件下均能达到小于10ps的时间分辨率,实现高的时间分辨率和大的动态范围;而且,本发明的量化模块具有较强的鲁棒性,针对不同测量分辨率修改三级细量化电路中各延时部负载电容的个数不会显著影响测量精度。本发明能够实现多通道的时间数字转换,可以对随机到达脉冲进行高精度单击(single-shot)时间测量,在超声波流体仪表、医学正电子成像、高能粒子测量、量子信息技术等领域有着广泛应用。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

168.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1