电荷泵架构的制作方法

1.本公开涉及电荷泵架构。

背景技术:

2.电荷泵电路是使用电容器作为蓄能元件以起到升压转换器作用的装置。

3.最流行的电荷泵电路之一是基于倍压器的,并且它也被称为佩里科尼(pelliconi)电荷泵并且通常包括多个nmos和pmos晶体管,多个nmos和pmos晶体管彼此交叉联接并连接至升压电容器,适当地组织成彼此级联的级,以提供阶梯式升压效果。

4.作为现有技术,图1a示意性示出了佩里科尼电荷泵。更具体地,所描绘的电荷泵100是2级电荷泵电路;然而,可以插入任意数量的级,以制作n级电荷泵电路。

5.电荷泵100包括第一级110和第二级120,第一级110连接至接收输入电压vin的输入端子in以及第二级120,第二级120进而连接至提供输出电压vout的输出端子out,第一级110和第二级120与处于内部电压v1的内部节点int相对应地互连。

6.第一级110包括第一nmos晶体管mn1a和第一pmos晶体管mp1a,第一nmos晶体管mn1a和第一pmos晶体管mp1a彼此串联地插入在输入端子in和内部节点int之间,并在第一电路节点x1a处彼此互连,进而连接至由时钟信号ck驱动的第一升压电容器c1a。此外,第一级110包括第二nmos晶体管mn1b和第二pmos晶体管mp1b,该第二nmos晶体管mn1b和第二pmos晶体管mp1b彼此串联地插入在输入端子in和内部节点int之间并且在第二电路节点x1b处彼此互连,进而连接至由相对于时钟信号ck具有反相值的反相时钟信号ckb驱动的第二升压电容器c1b。

7.此外,第一级110的晶体管是交叉联接的。具体而言,第一nmos晶体管mn1a和第一pmos晶体管mp1a使各自的控制端子或栅极端子连接至第二电路节点x1b,并且第二nmos晶体管mn1b和第二pmos晶体管mp1b使各自的控制端子或栅极端子连接至第一电路节点x1a。

8.类似地,第二级120包括第一nmos晶体管mn2a和第一pmos晶体管mp2a,第一nmos晶体管mn2a和第一pmos晶体管mp2a彼此串联地插入在内部节点int和输出端子out之间,并且在第一电路节点x2a处彼此互连,进而连接至由反相时钟信号ckb驱动的第一升压电容器c2a。此外,第二级120包括第二nmos晶体管mn2b和第二pmos晶体管mp2b,第二nmos晶体管mn2b和第二pmos晶体管mp2b彼此串联地插入在内部节点int和输出端子out之间并在第二电路节点x2b处彼此互连,进而连接至由时钟信号ck驱动的第二升压电容器c2b。

9.另外,第二级120的晶体管是交叉联接的。具体而言,第一nmos晶体管mn2a和第一pmos晶体管mp2a使各自的控制端子或栅极端子连接至第二电路节点x2b,并且第二nmos晶体管mn2b和第二pmos晶体管mp2b使各自的控制端子或栅极端子连接至第一电路节点x2a。

10.在图1b中示出了电荷泵100的用于第一级110的电压和时钟信号,并且在图1c中示出了电荷泵100的用于第二级120的电压和时钟信号。具体而言,显然,第一级110在其输入端子in处接收值等于vcc的输入电压vin,并且在内部节点int处提供等于2vcc的内部电压v1,在第一电路节点x1a和第二电路节点x1b处分别提供电压vboost1和vboost1b,电压

vboost1和vboost1b彼此相反并且当时钟信号ck和ckb范围在0和vcc之间时电压vboost1和vboost1b范围在vcc和2vcc之间,如图1b所示。

11.类似地,第二级120接收值等于2vcc的内部电压v1,并且在输出端子out处提供等于3vcc的输出电压vout,在第一电路节点x2a和第二电路节点x2b处分别提供电压vboost2b和vboost2,电压vboost2b和vboost2彼此相反并且当时钟信号ck和ckb范围在0和vcc之间时电压vboost2b和vboost2范围在2vcc和3vcc之间,如图1c所示。

12.作为现有技术,佩里科尼电荷泵已广泛应用于包括闪存装置在内的许多应用中。

13.使用这种电荷泵拓扑的缺点之一与两级的升压电容器之间的电阻有关,例如,如图1a所示的第一级110的第一升压电容器c1a和第二级120的第一升压电容器c2a之间的电阻、或者第一级110的第二升压电容器c1b和第二级120的第二升压电容器c2b之间的电阻。由于一个nmos晶体管和一个pmos晶体管连接两级的第一升压电容器c1a和c2a或第二升压电容器c1b和c2b,因此两个升压电容器之间的总电阻是nmos晶体管的导通电阻和pmos晶体管的导通电阻之和。为了减少电荷泵级中的传导损耗,应该使该寄生电阻最小化。

14.此外,第二个缺点与pmos本身的使用有关。事实上,众所周知,在pmos晶体管中,空穴迁移率低于nmos晶体管中的电子迁移率。这种效应迫使电荷泵设计者相对于nmos晶体管使用更大宽度的pmos晶体管,以补偿降低的空穴迁移率。通常,依据空穴与电子迁移率的比率,应该使用2到3范围内的宽度因子的增加。在电荷泵级中使用过大的晶体管具有分别在第一级110和第二级120的电路节点x1a、x1b、x2a、x2b上的寄生电容增加的负面影响,从而降低电荷泵效率。

15.已经提出cts电荷泵,作为在电荷泵的两级之间使用仅一个晶体管的方法,如在x.jiang,x.yu,k.moez,d.g.elliott,and j.chen,“high-efficiency charge pumps for low-power on-chip applications,”ieee trans.circuits syst.i,reg.papers,vol.65,no.3,pp.1143

–

1153,mar.2018(“用于低功率片上应用的高效电荷泵”ieee trans.circuits syst.i,reg.papers,第65卷第3号,第1143

–

1153页,2018年3月)中所描述的。例如,在图2a中,呈现了交叉联接的2级pmos cts电荷泵。

16.电荷泵200包括第一级210和第二级220,第一级210连接至接收第一电压或输入电压vin的输入端子in,并且第二级220进而连接至提供输出电压vout的输出端子out,第一级210和第二级220与第三电路节点x2a和第四电路节点x2b相对应地互连。

17.第一级210包括第一nmos晶体管mn1a和第一pmos晶体管mp1a,第一nmos晶体管mn1a和第一pmos晶体管mp1a彼此串联地插入在输入端子in和第三电路节点x2a之间,并且在第一电路节点x1a处彼此互连,进而连接至由时钟信号ck驱动的第一升压电容器c1a。此外,第一级210包括第二nmos晶体管mn1b和第二pmos晶体管mp1b,该第二nmos晶体管mn1b和第二pmos晶体管mp1b彼此串联地插入在输入端子in和第四电路节点x2b之间并且在第二电路节点x1b处彼此互连,进而连接至由相对于时钟信号ck具有反相值的反相时钟信号ckb驱动的第二升压电容器c1b。

18.此外,第一级210的nmos晶体管交叉联接。具体而言,第一nmos晶体管mn1a的控制栅极连接至第二电路节点x1b,而第二nmos晶体管mn1b的控制栅极连接至第一电路节点x1a。

19.第二级或输出级220包括交叉联接的第三pmos晶体管mp2a和第四pmos晶体管

mp2b,第三pmos晶体管mp2a和第四pmos晶体管mp2b分别插入在第三电路节点x2a和输出端子out之间以及第四电路节点x2b和输出端子out之间。

20.具体而言,第三pmos晶体管mp2a的控制栅极连接至第四电路节点x2b,进而连接至由时钟信号ck驱动的第四升压电容器c2b,而第四pmos晶体管mp2b的控制栅极连接至第三电路节点x2a,进而连接至由相对于时钟信号ck具有反相值的反相时钟信号ckb驱动的第三升压电容器c2a。

21.此外,第一级210的pmos晶体管mp1a和mp1b的栅极端子由作为典型cts架构的布置中的附加nmos和pmos晶体管来控制。具体而言,第一附加nmos晶体管mnaux1a连接在第二电路节点x1b和第一pmos晶体管mp1a的控制栅极之间,并且使控制栅极连接至第一内部电路节点y1a,进而连接至第一升压电容器c1a并且连接至第二nmos晶体管mn1b的控制栅极,而且第一附加pmos晶体管mpaux1a连接在第一pmos晶体管mp1a的控制栅极和第三电路节点x2a之间并且使控制栅极连接至第四电路节点x2b。类似地,第二附加nmos晶体管mnaux1b连接在第一电路节点x1a和第二pmos晶体管mp1b的控制栅极之间,并且使控制栅极连接至第二内部电路节点y1b,进而连接至第二升压电容器c1b并且连接至第一nmos晶体管mn1a的控制栅极,而且第二附加pmos晶体管mpaux1b连接在第二pmos晶体管mp1b的控制栅极和第四电路节点x2b之间并且使栅极端子连接至第三电路节点x2a。

22.在图2b中示出了cts电荷泵200的用于第一级210的电压和时钟信号,并且在图2c中示出了cts电荷泵200的用于第二级220的电压和时钟信号。具体而言,显然,第一级210在其输入端子in处接收值等于vcc的输入电压vin并且在第一电路节点x1a和第二电路节点x1b处分别提供电压vboost1和vboostb1,电压vboost1和vboostb1彼此相反并且当时钟信号ck和ckb范围在0和vcc之间时电压vboost1和vboostb1范围在vcc和2vcc之间,如图2b所示。

23.电压vboost1b借助于其控制栅极被偏置在电压电平vg2的第二pmos晶体管mp1b被传递至第四电路节点x2b,电压电平vg2范围在vcc和3vcc之间,而电压vboost1借助于其控制栅极被偏置在电压电平vg1的第一pmos晶体管mp1a传递至第三电路节点x2a,该电压电平vg1范围也在vcc和3vcc之间并且与电压vg2相反。

24.输出级220接收升压电压vboost1和vboost1b并产生升压电压vboost2和vboost2b,升压电压vboost2和vboost2b进而分别借助于第四pmos晶体管mp2b和第三pmos晶体管mp2a传递至输出端子out。

25.升压电压vboost2和vboost2b彼此相反,当时钟信号ck和ckb范围在0到vcc之间时升压电压vboost2和vboost2b范围在2vcc到3vcc之间,如图2c所示。

26.如图2a所示的cts电荷泵由相对于nmos晶体管具有降低的载流子迁移率的pmos晶体管制成。

27.已经提出了其它cts架构。在韩国专利申请公开no.kr 10-1983386中描述了其中使用pmos和nmos晶体管二者的cts电荷泵。具体而言,所公开的cts电路架构具有pmos和nmos晶体管的修改的连接配置,以防止由传统cts电荷泵(如图2a所示的cts电荷泵)中出现的阈值电压增加所引起的效率降低。在韩国专利申请公开no.kr 2013-0074050中也公开了使用泵并包括具有交叉联接配置的辅助电路的电源电路。

技术实现要素:

28.本发明的各个实施方式针对一种新的电荷泵架构,其包括彼此级联的多个级,其中,在每一级中,仅使用nmos开关晶体管来连接相邻级的升压电容器。附加的nmos和pmos晶体管用于偏置nmos开关晶体管的控制栅极。此外,在施加到每一级的时钟信号之间提供延迟。

29.所提出的电荷泵架构的目的在于降低电荷泵整体的功耗,从而提高其性能。这可以在这种新架构的实施方式中获得,因为两个nmos晶体管的串连接相邻级的两个升压电容器,以避免如佩里科尼电荷泵那样的一个nmos晶体管和一个pmos晶体管的串连接相邻级的两个升压电容器。此外,根据该新架构的另一实施方式,仅使用一个nmos晶体管连接相邻级的两个升压电容器以替代cts电荷泵中使用的pmos晶体管,使用nmos晶体管代替pmos晶体管是优选的,这是因为载流子迁移率在nmos晶体管中比在pmos晶体管中高。

30.此外,籍由所使用的时钟信号从一级到另一级的延迟,所提出的电荷泵架构能够有效地减少反向电荷传导效应。

31.在本发明的实施方式中,一种电荷泵架构包括:输入端子和输出端子;第一级,该第一级在其输入端子处接收第一电压并且在其输出端子处输出第二电压,该第一级包括连接至第一对内部升压节点的第一对电容器;第二级,该第二级在其输入端子处接收所述第二电压并且在其输出端子处输出第三电压,该第二级包括连接至第二对内部升压节点的第二对电容器;以及辅助级,该辅助级在其输入端子处接收所述第三电压,该辅助级包括连接至第三对内部升压节点的第三对电容器,其中,所述电荷泵架构的所述输入端子对应于所述第一级的所述输入端子,并且所述电荷泵架构的所述输出端子对应于所述第二级的所述输出端子和所述辅助级的所述输入端子,其中,所述第一级和所述第二级中的每一个包括:该级的所述输入端子和所述输出端子;第一类型的mos晶体管,所述第一类型的mos晶体管将来自所述输入端子的电压传送至所述一对内部升压节点并且交叉联接;第二类型的mos晶体管,所述第二类型的mos晶体管具有由第三类型的mos晶体管和第四类型的mos晶体管偏置的栅极;第三类型的mos晶体管,所述第三类型的mos晶体管将所述第二类型的mos晶体管的所述栅极连接至该级的所述一对内部升压节点;以及第四类型的mos晶体管,所述第四类型的mos晶体管将所述第二类型的mos晶体管的所述栅极连接至下一级的一对内部升压节点。

32.根据本发明的另一实施方式,一种电荷泵架构包括:输入端子和输出端子;第一级,该第一级在其输入端子处接收第一电压并且在其第一输出端子和第二输出端子处分别输出第一升压电压和第二升压电压,该第一级包括连接至所述第一输出端子和所述第二输出端子的第一对电容器;第一中间级,该第一中间级分别在其第一输入端子和第二输入端子处从所述第一级接收所述第一升压电压和所述第二升压电压,并且分别在其第一输出端子和第二输出端子处输出第三升压电压和第四升压电压,该第一中间级包括连接至其第一输出端子和第二输出端子的第二对电容器;第二中间级或最后中间级,该第二中间级或最后中间级分别在其第一输入端子和第二输入端子处从所述第一中间级接收所述第三升压电压和所述第四升压电压,并且分别在其第一输出端子和第二输出端子处输出第五升压电压和第六升压电压,该第二中间级包括连接至其第一输出端子和第二输出端子的第三对电容器;以及最后级,该最后级分别在其第一输入端子和第二输入端子处从所述第二中间级

接收所述第五升压电压和所述第六升压电压,并且在输出端子处输出输出电压,其中,所述电荷泵架构的所述输入端子对应于所述第一级的所述输入端子,并且所述电荷泵架构的所述输出端子对应于所述最后级的所述输出端子,其中,所述第一级包括:所述输入端子以及所述第一输出端子和所述第二输出端子;以及第一类型的mos晶体管,所述第一类型的mos晶体管将来自所述输入端子的电压传送至所述第一输出端子和所述第二输出端子并且交叉联接,并且其中,所述第一中间级和所述第二中间级中的每一个包括:所述第一输入端子和所述第二输入端子以及所述第一输出端子和所述第二输出端子;第二类型的mos晶体管,所述第二类型的mos晶体管将来自该级的所述第一输入端子和所述第二输入端子的升压电压传送至该级的所述第一输出端子和所述第二输出端子;第三类型的mos晶体管,所述第三类型的mos晶体管将该级的所述第二类型的mos晶体管的栅极连接至该级的所述第一输入端子和所述第二输入端子;以及第四类型的mos晶体管,所述第四类型的mos晶体管将该级的所述第二类型的mos晶体管的所述栅极连接至该级的所述第一输出端子和所述第二输出端子,并且其中,所述最后级包括:所述第一输入端子和所述第二输入端子以及所述输出端子;第五类型的mos晶体管,所述第五类型的mos晶体管将来自该级的所述第一输入端子和所述第二输入端子的所述第五升压电压和所述第六升压电压传送至该级的所述输出端子并且交叉联接。

33.根据本发明的另一实施方式,一种电荷泵架构包括:输入端子和输出端子;至少第一级,所述至少第一级在其也是电荷泵的输入端子的输入端子处接收第一电压,并且在其输出端子处输出第二电压;至少第二级,所述至少第二级在其输入端子处接收来自第一级的第二电压作为输入电压并在其输出端子处输出第三电压,该输出端子也是电荷泵的输出端子;以及辅助级,该辅助组在其输入端子接收最后一级(即,第二级)的输出电压作为输入并控制最后一级的内部节点电压,其中第一级和第二级包括:第一晶体管,该第一晶体管将输入电压传送至该级的内部升压节点,第一晶体管为第一类型的nmos晶体管;第二晶体管,该第二晶体管将该级的内部升压电压传送至输出电压,第二晶体管为第二类型的nmos晶体管;第三晶体管和第四晶体管,该第三晶体管和该第四晶体管控制第二晶体管的栅极,第三晶体管和第四晶体管分别为第三类型的nmos晶体管和第四类型的pmos晶体管。

34.根据本发明的实施方式,电荷泵架构可以使用彼此移位延迟时段的、连接至每一级的时钟信号和反相时钟信号,该延迟时段插入在驱动一个级的时钟信号和反相时钟信号中,以相对于前一级的时钟信号和反相时钟信号提前移位时钟信号。

附图说明

35.本公开的特征和优点将从以下参照附图以指示性而非限制性示例的方式给出的实施方式的描述中变得明显,在附图中,

36.图1a示出了根据传统技术的佩里科尼电荷泵。

37.图1b和图1c示出了图1a的佩里科尼电荷泵的内部信号。

38.图2a示出了根据传统技术的交叉联接的cts电荷泵。

39.图2b和图2c示出了图2a的交叉联接的cts电荷泵的内部信号。

40.图3示出了根据本发明的实施方式的电荷泵架构。

41.图4示出了根据本发明的实施方式的图3的电荷泵架构的内部信号。

42.图5a和图5b示出了根据本发明的实施方式的在不同工作阶段中图3的电荷泵架构的导通晶体管。

43.图6示出了根据本发明的替代实施方式的电荷泵架构。

44.图7示出了根据本发明的实施方式的图6的电荷泵架构的内部信号。

45.图8a和图8b示出了根据本发明的实施方式的在不同工作阶段中图6的电荷泵架构的导通晶体管。

46.图9示出了根据本发明的实施方式的电荷泵架构的时钟信号。

具体实施方式

47.下面将参照附图详细描述本发明的各个实施方式。尽管结合其实施方式示出并描述了本发明,但是对于本领域技术人员而言显而易见的是,可以在不脱离本发明的精神和范围的情况下进行各种修改。另外,可以省略本领域公知的构造的详细描述以避免不必要地掩盖本发明的清楚性。

48.在附图中,相应的特征由相同的附图标记标识。

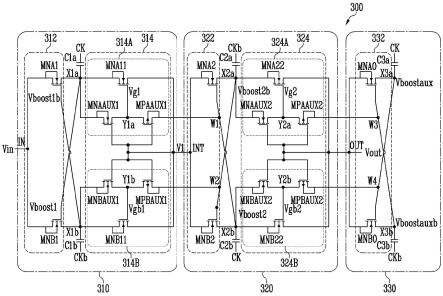

49.图3示意性地示出了根据本发明的实施方式的电荷泵架构300。

50.电荷泵架构300包括:第一级310,该第一级310连接至电荷泵的输入端子in并接收作为第一电压的输入电压vin;以及第二级320,该第二级320连接至电荷泵的输出端子out并提供输出电压vout,该第一级310和第二级320彼此串联并且在处于作为第二电压的内部电压v1的内部节点int处互连。第一级310包括分别由时钟信号ck和反相时钟信号ckb驱动的第一对电容器c1a、c1b,而第二级320包括分别由反相时钟信号ckb和时钟信号ck驱动的第二对电容器c2a、c2b。电荷泵架构300还包括辅助级330,该辅助级330进而包括分别由时钟信号ck和反相时钟信号ckb驱动的第三对电容器c3a、c3b。

51.更具体地,第一级310包括连接在输入端子in和第一对电容器c1a、c1b之间的第一开关块312,该第一开关块312包括:第一nmos晶体管mna1,其插入在输入端子in和第一电路节点x1a之间,进而连接至第一对的第一电容器c1a;以及第二nmos晶体管mnb1,其插入在输入端子in和第二电路节点x1b之间,进而连接至第一对的第二电容器c1b。此外,第一nmos晶体管mna1的控制端子或栅极端子连接至第二电路节点x1b,并且第二nmos晶体管mnb1的控制端子或栅极端子连接至第一电路节点x1a。第一nmos晶体管mna1在也连接至第二nmos晶体管mnb1的栅极端子的第一电路节点x1a处为第一对的第一电容器c1a提供第一升压电压vboost1,其进而在也连接至第一nmos晶体管mna1的栅极端子的第二电路节点x1b处为第一对的第二电容器c1b提供第二反相升压电压vboost1b。在实施方式中,第一nmos晶体管mna1和第二nmos晶体管mnb1在图3的实施方式中可以是具有连接至其源极端子的体端子的三阱nmos晶体管。然而,可以使用现有技术中已知的其它方案来根据充电泵相位改变体端子连接,以在升压或电荷泵输出下降期间避免体至漏极正向偏置。

52.因此,第一级310的第一电路节点x1a和第二电路节点x1b分别为第一级310的第一内部升压节点和第二内部升压节点。

53.第一级310还包括连接在第一电路节点x1a和第二电路节点x1b与内部节点int之间的第二开关块314,该第二开关块314包括插入在第一电路节点x1a和内部节点int之间的第一开关晶体管结构314a、以及插入在第二电路节点x1b和内部节点int之间的第二开关晶

体管结构314b,这样的第一开关晶体管结构314a和第二开关晶体管结构314b在处于内部电压v1的内部节点int处彼此互连。

54.更具体地,第一开关晶体管结构314a包括:第一开关nmos晶体管mna11,其插入在第一电路节点x1a和内部节点int之间并且具有连接至第一内部电路节点y1a的控制端子或栅极端子;第一附加开关nmos晶体管mnaaux1,其插入在第一电路节点x1a和第一内部电路节点y1a之间,并具有连接至内部节点int和第二开关晶体管结构314b的控制端子或栅极端子;以及第二附加开关pmos晶体管mpaaux1,其插入在第一内部电路节点y1a和第一互连节点w1之间并且具有连接至内部节点int和第二开关晶体管结构314b的控制端子或栅极端子。在图3的实施方式中,第一开关晶体管结构314a的第一开关nmos晶体管mna11和第一附加开关nmos晶体管mnaaux1可以是具有连接至其源极端子的体端子的三阱nmos晶体管。然而,可以使用现有技术中已知的其它方案来根据充电泵相位改变体端子连接,以在升压或电荷泵输出下降期间避免体至漏极正向偏置。另一方面,第二附加开关晶体管mpaaux1是具有连接至其源极的体的pmos晶体管。另外,对于该pmos晶体管,可以实施更复杂的方案来管理体连接,以在升压或电荷泵输出下降期间避免漏极至体正向偏置。

55.以对称的方式,第二开关晶体管结构314b包括:第一开关nmos晶体管mnb11,其插入在第二电路节点x1b和内部节点int之间并且具有连接至第二内部电路节点y1b的控制端子或栅极端子;第一附加开关nmos晶体管mnbaux1,其插入在第二电路节点x1b和第二内部电路节点y1b之间并具有连接至内部节点int和第一开关晶体管结构314a的控制端子或栅极端子;以及第二附加开关pmos晶体管mpbaux1,其插入在第二内部电路节点y1b和第二互连节点w2之间并且具有连接至内部节点int和第一开关晶体管结构314a的控制端子或栅极端子。在图3的实施方式中,第二开关晶体管结构314b的第一开关nmos晶体管mnb11和第一附加开关nmos晶体管mnbaux1可以是具有连接至其源极端子的体端子的三阱nmos晶体管。然而,可以使用现有技术中已知的其它方案来根据充电泵相位改变体端子连接,以在升压或电荷泵输出下降期间避免体至漏极正向偏置。另一方面,第二附加开关晶体管mpbaux1是具有连接至其源极的体的pmos晶体管。另外,对于该pmos晶体管,可以实现更复杂的方案来管理体连接,以在升压或电荷泵输出下降期间避免漏极至体正向偏置。第一内部电路节点y1a处于第一控制电压vg1,而第二内部电路节点y1b处于反相的第一控制电压vgb1。

56.第二级320具有与第一级310相同的结构。

57.更具体地,第二级320包括连接在内部节点int和第二对电容器c2a、c2b之间的第一开关块322,该第一开关块322包括:第一nmos晶体管mna2,其插入在内部节点int和第一电路节点x2a之间,进而连接至第二对的第一电容器c2a;以及第二nmos晶体管mnb2,其插入在内部节点int和第二电路节点x2b之间,进而连接至第二对的第二电容器c2b。此外,第一nmos晶体管mna2具有连接至第二电路节点x2b的控制端子或栅极端子,并且第二nmos晶体管mnb2具有连接至第一电路节点x2a的控制端子或栅极端子。第一nmos晶体管mna2在第一电路节点x2a处为第二对的第一电容器c2a提供第三反相升压电压vboost2b,而第二nmos晶体管mnb2在第二电路节点x2b处为第二对的第二电容器c2b提供第四升压电压vboost2。在图3的实施方式中,第一nmos晶体管mna2和第二nmos晶体管mnb2可以是具有连接至其源极端子的体端子的三阱nmos晶体管。然而,可以使用现有技术中已知的其它方案来根据充电泵相位改变体端子连接,以在升压或电荷泵输出下降期间避免体至漏极正向偏置。

58.因此,第二级320的第一电路节点x2a和第二电路节点x2b分别是第二级320的第一内部升压节点和第二内部升压节点。

59.第二级320还包括连接在第一电路节点x2a和第二电路节点x2b与输出端子out之间的第二开关块324,该第二开关块324包括插入在第一电路节点x2a和输出端子out之间的第一开关晶体管结构324a以及插入在第二电路节点x2b和输出端子out之间的第二开关晶体管结构324b,这样的第一开关晶体管结构324a和第二开关晶体管结构324b在输出端子out处彼此互连。

60.更具体地,第一开关晶体管结构324a包括:第一开关nmos晶体管mna22,其插入在第一电路节点x2a和输出端子out之间并且具有连接至第一内部电路节点y2a的控制端子或栅极端子;第一附加开关nmos晶体管mnaaux2,其插入在第一电路节点x2a和第一内部电路节点y2a之间,并具有连接至输出端子out和第二开关晶体管结构324b的控制端子或栅极端子;以及第二附加开关pmos晶体管mpaaux2,其插入在第一内部电路节点y2a和第三互连节点w3之间并且具有连接至输出端子out和第二开关晶体管结构324b的控制端子或栅极端子。在图3的实施方式中,第一开关晶体管结构324a的第一开关nmos晶体管mna22和第一附加开关nmos晶体管mnaaux2可以是具有连接至其源极端子的体端子的三阱nmos晶体管,然而,可以使用现有技术中已知的其它方案来根据充电泵相位改变体端子连接,以在升压或电荷泵输出下降期间避免体至漏极正向偏置。另一方面,第二附加开关晶体管mpaaux2是具有连接至其源极的体的pmos晶体管。另外,对于该pmos晶体管,可以实现更复杂的方案来管理体连接,以在升压或电荷泵输出下降期间避免漏极至体正向偏置。

61.第一内部电路节点y2a处于第二控制电压vg2,并且第二内部电路节点y2b处于反相的第二控制电压vgb2。

62.以对称方式,第二开关晶体管结构324b包括:第一开关nmos晶体管mnb22,其插入在第二电路节点x2b和输出端子out之间,并且具有连接至第二内部电路节点y2b的控制端子或栅极端子;第一附加开关nmos晶体管mnbaux2,其插入在第二电路节点x2b和第二内部电路节点y2b之间,并且具有连接至输出端子out和第一开关晶体管结构324a的控制端子或栅极端子;以及第二附加开关pmos晶体管mpbaux2,其插入在第二内部电路节点y2b和第四互连节点w4之间,并且具有连接至输出端子out和第一开关晶体管结构324a的控制端子或栅极端子。在图3的实施方式中,第二开关晶体管结构324b的第一开关nmos晶体管mnb22和第一附加开关nmos晶体管mnbaux2可以是具有连接至其源极端子的体端子的三阱nmos晶体管。然而,可以使用现有技术中已知的其它方案来根据充电泵相位改变体端子连接,以在升压或电荷泵输出下降期间避免体至漏极正向偏置。另一方面,第二附加开关晶体管mpbaux2是具有连接至其源极的体的pmos晶体管。另外,对于该pmos晶体管,可以实现更复杂的方案来管理体连接,以在升压或电荷泵输出下降期间避免漏极至体正向偏置。

63.第一级310和第二级320也在第一互连节点w1和第二互连节点w2处彼此连接。更具体地,第一互连节点w1连接至第一级310的第二开关块314的第一开关晶体管结构314a以及第二级320的第二电路节点x2b,并且第二互连节点w2连接至第一级310的第二开关块314的第二开关晶体管结构314b以及第二级320的第一电路节点x2a。

64.辅助级330包括插入在输出端子out和第三对电容器c3a、c3b之间的辅助开关块332。更具体地,辅助开关块332包括:第一nmos晶体管mnao,其插入在输出端子out和第一电

路节点x3a之间,进而连接至第三对的第一电容器c3a;以及第二nmos晶体管mnbo,其插入在输出端子out和第二电路节点x3b之间,进而连接至第三对的第二电容器c3b。此外,第一nmos晶体管mnao具有连接至第二电路节点x3b的控制端子或栅极端子,并且第二nmos晶体管mnbo具有连接至第一电路节点x3a的控制端子或栅极端子。在图3的实施方式中,辅助开关块332的第一nmos晶体管mnao和第二nmos晶体管mnbo是具有连接至其源极端子的体端子的三阱nmos晶体管,然而,可以使用现有技术中已知的其它方案来根据充电泵相位改变体端子连接,以在升压或电荷泵输出下降期间避免体至漏极正向偏置。第一nmos晶体管mnao在第一电路节点x3a处为第三对的第一电容器c3a提供第五升压电压vboostaux,而第二nmos晶体管mnbo在第二电路节点x3b处为第三对的第二电容器c3b提供第六反相升压电压vboostauxb。

65.因此,辅助级330的第一电路节点x3a和第二电路节点x3b分别为辅助级330的第一内部升压节点和第二内部升压节点。

66.第二级320和辅助级330也在第三互连节点w3和第四互连节点w4处彼此连接。更具体地,第三互连节点w3连接至第二级320的第二开关块324的第一开关晶体管结构324a以及辅助级330的第二电路节点x3b,而第四互连节点w4连接至第二级320的第二开关块324的第二开关晶体管结构324b和辅助级330的第一电路节点x3a。

67.因此,电荷泵架构300包括:第一级310,其在输入端子in处接收第一电压vin并输出第二电压v1;第二级320,其接收第二电压v1并在输出端子out处输出输出电压vout;以及辅助级330,其连接至输出端子out,其中,第一级310包括分别连接至第一级310的第一内部升压节点x1a和第二内部升压节点x1b的第一对电容器c1a、c1b,第二级320包括分别连接至第二级320的第一内部升压节点x2a和第二内部升压节点x2b的第二对电容器c2a、c2b,并且辅助级330包括分别连接至辅助级330的第一内部升压节点x3a和第二内部升压节点x3b的第三对电容器c3a、c3b。

68.此外,第一级310包括连接至第一对电容器c1a、c1b的各个开关块,并且各个开关块包括:第一类型的mos晶体管(具体地,nmos晶体管mna1、mnb1),其将输入电压vin分别传送到该级的第一内部升压节点x1a和第二内部升压节点x1b并且交叉联接;第二类型的mos晶体管(具体地,nmos晶体管mna11、mnb11),其将该级的第一内部升压节点x1a和第二内部升压节点x1b处的电压传送至内部节点int,并具有通过第三类型的mos晶体管mnaaux1、mnbaux1和第四类型的mos晶体管mpaaux1、mpbaux1而偏置的栅极;第三类型的mos晶体管(具体地,nmos晶体管mnaaux1、mnbaux1),其将第二类型的mos晶体管mna11、mnb11的栅极连接至该级的第一内部升压节点x1a和第二内部升压节点x1b;以及第四类型的mos晶体管(具体地,pmos晶体管mpaaux1、mpbaux1),其将第二类型的mos晶体管mna11、mnb11的栅极连接至下一级(具体地,第二级320)的第二内部升压节点x2b和第一内部升压节点x2a。

69.第二级320包括连接至第二对电容器c2a、c2b的各个开关块,并且各个开关块包括:第一类型的mos晶体管(具体地,nmos晶体管mna2、mnb2),其将第二电压v1分别传送至该级的第一内部升压节点x2a和第二内部升压节点x2b并且交叉联接;第二类型的mos晶体管(具体地,nmos晶体管mna22、mnb22),其将该级的第一内部升压节点x2a和第二内部升压节点x2b处的电压传送至输出节点out并具有由第三类型的mos晶体管mnaaux2、mnbaux2和第四类型的mos晶体管mpaaux2、mpbaux2偏置的栅极;第三类型的mos晶体管(具体地,nmos晶

体管mnaaux2、mnbaux2),其将第二类型的mos晶体管mna22、mnb22的栅极连接至该级的第一内部升压节点x2a和第二内部升压节点x2b;以及第四类型的mos晶体管(具体地,pmos晶体管mpaaux2、mpbaux2),其将第二类型的mos晶体管mna22、mnb22的栅极连接至下一级(具体地,辅助级330)的第二内部升压节点x3b和第一内部升压节点x3a。

70.此外,辅助级330包括连接至输出端子out并交叉联接的第一类型的mos晶体管(具体地,nmos晶体管mna0、mnb0)。

71.图3的电荷泵架构300是二级电荷泵,其组成级为第一级310和第二级320,并且包括辅助级330;然而,可以插入任意数量的级以通过级联属于第一级310或第二级320的类型的若干级并以属于辅助级330的类型的辅助级结束,来制成n级电荷泵。

72.图4中示出了电荷泵架构300的电压和时钟信号。

73.具体而言,第一级310在其输入端子in处接收值等于vcc的输入电压vin,并且使用范围在0和vcc之间的时钟信号ck和反相时钟信号ckb,在内部节点int处提供等于2vcc的第二电压v1。此外,分别处于第一级310的第一电路节点x1a和第二电路节点x1b处的第一升压电压vboost1和第二反相升压电压vboost1b范围在vcc和2vcc之间,并且分别处于第一内部电路节点y1a和第二内部电路节点y1b处的第一控制电压vg1和反相的第一控制电压vgb1范围在vcc和3vcc之间。

74.类似地,第二级320接收值等于2vcc的第二电压v1,并且使用范围在0和vcc之间的时钟信号ck和反相时钟信号ckb,在输出端子out处提供等于3vcc的输出电压vout。此外,分别处于第二级320的第一电路节点x2a和第二电路节点x2b处的第三反相升压电压vboost2b和第四升压电压vboost2范围在2vcc和3vcc之间,并且分别处于第二级320的第一内部电路节点y2a和第二内部电路节点y2b处的第二控制电压vg2和反相的第二控制电压vgb2范围在2vcc和4vcc之间。

75.最后,辅助级330接收值等于3vcc的输出电压vout,并且在辅助级330的第一电路节点x3a和第二电路节点x3b处分别为第三对电容器c3a、c3b提供范围在3vcc和4vcc之间的第五升压电压vboostaux和第六反相升压电压vboostauxb。

76.图4所示的信号在图3的电荷泵架构300中的模式提供了包括在其内的晶体管的交替导通阶段。

77.更具体的,如图5a所示,在如图4所示的与时钟信号ck第一次上升到等于vcc的值对应的第一时间段t1中,在第一级310中,第一开关块312的第二nmos晶体管mnb1、第一开关晶体管结构314a的第一开关nmos晶体管mna11和第二附加开关pmos晶体管mpaaux1以及第二开关晶体管结构314b的第一附加开关nmos晶体管mnbaux1导通。以对称的方式,在第二级320中,第一开关块322的第一nmos晶体管mna2和第一开关晶体管结构324a的第一附加开关nmos晶体管mnaaux2以及第二开关晶体管结构324b的第一开关nmos晶体管mnb22和第二附加开关pmos晶体管mpbaux2导通。最后,辅助级330的辅助开关块332的第二nmos晶体管mnbo也导通。

78.如图5b所示,在如图4所示的与时钟信号ck第一次下降至等于0的值对应的第二时间段t2中,在第一级310中,第一开关块312的第一nmos晶体管mna1、第一开关晶体管结构314a的第一附加开关nmos晶体管mnaaux1、以及第二开关晶体管结构314b的第一开关nmos晶体管mnb11和第二附加开关pmos晶体管mpbaux1导通。以对称的方式,在第二级320中,第

一开关块322的第二nmos晶体管mnb2和第一开关晶体管结构324a的第一开关nmos晶体管mna22和第二附加开关pmos晶体管mpaaux2以及第二开关晶体管结构324b的第一附加开关nmos晶体管mnbaux2导通。最后,辅助级330的辅助开关块332的第一nmos晶体管mnao也导通。

79.图6中示出了电荷泵架构的替代实施方式。

80.电荷泵架构600包括连接至接收第一电压或输入电压vin的输入端子in的第一级或输入级610以及连接至提供输出电压vout的输出端子out的最后级或输出级640,第一级或输入级610和最后级或输出级640借助于第一中间级620和第二中间级630互联。输入级610包括分别由时钟信号ck和反相时钟信号ckb驱动的第一对电容器c1a、c1b,第一中间级620包括分别由反相时钟信号ckb和时钟信号ck驱动的第二对电容器c2a、c2b,并且第二中间级630包括分别由时钟信号ck和反相时钟信号ckb驱动的第三对电容器c3a、c3b。

81.更具体地,输入级610包括连接在输入端子in和第一对电容器c1a、c1b之间的输入开关块612,并且输入开关块612包括:第一nmos晶体管mna1,其插入在输入端子in和第一电路节点x1a之间,进而连接至第一对的第一电容器c1a;以及第二nmos晶体管mnb1,其插入在输入端子in和第二电路节点x1b之间,进而连接至第一对的第二电容器c1b。此外,第一nmos晶体管mna1具有连接至第二电路节点x1b的控制端子或栅极端子,并且第二nmos晶体管mnb1具有连接至第一电路节点x1a的控制端子或栅极端子。第一nmos晶体管mna1在也连接至第二nmos晶体管mnb1的栅极端子的第一电路节点x1a处为第一对的第一电容器c1a提供第一升压电压vboost1,其进而在也连接至第一nmos晶体管mna1的栅极端子的第二电路节点x1b处为第一对的第二电容器c1b提供第二反相升压电压vboost1b。在图6的实施方式中,第一nmos晶体管mna1和第二nmos晶体管mnb1可以是具有连接至其源极端子的体端子的三阱nmos晶体管。然而,可以使用现有技术中已知的其它方案来根据充电泵相位改变体端子连接,以在升压或电荷泵输出下降期间避免体至漏极正向偏置。

82.因此,输入级610的第一电路节点x1a和第二电路节点x1b分别是输入级610的第一内部升压节点和第二内部升压节点。

83.进而,第一中间级620包括中间开关块624,该中间开关块624插入在第一对电容器c1a、c1b和第二对电容器c2a、c2b之间,并且连接至输入级610的第一电路节点x1a和第二电路节点x1b以及第一中间级620的第一电路节点x2a和第二电路节点x2b。更具体地,中间开关块624包括插入在输入级610的第一电路节点x1a与第一中间级620的第一电路节点x2a之间的第一开关晶体管结构624a以及插入在输入级610的第二电路节点x1b与第一中间级620的第二电路节点x2b之间的第二开关晶体管结构624b。

84.第一开关晶体管结构624a和第二开关晶体管结构624b还连接至第一互连节点w1、第二互连节点w2、第三互连节点w3和第四互连节点w4。更具体地,第一开关晶体管结构624a包括:第一开关nmos晶体管mna2,其插入在输入级610的第一电路节点x1a和第一中间级620的第一电路节点x2a之间,并具有连接至第一内部电路节点y2a的控制端子或栅极端子;第一附加开关nmos晶体管mnaaux2,其插入在进而连接至输入级610的第一电路节点x1a的第一互连节点w1与第一内部电路节点y2a之间,并具有连接至第二互连节点w2进而连接至输入级610的第二电路节点x1b的控制端子或栅极端子;以及第二附加开关pmos晶体管mpaaux2,其插入在第一内部电路节点y2a与进而连接至第一中间级620的第二电路节点x2b

的第四互连节点w4之间,并具有连接至第二互连节点w2的控制端子或栅极端子。在图6的实施方式中,第一开关晶体管结构624a的第一开关nmos晶体管mna2和第一附加开关nmos晶体管mnaaux2是具有连接至其源极端子的体端子的三阱nmos晶体管,然而,可以使用现有技术中已知的其它方案来根据充电泵相位改变体端子连接,以在升压或电荷泵输出下降期间避免体至漏极正向偏置。另一方面,第一开关晶体管结构624a的第二附加开关pmos晶体管mpaaux2是具有连接至其源极的体的pmos晶体管。另外,对于该pmos晶体管,可以实现更复杂的方案来管理体连接,以在升压或电荷泵输出下降期间避免漏极至体正向偏置。

85.因此,第一中间级620的第一电路节点x2a和第二电路节点x2b分别是第一中间级620的第一内部升压节点和第二内部升压节点。

86.以对称的方式,第二开关晶体管结构624b包括:第一开关nmos晶体管mnb2,其插入在输入级610的第二电路节点x1b与第一中间级620的第二电路节点x2b之间,并具有连接至第二内部电路节点y2b的控制端子或栅极端子;第一附加开关nmos晶体管mnbaux2,其插入在第二互连节点w2和第二内部电路节点y2b之间,并具有连接至第一互连节点w1进而连接至输入级610的第一电路节点x1a的控制端子或栅极端子;以及第二附加开关pmos晶体管mpbaux2,其插入在第二内部电路节点y2b与进而连接至第一中间级620的第一电路节点x2a的第三互连节点w3之间,并且具有连接至第一互连节点w1的控制端子或栅极端子。在图6的实施方式中,第二开关晶体管结构624b的第一开关nmos晶体管mnb2和第一附加开关nmos晶体管mnbaux2可以是具有连接至其源极端子的体端子的三阱nmos晶体管。然而,可以使用现有技术中已知的其它方案来根据充电泵相位改变体端子连接,以在升压或电荷泵输出下降期间避免体至漏极正向偏置。另一方面,第二开关晶体管结构624b的第二附加开关pmos晶体管mpbaux2是具有连接至其源极的体的pmos晶体管。另外,对于该pmos晶体管,可以实现更复杂的方案来管理体连接,以在升压或电荷泵输出下降期间避免漏极至体正向偏置。第一内部电路节点y2a处于第一控制电压vg1,而第二内部电路节点y2b处于反相的第一控制电压vgb1。

87.此外,第一开关晶体管结构624a的第一nmos晶体管mna2在第一中间级620的第一电路节点x2a处为第二对的第一电容器c2a提供第三反相升压电压vboost2b,而第二开关晶体管结构624b的第一nmos晶体管mnb2在第一中间级620的第二电路节点x2b处为第二对的第二电容器c2b提供第四升压电压vboost2。

88.类似地,第二中间级630包括输出开关块634,该输出开关块634插入在第二对电容器c2a、c2b和第三对电容器c3a、c3b之间,并连接至第一中间级620的第一电路节点x2a和第二电路节点x2b以及第二中间级630的第一电路节点x3a和第二电路节点x3b。更具体地,输出开关块634包括:第一开关晶体管结构634a,其插入在第一中间级620的第一电路节点x2a和第二中间级630的第一电路节点x3a之间;以及第二开关晶体管结构634b,其插入在第一中间级620的第二电路节点x2b和第二中间级630的第二电路节点x3b之间。

89.第一开关晶体管结构634a包括:第一开关nmos晶体管mna3,其插入在第一中间级620的第一电路节点x2a和第二中间级630的第一电路节点x3a之间,并具有连接至第一内部电路节点y3a的控制端子或栅极端子;第一附加开关nmos晶体管mnaaux3,其插入在第三互连节点w3和第一内部电路节点y3a之间,并具有连接至第四互连节点w4的控制端子或栅极端子;以及第二附加开关pmos晶体管mpaaux3,其插入在第二中间级630的第一内部电路节

点y3a和第二电路节点x3b之间,并具有连接至第四互连节点w4的控制端子或栅极端子。在图6的实施方式中,第一开关晶体管结构634a的第一开关nmos晶体管mna3和第一附加开关nmos晶体管mnaaux3可以是具有连接至其源极端子的体端子的三阱nmos晶体管。然而,可以使用现有技术中已知的其它方案来根据充电泵相位改变体端子连接,以在升压或电荷泵输出下降期间避免体至漏极正向偏置。另一方面,第一开关晶体管结构634a的第二附加开关pmos晶体管mpaaux3是具有连接至其源极的体的pmos晶体管。另外,对于该pmos晶体管,可以实现更复杂的方案来管理体连接,以在升压或电荷泵输出下降期间避免漏极至体正向偏置。

90.以对称的方式,第二开关晶体管结构634b包括:第一开关nmos晶体管mnb3,其插入在第一中间级620的第二电路节点x2b和第二中间级630的第二电路节点x3b之间,并具有连接至第二内部电路节点y3b的控制端子或栅极端子;第一附加开关nmos晶体管mnbaux3,其插入在第四互连节点w4和第二内部电路节点y3b之间,并且具有连接至第三互连节点w3的控制端子或栅极端子;以及第二附加开关pmos晶体管mpbaux3,其插入在第二中间级630的第二内部电路节点y3b和第一电路节点x3a之间,并具有连接至第三互连节点w3的控制端子或栅极端子。在图6的实施方式中,第二开关晶体管结构634b的第一开关nmos晶体管mnb3和第一附加开关nmos晶体管mnbaux3可以是具有连接至其源极端子的体端子的三阱nmos晶体管。然而,可以使用现有技术中已知的其它方案来根据充电泵相位改变体端子连接,以在升压或电荷泵输出下降期间避免体至漏极正向偏置。另一方面,第二开关晶体管结构634b的第二附加开关pmos晶体管mpbaux3是具有连接至其源极的体的pmos晶体管。另外,对于该pmos晶体管,可以实现更复杂的方案来管理体连接,以在升压或电荷泵输出下降期间避免漏极至体正向偏置。第一内部电路节点y3a处于第二控制电压vg2,而第二内部电路节点y3b处于反相的第一控制电压vgb2。

91.因此,第二中间级630的第一电路节点x3a和第二电路节点x3b分别是第二中间级630的第一内部升压节点和第二内部升压节点。

92.第一开关晶体管结构634a的第一nmos晶体管mna3在第一电路节点x3a处为第三对的第一电容器c3a提供第五升压电压vboost3,而第二开关晶体管结构634b的第一nmos晶体管mnb3在第二电路节点x3b处为第三对的第二电容器c3b提供第六反相升压电压vboost3b。

93.电荷泵架构600还包括插入在第三对电容器c3a、c3b和输出端子out之间的输出级640。更具体地,输出级640包括:第一pmos晶体管mpa3,其插入在进而连接至第三对的第一电容器c3a的第一电路节点x3a与输出端子out之间;以及第二pmos晶体管mpb3,其插入在进而连接至第三对的第二电容器c3b的第二电路节点x3b与输出端子out之间。此外,第一pmos晶体管mpa3具有连接至第二电路节点x3b的控制端子或栅极端子,而第二pmos晶体管mpb3具有连接至第一电路节点x3a的控制端子或栅极端子。第一pmos晶体管mpa3和第二pmos晶体管mpb3具有连接至其源极端子的体端子,然而,可以实现更复杂的方案来管理体连接,以在升压或电荷泵输出下降期间避免漏极至体正向偏置。

94.根据本实施方式,电荷泵架构600包括:输入端子in和输出端子out;第一级或输入级610,该第一或输入级610在其输入端子(这也是电荷泵的输入端子in)处接收输入电压vin作为第一电压,并在其第一输出端子x1a和第二输出端子x1b处输出第一升压电压vboost1和第二升压电压vboost1b;第一中间级620,该第一中间级620连接至第一级610的

作为第一对内部升压节点的第一输出端子x1a和第二输出端子x1b,并且从其接收输入级610的第一升压电压vboost1和第二升压电压vboost1b并且在其第一输出端子x2a和第二输出端子x2b处输出第三升压电压vboost2b和第四升压电压vboost2;第二中间级630,该第二中间级630连接至第一中间级620的作为第二对内部升压节点的第一输出端子x2a和第二输出端子x2b,并且从其接收第一中间级620的第三升压电压vboost2b和第四升压电压vboost2并且在其第一输出端子x3a和第二输出端子x3b处输出第五升压电压vboost3和第六升压电压vboost3b;以及最后级或输出级640,该最后级或输出级640连接至第二中间级630的作为第三对内部升压节点的第一输出端子x3a和第二输出端子x3b,并且从其接收第二中间级630的第五升压电压vboost3和第六升压电压vboost3b并且在其输出端子(也是电荷泵的输出端子out)处输出电压vout,其中,第一级610包括连接至第一对升压节点x1a、x1b的第一对电容器c1a、c1b,第一中间级620包括连接至第二对内部升压节点x2a、x2b的第二对电容器c2a、c2b,并且第二中间级630包括连接至相应的第三对内部升压节点x3a、x3b的第三对电容器c3a、c3b。

95.第一级610还包括第一类型的mos晶体管(具体地,nmos晶体管mna1、mnb1),其将输入电压vin传送至其第一输出端子x1a和第二输出端子x1a。

96.此外,第一中间级620包括:联接至第一级610的输出端子x1a和x1b的一对输入端子以及一对输出端子x2a、x2b;第二类型的mos晶体管(具体地,nmos晶体管mna2、mnb2),其将第一输入端子x1a和第二输入端子x1b处的第一升压电压vboost1和第二升压电压vboost1b传送至第一中间级620的第一输出端子x2a和第二输出端子x2b;以及第三类型的mos晶体管(具体地,nmos晶体管mnaaux2、mnbaux2),其将第二类型的mos晶体管mna2、mnb2的栅极连接至输入端子;以及第四类型的mos晶体管(具体地,pmos晶体管mpaaux2、mpbaux2),其将第二类型的mos晶体管mna2、mnb2的栅极分别连接至第二输出端子x2b和第一输出端子x2a,进而连接至下一级(具体地,第二中间级630)。

97.类似地,第二中间级630包括:联接至第一中间级620的输出端子x2a和x2b的一对输入端子以及一对输出端子x3a、x3b;第二类型的mos晶体管(具体地,nmos晶体管mna3、mnb3),其将输入端子处的第三升压电压vboost2b和第四升压电压vboost2传送至第二中间级630的第一输出端子x3a和第二输出端子x3b;第三类型的mos晶体管(具体地,nmos晶体管mnaaux3、mnbaux3),其将第二类型的mos晶体管mna3、mnb3的栅极连接至输入端子;以及第四类型的mos晶体管(具体地,pmos晶体管mpaaux3、mpbaux3),其将第二类型的mos晶体管mna3、mnb3的栅极分别连接至输出端子x3b、x3a,进而连接至下一级(具体地,最后级或输出级640)。

98.最后,最后级或输出级640包括:联接至第二中间级630的输出端子x3a、x3b的一对输入端子以及一个输出端子out,该输出端子out也是电荷泵的输出端子;第五类型的mos晶体管(具体地,pmos交叉联接晶体管mpa3、mpb3),其将输入端子处的第五升压电压vboost3和第六升压电压vboost3b传送至输出端子out。

99.图6的电荷泵架构600是三级电荷泵,其组成级为输入级610、第一中间级620、第二中间级630和输出级640,然而,可以插入任意数量的级以制成n级电荷泵。

100.图7中示出了电荷泵架构600的电压和时钟信号。

101.具体而言,输入级610在其输入端子in处接收值等于vcc的输入电压vin,并由范围

在0和vcc之间的时钟信号ck和反相时钟信号ckb驱动。此外,分别在输入级610的第一电路节点x1a和第二电路节点x1b处的第一升压电压vboost1和第二升压电压vboost1b范围在vcc与2vcc之间。

102.第一升压电压vboost1和第二升压电压vboost1b被提供给连接至第一中间级620的第一互连节点w1和第二互连节点w2。

103.在第一中间级620中,分别在第一中间级620的第一内部电路节点y2a和第二内部电路节点y2b处的第一控制电压vg1和反相的第一控制电压vgb1范围在vcc和3vcc之间,并且分别在第一中间级620的第一电路节点x2a和第二电路节点x2b处的第三升压电压vboostb2和第四升压电压vboost2范围在2vcc和3vcc之间,并且被提供给第三互连节点w3和第四互连节点w4。

104.类似地,在第二中间级630中,分别在第二中间级630的第一电路节点x3a和第二电路节点x3b处的第五升压电压vboost3和第六升压电压vboost3b范围在3vcc和4vcc之间,而分别在第二中间级630的第一内部电路节点y3a和第二内部电路节点y3b处的第二控制电压vg2和反相的第二控制电压vgb2范围在2vcc和4vcc之间。

105.以此方式,电荷泵架构600在输出端子out处提供值为4vcc的输出电压vout。

106.图7中所示的信号在图6的电荷泵架构600中的模式提供了包括在其内的晶体管的交替导通阶段。

107.更具体地,如图8a所示,在如图7所示的与时钟信号ck第一次上升到等于vcc的值对应的第一时间段t1内,在输入级610中,第一开关块612的第二nmos晶体管mnb1导通。此外,在第一中间级620中,第一开关晶体管结构624a的第一开关nmos晶体管mna2和第二附加开关pmos晶体管mpaaux2以及第二开关晶体管结构624b的第一附加开关nmos晶体管mnbaux2导通。以对称的方式,在第二中间级630中,第一开关晶体管结构634a的第一附加开关nmos晶体管mnaaux3以及第二开关晶体管结构634b的第一开关nmos晶体管mnb3和第二附加开关pmos晶体管mpbaux3导通。最后,输出级640的第一pmos晶体管mpa3也导通。

108.如图8b所示,在如图7所示的与时钟信号ck第一次下降至等于0的值对应的第二时间段t2中,在输入级610中,第一开关块612的第一nmos晶体管mna1导通。此外,在第一中间级620中,第一开关晶体管结构624a的第一附加开关nmos晶体管mnaaux2以及第二开关晶体管结构624b的第一开关nmos晶体管mnb2和第二附加开关pmos晶体管mpbaux2导通。以对称的方式,在第二中间级630中,第一开关晶体管结构634a的第一开关nmos晶体管mna3和第二附加开关pmos晶体管mpaaux3以及第二开关晶体管结构324b的第一附加开关nmos晶体管mnbaux3导通。最后,输出级640的第二nmos晶体管mnb3也导通。

109.根据另一实施方式,连接至电荷泵架构的每一级的时钟信号和反相时钟信号彼此适当地移位。具体而言,在驱动该级的时钟信号和反相时钟信号中插入延迟时段t

delay

,以相对于前一级的时钟信号和反相时钟信号提前移位时钟信号,如图9所示,对于分别由第一时钟信号和反相的第一时钟信号第二时钟信号和反相的第二时钟信号以及第三时钟信号和反相的第三时钟信号驱动的三级的序列,第二时钟信号和反相的第二时钟信号相对于第一时钟信号和反相的第一时钟信号提前了延迟时段t

delay

,并且第三时钟信号和反相的第三时钟信号相对于第二时钟信号和反相的第二时钟信号提前了延迟时段t

delay

。

110.可以验证不同级的时钟信号和反相时钟信号之间的移位能够减少所谓的反向电荷传导效应,从而提高驱动移位时钟信号和反相时钟信号的电荷泵架构的效率。

111.根据实施方式的电荷泵架构,使用具有比pmos晶体管更高的电导的nmos晶体管,允许在相同电导下减小其内所包括的开关块和开关晶体管结构的面积,从而减小作为整体的架构的硅面积和寄生电容。另选地,在相同的面积上,能够降低耗散功率。

112.此外,使用时钟信号和反相时钟信号之间的移位来驱动不同的级,根据实施方式的电荷泵架构表现出降低的反向电荷传导效应。

113.从上文将理解,虽然出于示例的目的已经在本文中描述了本发明的特定实施方式,但是在不脱离本发明的精神和范围的情况下可以进行各种修改。因此,除了如所附权利要求之外,本发明不受限制。

114.相关申请的交叉引用

115.本技术要求基于2021年2月5日提交的意大利专利申请no.102021000002585的优先权,该意大利专利申请的公开内容通过引用整体并入本文中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1