带隙基准电路的制作方法

本公开涉及电子电路,更具体地,涉及一种带隙基准电路。

背景技术:

1、由于模拟电路中的电阻、三极管等器件具有一定的温度系数,使得所提供的基本电压在一定程度上受到温度的影响,从而造成偏差。在模拟电路中,常需要与温度几乎无关的电压基准为三极管和其他电路元器件提供精准的偏置,因此带隙基准电路受到广泛的应用。

2、带隙基准电路的原理是将在某一温度下的两个具有正负温度系数的电压以适当的权重相加,由于其相反的温度特性,可近似得到一个零温度系数的电压基准,以减小由于温度漂移引起的输出电压变化。但由于具有正负温度系数的两个电压具有不同的阶数,两个电压之间存在不能抵消补偿的高阶分量,导致带隙基准电路的精度不够高。

技术实现思路

1、本公开的一个目的是提供一种用于对带隙基准子电路进行电压补偿的带隙基准电路,可以对带隙基准子电路进行电压补偿,提高带隙基准子电路的精度。

2、根据本公开的第一方面,提供了一种带隙基准电路。

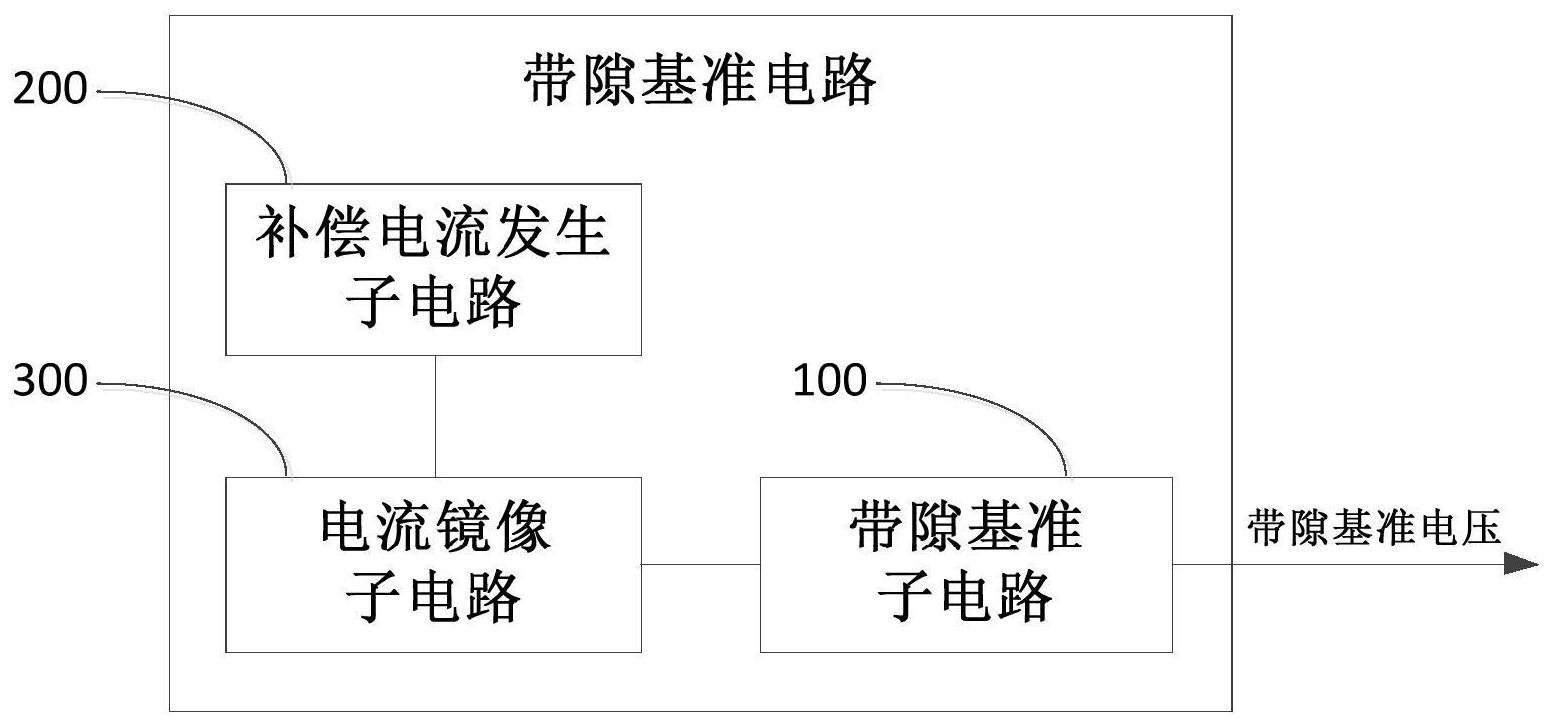

3、该带隙基准电路包括带隙基准子电路、补偿电流发生子电路和电流镜像子电路;所述电流镜像子电路分别与所述补偿电流发生子电路、所述带隙基准子电路连接;所述带隙基准子电路,用于生成带隙基准电压;所述补偿电流发生子电路,用于生成具有温度特性的补偿电流;所述电流镜像子电路,用于对所述补偿电流进行镜像生成镜像电流,通过所述镜像电流对所述带隙基准电压进行电压补偿。

4、可选地,所述补偿电流发生子电路包括第一三极管;所述第一三极管的集电极和所述带隙基准电路的工作电压端连接;所述第一三极管的发射极和所述带隙基准子电路连接,以向所述带隙基准子电路提供工作电压;所述第一三极管的基极产生所述补偿电流。

5、可选地,所述补偿电流发生子电路包括第一三极管;所述第一三极管的集电极和所述带隙基准电路的工作电压端连接;所述第一三极管的发射极和第一电流源连接;所述第一三极管的基极产生所述补偿电流。

6、可选地,所述电流镜像子电路包括第一电流镜、第二电流镜和第一电阻;第一电流镜的第一镜像电流端口、第一三极管的基极、第一电阻的第一端分别连接至第一电路节点;第二电流镜的第一镜像电流端口与第一电阻的第二端连接;第一电流镜的第二镜像电流端口、第二电流镜的第二镜像电流端口分别连接至第二电路节点;所述电流镜像子电路与所述带隙基准子电路连接,包括:所述第二电路节点与所述带隙基准子电路连接。

7、可选地,所述第一电流镜为共源共栅电流镜。

8、可选地,所述第一电流镜包括第一至第六pmos管;第一至第三pmos管的栅极连接在一起,第一至第三pmos管的源极分别与所述带隙基准电路的工作电压端连接;第四至第六pmos管的栅极连接在一起;第一pmos管的漏极和第四pmos管的源极连接,第二pmos管的漏极和第五pmos管的源极连接,第三pmos管的漏极和第六pmos管的源极连接;第四pmos管的漏极和第二电流源连接,第五pmos管的漏极连接至第一电路节点,第六pmos管的漏极连接至第二电路节点;第一pmos管的漏极和栅极连接,第四pmos管的漏极和栅极连接;其中,第五pmos管的漏极为第一电流镜的第一镜像电流端口,第六pmos管的漏极为第一电流镜的第二镜像电流端口。

9、可选地,所述第二电流镜包括第一至第四nmos管;第一nmos管的栅极和第二noms管的栅极连接;第三nmos管的栅极和第四noms管的栅极连接;第一nmos管的漏极与第一电阻的第二端连接,第二nmos管的漏极连接至第二电路节点;第一nmos管的源极和第三nmos管的漏极连接,第二nmos管的源极和第四nmos管的漏极连接;第一nmos管的漏极和栅极连接,第三pmos管的漏极和栅极连接;第三nmos管的源极和第四noms管的源极分别接地;其中,第一nmos管的漏极为第二电流镜的第一镜像电流端口,第二nmos管的漏极为第二电流镜的第二镜像电流端口。

10、可选地,所述带隙基准子电路包括运算放大器、第二三极管、第三三极管、第二电阻以及第三电阻;运算放大器的第一输入与第二三极管的集电极连接,第二输入端与第三三极管的集电极连接;第二三极管的基极和第三三极管的基极连接,第三三极管的发射极与第二电阻的第一端连接,第二三极管的发射极和第二电阻的第二端连接;第二电阻的第二端与第三电阻的第一端连接,第三电阻的第二端接地;运算放大器的输出端与第三三极管的基极连接,以输出带隙基准电压;所述第二电路节点与所述带隙基准子电路连接,包括:所述第二电路节点与第三电阻的第一端连接。

11、可选地,所述带隙基准子电路包括运算放大器、第二三极管、第三三极管、第二电阻、第三电阻以及第四电阻;运算放大器的第一输入与第二三极管的集电极连接,第二输入端与第三三极管的集电极连接;第二三极管的基极和第三三极管的基极连接,第三三极管的发射极与第二电阻的第一端连接,第二三极管的发射极和第二电阻的第二端连接;第二电阻的第二端与第四电阻的第一端连接,第四电阻的第二端与第三电阻的第一端连接,第三电阻的第二端接地;运算放大器的输出端与第二三极管的基极连接,以输出带隙基准电压;所述第二电路节点与所述带隙基准子电路连接,包括:所述第二电路节点与第三电阻的第一端连接。

12、可选地,所述第一三极管为npn型三极管、所述第二三极管为npn型三极管、所述第三三极管为npn型三极管。

13、本公开实施例提供的带隙基准电路,具有高阶温度补偿功能,使得带隙基准电路对于温度的变化更加不敏感,输出的带隙基准电压曲线更加平缓,具有更小的幅度变化,实现了高精度带隙基准电压的输出。

14、通过以下参照附图对本公开的示例性实施例的详细描述,本公开的其它特征及其优点将会变得清楚。

技术特征:

1.一种带隙基准电路,其特征在于,所述带隙基准电路包括带隙基准子电路、补偿电流发生子电路和电流镜像子电路;

2.根据权利要求1所述的带隙基准电路,其特征在于,所述补偿电流发生子电路包括第一三极管(q3);

3.根据权利要求1所述的带隙基准电路,其特征在于,所述补偿电流发生子电路包括第一三极管(q3);

4.根据权利要求1-3任一项所述的带隙基准电路,其特征在于,所述电流镜像子电路包括第一电流镜、第二电流镜和第一电阻(r6);

5.根据权利要求4所述的带隙基准电路,其特征在于,所述第一电流镜为共源共栅电流镜。

6.根据权利要求5所述的带隙基准电路,其特征在于,所述第一电流镜包括第一至第六pmos管;

7.根据权利要求4所述的带隙基准电路,其特征在于,所述第二电流镜包括第一至第四nmos管;

8.根据权利要求4-7任一项所述的带隙基准电路,其特征在于,所述带隙基准子电路包括运算放大器(amp)、第二三极管(q1)、第三三极管(q2)、第二电阻(r3)以及第三电阻(r5);

9.根据权利要求4-7任一项所述的带隙基准电路,其特征在于,所述带隙基准子电路包括运算放大器(amp)、第二三极管(q1)、第三三极管(q2)、第二电阻(r3)、第三电阻(r5)以及第四电阻(r4);

10.根据权利要求8-9任一项所述的带隙基准电路,其特征在于,所述第一三极管(q3)为npn型三极管、所述第二三极管(q1)为npn型三极管、所述第三三极管(q2)为npn型三极管。

技术总结

本公开提供了带隙基准电路。所述带隙基准电路包括带隙基准子电路、补偿电流发生子电路和电流镜像子电路;所述电流镜像子电路分别与所述补偿电流发生子电路、所述带隙基准子电路连接;所述带隙基准子电路,用于生成带隙基准电压;所述补偿电流发生子电路,用于生成具有温度特性的补偿电流;所述电流镜像子电路,用于对所述补偿电流进行镜像生成镜像电流,通过所述镜像电流对所述带隙基准电压进行电压补偿。

技术研发人员:陈胜胜,白淳,郭亮亮,杨云

受保护的技术使用者:比亚迪半导体股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!