一种LVDS发送器的制作方法

一种lvds发送器

技术领域

1.本技术涉及电子技术领域,尤其涉及一种lvds发送器。

背景技术:

2.目前,为了稳定低压差分信号(low-voltage differential signal,lvds)驱动电路输出端的共模电压,通常会在lvds驱动电路中加入共模反馈(common mode feedback,cmfb)电路。

3.图1为现有技术提供的一种lvds发送器的结构示意图,该lvds发送器包括:相互耦合的驱动电路和cmfb电路。该驱动电路用于输出差分电压v1和v2,该cmfb电路用于接收该差分电压v1和v2并根据该差分电压v1和v2确定共模电压vc,进一步根据该共模电压vc输出反馈电压vf。其中,该驱动电路包括:6个晶体管且表示为m1至m6,晶体管m1耦合于电源端(vdd)和第一节点p1之间,晶体管m6耦合于第二节点p2和接地端(gnd)之间,晶体管m1的漏极与vdd耦合,晶体管m6的源极与gnd耦合,晶体管m2和晶体管m4串联耦合于第一节点p1和第二节点p2之间,晶体管m3和晶体管m5串联耦合于第一节点p1和第二节点p2之间,第一差分输出端与晶体管m3的源极耦合,第二差分输出端与晶体管m2的源极耦合,晶体管m1的栅极可用于接收偏置电压ve,晶体管m2的栅极和晶体管m5的栅极可分别用于接收第一控制信号c1,晶体管m3的栅极和晶体管m4的栅极可分别用于接收第二控制信号c2,晶体管m6的的栅极可用于接收反馈电压vf。该cmfb电路包括:第一电阻r1、第二电阻r2和运算放大器op。第一电阻r1和第二电阻r2串联耦合于第一差分输出端和第二差分输出端之间,第一电阻r1和第二电阻r2耦合于节点p3,节点p3处的电压为共模电压vc,运算放大器op的负极用于接收共模电压vc,运算放大器op的正极用于接收基准电压v

bg

。具体的,驱动电路在工作的过程中,晶体管m1和晶体管m6均为电流源。t1时刻,该第一控制信号c1可用于控制晶体管m2和晶体管m5导通,该第二控制信号c2可用于控制晶体管m3和晶体管m4关断,此时,第一差分输出端和第二差分输出端输出第一差分电压v

11

和v

12

,该第二电阻r2和该第一电阻r1根据该第一差分电压v

11

和v

12

确定第一共模电压v

c1

,运算放大器op的正极接收该第一共模电压v

c1

,并将该第一共模电压v

c1

与基准电压v

bg

比较后输出反馈电压vf,晶体管m6的栅极接收该反馈电压vf;t2时刻,该第一控制信号c1可用于控制晶体管m2和晶体管m5关断,该第二控制信号c2可用于控制晶体管m3和晶体管m4导通,由于晶体管m6的栅极接收该反馈电压vf,该反馈电压vf改变晶体管m6中的电流,进一步改变了驱动电路中的电流,此时第一差分输出端和第二差分输出端输出第二差分电压v

21

和v

22

,该第一电阻r1和该第二电阻r2根据该第二差分电压v

21

和v

22

后确定第二共模电压v

c2

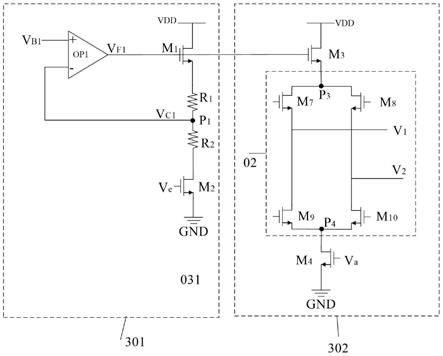

。该lvds发送器通过cmfb电路的反馈电压来改变晶体管m6的栅极电压,进一步改变驱动电路中,从而达到稳定共模电压的目的。

4.但是,该lvds发送器中,cmfb电路中的电流与驱动电路中的电流相同,若cmfb电路中的电流太大,这样会导致cmfb电路中产生较大的功耗,若cmfb电路中的电流太小,则不能在很短的时间内对共模电压进行有效的调节;另外,第一电阻和第二电阻的阻值很大,通常在千欧(kω)量级以上,从而将第一电阻和第二电阻集成在芯片上时,占用大量的芯片面

积。

技术实现要素:

5.本技术提供一种低电压差分信号lvds发送器,用于解决lvds发送器中功耗较大的问题。

6.为达到上述目的,本技术采用如下技术方案:

7.第一方面,提供一种lvds发送器,该lvds发送器包括第一共模反馈电路和驱动电路,该第一共模反馈电路的输出端与该驱动电路的第一输入端耦合;该第一共模反馈电路包括:第一运算放大器、以及依次串联耦合在电源端和接地端之间的第一晶体管、第一电阻、第二电阻和第二晶体管;其中,该第一电阻和该第二电阻耦合于第一节点,该第一运算放大器的第一输入端耦合于该第一节点,该第一运算放大器的第二输入端用于接收第一基准电压,该第一运算放大器的输出端与该第一晶体管的栅极和该第一共模反馈电路的输出端耦合,该第二晶体管的栅极用于接收偏置电压;该驱动电路包括:依次串联耦合在该电源端和该接地端之间的第三晶体管、差分电路和第四晶体管;其中,该第三晶体管的栅极与该驱动电路的第一输入端耦合,该差分电路的差分输出端作为与该驱动电路的差分输出端用于输出差分电压;其中,该第三晶体管的电流大于该第一晶体管的电流,且与该第一晶体管的电流之间存在线性关系。

8.上述技术方案中,该第三晶体管的电流大于该第一晶体管的电流,且与该第一晶体管的电流之间存在线性关系,即该驱动电路的电流大于该第一共模反馈电路的电流,且与第一共模反馈电路的电流之间存在线性关系,该第一共模反馈电路根据偏置电压在第一节点处产生第一共模电压,并根据该第一共模电压和第一基准电压输出第一反馈电压,该驱动电路用于根据驱动电路的电流(大电流)产生差分电压并接收该第一反馈电压,该差分电压用于确定第二共模电压,该第一反馈电压用于调节该差分电压以稳定该第二共模电压,从而快速稳定该第二共模电压,与串联两个电阻的lvds发送器(cmfb电路中的电流与驱动电路中的电流相同,为了快速稳定驱动电路中的共模电压,必须增大驱动电路中的电流)相比,该共模反馈电路中的电流小,因此该共模反馈电路中的功耗小,从而在快速稳定该第二共模电压的同时,降低了共模反馈电路中的功耗;另一方面,该第一电阻和该第二电阻的阻值很小,通常为几百欧姆(ω),当该第一电阻和该第二电阻集成在芯片上时,占用芯片的面积小。

9.在第一方面的一种可能的实现方式中,该第三晶体管的尺寸大于该第一晶体管的尺寸。上述可能的实现方式中,当该第三晶体管和该第一晶体管为共栅极连接时,该第三晶体管和该第一晶体管构成了电流镜,使得该第三晶体管中的电流大于该第一晶体管中的电流,且该第三晶体管中的电流与该第一晶体管中的电流呈倍数关系,提高了该第三晶体管中的电流。

10.在第一方面的一种可能的实现方式中,该lvds发送器还包括:第二共模反馈电路,该第二共模反馈电路的输入端与该第一共模反馈电路的输出端耦合,该第二共模反馈电路的输出端与该驱动电路的第二输入端耦合;该第二共模反馈电路包括:第二运算放大器、以及依次串联耦合在该电源端和该接地端之间的第五晶体管、第三电阻、第四电阻和第六晶体管;其中,该第三电阻和该第四电阻耦合于第二节点,该第二运算放大器的第一输入端耦

合于该第二节点,该第二运算放大器的第二输入端用于接收第二基准电压,该第二运算放大器的输出端与该第六晶体管的栅极和该第二共模反馈电路的输出端耦合,该第五晶体管的栅极与该第二共模反馈电路的输入端耦合。上述可能的实现方式中,该第二共模反馈电路接收该第一共模反馈电路输出的第一反馈电压,可以根据该第一反馈电压在第二节点处产生第三共模电压,并根据该第三共模电压和第二基准电压输出第二反馈电压,该第二反馈电压用于调节该差分电压以稳定该第二共模电压,利用该第一共模反馈电路和该第二共模反馈电路共同稳定该第二共模电压,从而提高了稳定该第二共模电压的速度;另一方面,该第三电阻和该第四电阻的阻值很小,通常为几百欧姆(ω),当该第三电阻和该第四电阻集成在芯片上时,占用芯片的面积小。

11.在第一方面的一种可能的实现方式中,该第四晶体管的尺寸大于该第六晶体管的尺寸。上述可能的实现方式中,当该第四晶体管和该第六晶体管为共栅极连接时,该第四晶体管和该第六晶体管构成了电流镜,使得该第四晶体管中的电流大于该第六晶体管中的电流,且该第四晶体管中的电流与该第六晶体管中的电流呈倍数关系,提高了该第六晶体管中的电流。

12.在第一方面的一种可能的实现方式中,该差分电路与该第三晶体管耦合于第三节点,该差分电路与该第四晶体管耦合于第四节点,该差分电路还包括:第七晶体管、第八晶体管、第九晶体管和第十晶体管,该第七晶体管和该第八晶体管分别耦合于该第三节点和该差分输出端之间,该第九晶体管和该第十晶体管分别耦合于该差分输出端和该第四节点之间。上述可能的实现方式中,当该驱动电路接收到串行信号时,该驱动电路可用于将串行信号转换为并行的lvds信号输出,该lvds信号在传输时,可以提高信号的传输速率。

13.在第一方面的一种可能的实现方式中,该偏置电压为固定电压。上述可能的实现方式中,当该第二晶体管的栅极接收到该偏置电压时,使得该第二晶体管为恒流源,即该第一共模反馈电路中的电流为一恒定值。

14.在第一方面的一种可能的实现方式中,该第二晶体管和该第四晶体管为恒流源。上述可能的实现方式中,该第二晶体管和该第四晶体管为恒流源,保证了该第二晶体管和该第四晶体管的稳定性。

15.在第二方面提供一种芯片,该芯片包括lvds发送器,该lvds发送器为上述第一方面或第一方面的任一种可能的实现方式所提供的lvds发送器。

16.在第三方面提供一种lvds接口,该lvds接口中包括lvds发送器,该lvds发送器为上述第一方面或第一方面的任一种可能的实现方式所提供的lvds发送器。

17.在第四方面提供一种终端设备,该终端设备包括输入\输出接口,该输入\输出接口中包括lvds发送器,该lvds发送器为上述第一方面或第一方面的任一种可能的实现方式所提供的lvds发送器。

18.可以理解地,上述提供的芯片、lvds接口和终端设备中均包含了上文所提供的lvds发送器的所有内容,因此,其所能达到的有益效果可参考上文所提供的lvds发送器中的有益效果,此处不再赘述。

附图说明

19.图1为现有技术提供的一种lvds发送器的结构示意图;

20.图2为本技术实施例提供的一种终端设备的结构示意图;

21.图3为本技术实施例提供的一种lvds发送器的结构示意图;

22.图4为本技术实施例提供的另一种lvds发送器的结构示意图。

具体实施方式

23.本技术中,“至少一个”是指一个或者多个,“多个”是指两个或两个以上。“和/或”,描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b的情况,其中a,b可以是单数或者复数。“以下至少一项(个)”或其类似表达,是指的这些项中的任意组合,包括单项(个)或复数项(个)的任意组合。例如,a,b,或c中的至少一项(个),可以表示:a,b,c,a和b,a和c,b和c,或a、b和c,其中a,b,c可以是单个,也可以是多个。

24.本技术的实施例采用了“第一”和“第二”等字样对名称或功能或作用类似的对象进行区分,本领域技术人员可以理解“第一”和“第二”等字样并不对数量和执行次序进行限定。“耦合”一词用于表示电性连接,包括通过导线或连接端直接相连或通过其他器件间接相连。因此“耦合”应被视为是一种广义上的电子通信连接。

25.在本技术实施例中的晶体管可以是指金属氧化物半导体(metal oxide semiconductor,mos),该晶体管的类型可以包括n型金属氧化物半导体(n-type metal oxide semiconductor,nmos)管和p型金属氧化物半导体(p-type metal oxide semiconductor,pmos)管,该晶体管也可以是其他类型的晶体管,比如氮化镓型晶体管,本技术实施例中的晶体管均以nmos为例进行说明。另外,本文中串联耦合的两个晶体管可以是指这两个晶体管中第一个晶体管的源极与第二个晶体管的漏极相连,第一个晶体管的漏极和第二个晶体管的源极均与外部电路相连的意思。

26.本技术实施例提供的技术方案可应用于各种包括低压差分信号(low-voltage differential signal,lvds)发送器的终端设备中,该终端设备可以包括但不限于个人计算机、服务器计算机、移动设备(比如手机、平板电脑、媒体播放器等)、可穿戴设备、车载设备、消费型终端设备、移动机器人和无人机等。下面对该终端设备的具体结构进行介绍说明。

27.图2为本技术实施例提供的一种终端设备的结构示意图,该终端设备以笔记本电脑为例进行说明。如图2所示,该终端设备可以包括:存储器201、处理器202、传感器组件203、多媒体组件204和输入\输出接口205。

28.其中,存储器201可用于存储数据、软件程序以及软件模块;主要包括存储程序区和存储数据区,其中,存储程序区可存储操作系统和至少一个功能所需的应用程序,比如声音播放功能或图像播放功能等;存储数据区可存储根据终端设备的使用所创建的数据,比如音频数据、图像数据、或表格数据等。此外,终端设备可以包括高速随机存取存储器,还可以包括非易失性存储器,例如至少一个磁盘存储器件、闪存器件、或其他易失性固态存储器件。

29.处理器202是终端设备的控制中心,利用各种接口和线路连接整个设备的各个部分,通过运行或执行存储在存储器201内的软件程序和/或软件模块,以及调用存储在存储器201内的数据,执行终端设备的各种功能和处理数据,从而对终端设备进行整体监控。可

选地,处理器202可以包括一个或多个处理单元,比如,上述处理器202可以包括中央处理器(central processing unit,cpu)、应用处理器(application processor,ap)、调制解调处理器、图形处理器(graphics processing unit,gpu)、图像信号处理器(image signal processor,isp)、控制器、视频编解码器、数字信号处理器(digital signal processor,dsp)、基带处理器和/或神经网络处理器(neural-networkprocessing unit,npu)等。其中,不同的处理单元可以是独立的器件,也可以集成在一个或多个处理器中。

30.传感器组件203包括一个或多个传感器,用于为终端设备提供各个方面的状态评估。其中,传感器组件203可以包括加速度传感器、陀螺仪传感器、磁传感器、压力传感器或温度传感器,通过传感器组件203可以检测到终端设备的加速/减速、方位、打开/关闭状态、组件的相对定位或终端设备的温度变化等。此外,传感器组件203还可以包括光传感器,此外,传感器组件203还可以包括光传感器,用于检测周围环境的灯光。

31.多媒体组件204在终端设备和用户之间的提供一个输出接口的屏幕,该屏幕可以为触摸面板,且当该屏幕为触摸面板时,屏幕可以被实现为触摸屏,以接收来自用户的输入信号。触摸面板包括一个或多个触摸传感器以感测触摸、滑动和触摸面板上的手势。所述触摸传感器可以不仅感测触摸或滑动动作的边界,而且还检测与所述触摸或滑动操作相关的持续时间和压力。此外,多媒体组件204还包括至少一个摄像头,比如,多媒体组件204包括一个前置摄像头和/或后置摄像头。当终端设备处于操作模式,如拍摄模式或视频模式时,前置摄像头和/或后置摄像头可以接收外部的多媒体数据。每个前置摄像头和后置摄像头可以是一个固定的光学透镜系统或具有焦距和光学变焦能力。

32.输入\输出接口205为处理器202和外围接口模块之间提供接口,比如,外围接口模块可以是通用串行总线(universal serial bus,usb)设备。在本技术实施例中,输入\输出接口205可以包括本文所提供的lvds发送器,该lvds发送器用于将接收到的串行信号转换为并行的lvds信号。

33.尽管未示出,终端设备还可以包括音频组件和通信组件等,比如,音频组件包括麦克风,通信组件包括无线保真(wireless fidelity,wifi)模块或蓝牙模块等,本技术实施例在此不再赘述。本领域技术人员可以理解,图2中示出的终端设备结构并不构成对该终端设备的限定,可以包括比图示更多或更少的部件,或者组合某些部件,或者不同的部件布置。

34.图3为本技术实施例提供的一种lvds发送器的结构示意图,该lvds发送器包括第一共模反馈电路301和驱动电路302,该第一共模反馈电路301的输出端与该驱动电路302的第一输入端耦合;该第一共模反馈电路301包括:第一运算放大器op1、以及依次串联耦合在电源端(vdd)和接地端(gnd)之间的第一晶体管m1、第一电阻r1、第二电阻r2和第二晶体管m2;其中,该第一电阻r1和该第二电阻r2耦合于第一节点p1,该第一运算放大器op1的第一输入端耦合于该第一节点p1,该第一运算放大器op1的第二输入端用于接收第一基准电压v

b1

,该第一运算放大器op1的输出端与该第一晶体管m1的栅极和该第一共模反馈电路301的输出端耦合,该第二晶体管m2的栅极用于接收偏置电压ve。

35.下面将该第一共模反馈电路301的工作过程进行介绍说明。

36.具体的,在一个工作周期t中,该第二晶体管m2的栅极可用于接收偏置电压ve,使得该第二晶体管m2中产生偏置电流,此时该第二晶体管m2为恒流源。该偏置电流通过第一晶体

管m1、第一电阻r1、第二电阻r2和第二晶体管m2后,使得该第一输出端输出第一共模电压v

c1

,该运算放大器op1接收该第一共模电压v

c1

,并将该第一共模电压v

c1

与该第一基准电压v

b1

进行比较后输出该第一反馈电压v

f1

,第一晶体管m1的栅极可用于接收该第一反馈电压v

f1

。该第一晶体管m1、该第一电阻r1、该第一共模电压v

c1

和该运算放大器op1构成了第一闭环负反馈回路。

37.其中,在设计电路时,可以设置偏置电压ve的数值,使得该偏置电流等于第一阈值,例如,在实际应用中,该第一阈值可以为350微安(μa)。

38.另外,在设计电路时,可以选择合适的电阻使得该第一电阻r1和该第二电阻r2之间第一共模电压v

c1

等于该第一基准电压v

b1

,比如,该第一基准电压v

b1

可以为1.25v。

39.在另一种可能的实施例中,如图4所示,该lvds发送器还包括:该第二共模反馈电路303,该第二共模反馈电路303的输入端与该第一共模反馈电路301的输出端耦合,该第二共模反馈电路303的输出端与该驱动电路302的第二输入端耦合;该第二共模反馈电路303包括:第二运算放大器op2、以及依次串联耦合在该(vdd)和该(gnd)之间的第五晶体管m5、第三电阻r3、第四电阻r4和第六晶体管m6;其中,该第三电阻r3和该第四电阻r4耦合于第二节点p2,该第二运算放大器op2的第一输入端耦合于该第二节点p2,该第二运算放大器op2的第二输入端用于接收第二基准电压v

b2

,该第二运算放大器op2的输出端与该第六晶体管m6的栅极和该第二共模反馈电路303的输出端耦合,该第五晶体管m5的栅极与该第二共模反馈电路303的输入端耦合。

40.下面将该第二共模反馈电路303具体的工作过程进行介绍说明。

41.具体的,在一个工作周期t中,第五晶体管m5的栅极可用于接收第一反馈电压v

f1

,使得第五晶体管m5和中产生偏置电流,该偏置电流通过第五晶体管m5、第六晶体管m6、第三电阻r3和第四电阻r4后,使得该第二节点p2处产生输出第三共模电压v

c3

,该第二运算放大器op2接收该第三共模电压v

c3

,并将该第三共模电压v

c3

与该第二基准电压v

b2

进行比较后输出该第二反馈电压v

f2

,该第六晶体管m6的栅极可用于接收该第二反馈电压v

f2

。该第六晶体管m6、该第四电阻r4、该第二共模电压v

c2

和该第二运算放大器op2构成了第二闭环负反馈回路。

42.需要说明的是,在设计电路时,可以选择合适的电阻使得该第三电阻r3和该第四电阻r4之间的第三共模电压v

c3

等于该第二基准电压v

b2

,比如,该第二基准电压v

b2

可以为1.25v。

43.下面将图3与图4中的驱动电路302进行介绍说明。

44.该驱动电路302包括:依次串联耦合在该(vdd)和该(gnd)之间的第三晶体管m3、差分电路02和第四晶体管m4;其中,该第三晶体管m3的栅极与该驱动电路302的第一输入端耦合,该差分电路02的差分输出端作为与该驱动电路302的差分输出端用于输出差分电压v1和v2;其中,差分电路02与该第三晶体管m3耦合于第三节点p3,该差分电路02与该第四晶体管m4耦合于第四节点p4,该驱动电路302还包括:第七晶体管m7、第八晶体管m8、第九晶体管m9和第十晶体管m

10

,该第七晶体管m7和该第八晶体管m8分别耦合于该第三节点p3和该差分输出端之间,该第九晶体管m9和该第十晶体管m

10

分别耦合于该差分输出端和该第四节点p4之间。

45.下面将该驱动电路302的工作过程进行说明。该驱动电路302在工作的过程中该第

五晶体管m3和第十晶体管m4均为电流源。在一个工作周期t中,该驱动电路302的工作过程可以包括两个阶段。

46.具体的,t1时刻,第一控制信号c1控制该第七晶体管m7和该第九晶体管m9导通,第二控制信号c2控制第八晶体管m8和该第十晶体管m

10

关断,该第一差分输出端和该第二差分输出端输出差分电压v

11

和v

12

。其中,该差分电压v

11

和v

12

的大小相同,相位相差180

°

,且此时v

11

为高电平,v

12

为低电平。

47.t2时刻,第一控制信号c1控制该第七晶体管m7和该第九晶体管m9关断,第二控制信号c2控制第八晶体管m8和该第十晶体管m

10

导通,该第一差分输出端和该第二差分输出端输出差分电压v

21

和v

22

。该差分电压v

11

和v

12

的大小相同,相位相差180

°

,且此时v

21

为高电平,v

22

为低电平。

48.其中,根据该差分电压确定第二共模电压的过程与现有技术相同,此处不再赘述。

49.进一步的,该第三晶体管m3的电流大于该第一晶体管m1的电流,且与该第一晶体管m1的电流之间存在线性关系。

50.进一步的,该第三晶体管m3的尺寸大于该第一晶体管m1的尺寸,该第四晶体管m4的尺寸大于该第十晶体管m

10

的尺寸,即该第三晶体管m3的尺寸比例大于该第一晶体管m1的尺寸比例,该第四晶体管m4的尺寸比例大于该第十晶体管m

10

的尺寸比例。

51.其中,尺寸比例为晶体管的宽度与长度的比值,例如,该第三晶体管m3的尺寸比例为该第三晶体管m3的宽度与该第三晶体管m3的长度的比值。在实际应用中该第三晶体管m3的尺寸比例可以为该第一晶体管m1尺寸比例的10倍。在该情境下,该第三晶体管m3和该第一晶体管m1共栅极连接时,该第三晶体管m3和该第一晶体管m1构成电流镜,即该第三晶体管m3中的电流与该第一晶体管m1中的电流呈倍数关系,该第三晶体管m3中的电流是该第一晶体管m1中的电流按照一定比例进行放大后的电流。

52.图4所示的lvds发送器在电路设计阶段,可以选择合适的电阻,使得驱动电路302中的第二共模电压v

c2

和第一共模反馈电路301中第一节点p1处的第一共模电压v

c1

,以及第二共模反馈电路303中第二节点p2处的第三共模电压v

c3

对应。即该驱动电路302中的第二共模电压v

c2

与第一共模反馈电路301中的第一共模电压v

c1

和第二共模反馈电路303中第二节点p2处的第三共模电压v

c3

的变化趋势相等,因此可以通过稳定第一共模反馈电路301中的第一共模电压v

c1

以及第二共模反馈电路303中第二节点p2处的第三共模电压v

c3

来稳定驱动电路302中的第二共模电压v

c2

。

53.在一种可能的实施例中,该lvds发送器包括第一共模反馈电路301和驱动电路302,此时,该lvds发送器的结构如图3所示,该第一共模反馈电路301根据该偏置电流(小电流)在第一节点p1处产生第一共模电压v

c1

,该第一运算放大器op1根据该第一共模电压v

c1

和第一基准电压v

b1

输出第一反馈电压v

f1

,该第一共模反馈电路301接收该第一反馈电压v

f1

,并通过该第一反馈电压v

f1

调节该第一共模电压v

c1

,以稳定了该第一共模电压v

c1

,由于该第一共模电压v

c1

与该第二共模电压v

c2

的变化趋势相同,从而稳定了该第二共模电压v

c2

,在此过程中该偏置电流为小电流,即该第一共模反馈电路301中的电流为小电流(实际应用中为350μa),与图1中lvds发送器(为了快速稳定驱动电路中的共模电压,必须增大驱动电路中的电流)相比,该第一共模反馈电路301中的电流小,因此该第一共模反馈电路301中的功耗小,从而在快速稳定该第二共模电压v

c2

的同时,降低了第一共模反馈电路301中的功耗;另

一方面,与图1中lvds发送器中的电阻(通常在kω量级以上)相比,该第一电阻r1和该第二电阻r1的阻值较小,通常为几百欧姆(ω),从而将该第一电阻r1和该第二电阻r1集成在芯片上时,占用芯片的面积小。

54.在另一种可能的实施例中,该lvds发送器包括驱动电路302和第二共模反馈电路303,此时,该lvds发送器的结构如图4所示的部分结构。该结构下的lvds发送器中第三晶体管m3的栅极用来接收偏置电压va,第三晶体管m3为电流源,第五晶体管m5的栅极用来接收偏置电压ve,该结构下的lvds发送器产生的有益效果与上述图3中的lvds发送器产生的有益效果类似,此处不再赘述。

55.在又一种可能的实施例中,该lvds发送器包括驱动电路302、第一共模反馈电路301和第二共模反馈电路303,此时,该lvds发送器的结构如图4所示,该lvds发送器通过第一共模反馈电路301和第二共模反馈电路303同时调节该驱动电路中的第二共模电压,在稳定该第二共模电压的同时,提升了该第二共模电压达到稳定时的速度。

56.需要说明的是,该第一共模电压v

c1

的调节过程与该第三共模电压v

c3

的调节过程类似,下面以第一共模电压v

c1

为例,对第一闭环负反馈回路调节该第一共模电压v

c1

的过程进行说明。

57.当该第一共模电压v

c1

升高时,该第一运算放大器op1输出的第一反馈电压v

f1

降低,该第一反馈电压v

f1

满足公式(1):

58.第一反馈电压v

f1

=(第一基准电压v

b1-第一共模电压v

c1

)

×

放大倍数

ꢀꢀꢀꢀ

(1)

59.由于第一晶体管m1的电流i与栅极电压和源极电压的差值成正比,该第一反馈电压v

f1

降低,流过第一晶体管m1的电流i不变,则第一晶体管m1的源极电压vs降低。由于第一共模电压v

c1

满足公式(2):

60.第一共模电压v

c1

=源极电压v

s-ir1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(2)

61.其中,由于电流i和第一电阻r1的阻值不变,当源极电压vs降低时,使得该第一共模电压v

c1

降低。

62.由上述调节过程可知,当该第一共模电压v

c1

升高时,通过第一闭环负反馈回路调节后,使得原来升高的第一共模电压v

c1

降低,从而实现稳定第一共模电压v

c1

的目的。

63.由于第一晶体管m1和该第三晶体管m3为共栅极连接,因此第一晶体管m1和该第三晶体管m3构成了线性电流镜,即该第三晶体管m3中的电流与该第一晶体管m1中的电流呈倍数关系,且流过该第三晶体管m3的电流满足公式(3):

[0064][0065]

其中,为第一晶体管m1中的电流,q1为该第三晶体管m3的尺寸比例,q2为第一晶体管m1的尺寸比例,q1满足公式(4),q2满足公式(5):

[0066][0067][0068]

为该第三晶体管m3的宽度,为该第三晶体管m3的长度,为第一晶体管m1的宽度,为第一晶体管m1的长度。在实际应用中该第三晶体管m3的尺寸比例可以为第

一晶体管m1的尺寸比例的10倍,即q1与q2的比值为10。当该第一晶体管m1中的电流为350μa时,由公式(3)可知该第三晶体管m3的电流为3.5毫安(ma)。因此,当该第一晶体管m1中的电流固定时,根据公式(3)可知第三晶体管m3中的电流也固定。同理可知,当该第六晶体管m6中的电流固定时,该第四晶体管m4中的电流也固定。

[0069]

当该第二共模电压升高时,该第一共模电压也升高,该第一运算放大器op1的输出电压降低,该第五晶体管m5的栅极电压降低,由于该第五晶体管m5中的电流为固定值,因此该第三晶体管m3的源极电压降低,从而该第二共模电压降低,即稳定了该第二共模电压。

[0070]

本技术实施例提供的lvds发送器,驱动电路的电流大于共模反馈电路的电流,且与共模反馈电路的电流之间存在线性关系,该共模反馈电路根据共模反馈电路的电流(小电流)产生第一共模电压,并根据该第一共模电压输出反馈电压,该驱动电路用于根据驱动电路的电流(大电流)产生差分电压并接收该反馈电压,该差分电压用于确定第二共模电压,该反馈电压用于调节该差分电压以稳定该第二共模电压,从而快速稳定该第二共模电压,与图1中串联两个电阻的lvds发送器(为了快速稳定驱动电路中的共模电压,必须增大驱动电路中的电流)相比,该共模反馈电路中的电流小,因此该共模反馈电路中的功耗小,从而在快速稳定该第二共模电压的同时,降低了共模反馈电路中的功耗。

[0071]

本技术实施例还提供一种芯片,该芯片包括lvds发送器,该lvds发送器可以包括图3或者图4所提供的lvds发送器。

[0072]

本技术实施例还提供一种lvds接口,该lvds接口可以包括图3或者图4所提供的lvds发送器。

[0073]

本技术实施例还提供一种终端设备,该终端设备包括输入\输出接口,该输入\输出接口可以包括图3或者图4所提供的lvds发送器。

[0074]

需要说明的是,关于lvds发送器的相关描述可以参见上文所提供的lvds发送器的相关描述,本技术实施例在此不再赘述。

[0075]

最后应说明的是:以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何在本技术揭露的技术范围内的变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1