一种CAN总线终端电阻的匹配挂载装置的制作方法

一种can总线终端电阻的匹配挂载装置

技术领域

1.本发明涉及can总线终端电阻匹配的技术领域,更具体地,涉及一种 can总线终端电阻的匹配挂载装置。

背景技术:

2.can总线是国际上应用最广泛的现场总线之一,can总线网络主要挂在 can_h和can_l之间,can_h和can_l电平的性质是不同的,can_h电平的两种逻辑状态为高电平状态和高阻状态,can_l的两种逻辑状态为低电平和高阻状态,而高阻状态的电平是不确定的,因此,在差分传输的can总线中,匹配终端电阻一方面能降低can_h与can_l回路中阻抗的作用,使canh和 canl具有确定的电平,另一方面,终端电阻吸收信号反射及回波,避免反射波对原信号产生干扰。

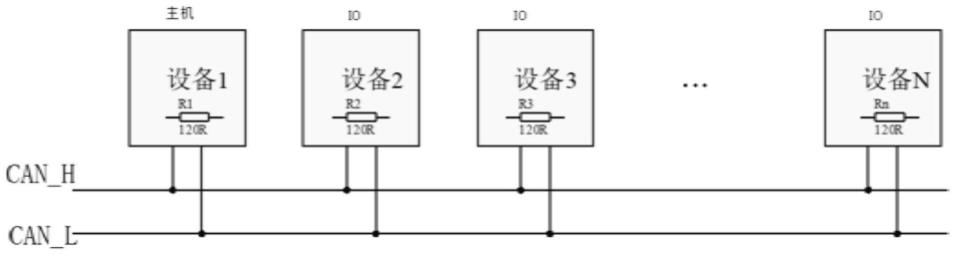

3.如图1所示,can总线的终端电阻配置于can_h和can_l之间,一般仅能通过硬件焊接来实现,而改变仅能通过拆除来实现,若涉及到多个io模块组网时,需要硬性拆除外壳,并用电烙铁去掉多余的终端电阻,容易发生终端电阻错配现象,而一旦发生终端电阻错配现象,将引起can总线出现大量的通讯故障,影响其正常通讯,为克服这种缺陷,现有技术中公开了一种自动匹配can 总线终端电阻的装置,通过控制单元和收发器的配合计算接入can总线的终端电阻的电阻最优值,并且不需要焊接与拆卸操作,省时省力,但该装置主要侧重于终端电阻值的选取,面向can总线主机与io模块组网时的终端电阻匹配挂载问题时,无法灵活处理。

技术实现要素:

4.为解决can总线主机和io模块组网时的终端电阻匹配挂载的问题,本发明提出一种can总线终端电阻的匹配挂载装置,在can总线设备主机和 io模块组网时,保证了终端电阻的快捷匹配挂载,操作简单方便。

5.为解决上述技术问题,本发明的技术方案如下:

6.一种can总线终端电阻的匹配挂载装置,包括:第一对外连接器p1、接入 can总线的主机、若干个接入can总线的终端电阻、第二对外连接器p2、自主机沿can总线依次接入can总线的若干个io设备、电压源单元、中央控制器单元及继电器,所述第一对外连器p1设有第一引脚与第二引脚,第一引脚连接can总线的高位线can1_h,第二引脚连接can总线的低位线can1_l;第二对外连接器p2设有第三引脚、第四引脚、第五引脚及第六引脚;第三引脚分别连接can总线的高位线can1_h及继电器触点的第一端,第四引脚分别连接can总线的低位线can1_l及继电器触点的第二端,终端电阻的两端分别连接can总线的高位线can1_h与低位线can1_l;第五引脚分别连接电压源单元及中央控制器单元的输入端,中央控制器单元的输出端输出高或低电平,控制继电器的通断;第一引脚与第二引脚短接,主机的终端电阻挂载接入,第五引脚与第六引脚悬空,io设备的终端电阻不挂载接入,第五引脚与第六引脚短接, io设备的终端电阻挂载接入。

7.在本技术方案中,对于设置于can总线上的io设备与主机,考虑io设备与主机组网时的终端电阻匹配需求,提出利用第一对外连器p1、第二对外连接器p2以及中央控制器单元之间的配合,实现终端电阻的匹配挂载,将第一对外连器p1的第一引脚与第二引脚短接,can总线的高位线can1_h与can总线的低位线can1_l之间挂载接入终端电阻,将第二对外连接器p2的第五引脚与第六引脚悬空,中央控制器单元自动采集到第五引脚的高电平输入,而输出低电平,继电器的触点在低电平的作用下,对应常闭触点断开,第一端与第二端不闭合,终端电阻不接入can总线,将第二对外连接器p2的第五引脚与第六引脚短接,中央控制器单元自动采集到第五引脚的低电平输入,而输出高电平,继电器的触点在高电平的作用下,对应常闭触点不动作,第一端与第二端闭合,终端电阻接入can总线,保证了终端电阻的快捷匹配挂载,操作简单方便。

8.优选地,与第一引脚连接的can总线的高位线can1_h上接入有终端电阻 r1a,终端电阻r1a的最大值为128ω,最小值为116ω,标称值为120ω,与第二引脚连接的can总线的低位线can1_l上接入有终端电阻r2a,阻值为0 ω。

9.优选地,第一引脚与第二引脚短接,can总线的高位线can1_h与can 总线的低位线can1_l之间接入终端电阻r1a与终端电阻r2a。

10.在此,将第一对外连器p1的第一引脚与第二引脚短接,can总线的高位线 can1_h与can总线的低位线can1_l之间挂载接入终端电阻,第一对外连器p1的两个引脚采用外部布线选择,通过短接与否实现在单主机接入时的终端电阻接入与否,简单方便。

11.优选地,与第三引脚连接的can总线的高位线can1_h上接入有终端电阻 r3a,阻值为0ω,第三引脚与继电器触点的第一端连接的线路上接入有电阻r5,电阻r5最大值为128ω,最小值为116ω,标称值为120ω。

12.优选地,与第四引脚连接的can总线的低位线can1_l上接入有终端电阻 r4a,阻值为0ω。

13.优选地,所述电压源单元包括电阻r6及电源vcc1,第五引脚连接电阻r6,电阻r6连接电源vcc1,第六引脚接地。

14.优选地,所述中央控制器单元包括与门模块、电阻r7、光耦合器、电阻r8 及中央处理器cpu,所述与门模块上设有引脚b、引脚a、接地引脚、电源引脚及引脚y,第五引脚分别连接与门模块的引脚b与引脚a,接地引脚接地,电源引脚连接电源vcc1,电源vcc1连接电阻r7的一端,电阻r7的另一端与引脚y分别连接光耦光耦合器的第一输入端和第二输入端,所述光耦合器的输出端为光敏三极管,光敏三极管的集电极分别连接电阻r8的一端与中央处理器 cpu的输入端,光敏三极管的发射极接地,电阻r8的另一端连接3.3v电压源,中央处理器cpu的输出端连接继电器的一端,继电器的另一端连接电源vcc1。

15.优选地,所述中央处理器cpu为stm32微机控制器。stm32微机控制器自身的芯片电路本身具有输入采集与输出功能。

16.优选地,所述继电器的触点还包括悬空端,第二对外连接器p2的第五引脚与第六引脚悬空时,stm32微机控制器采集到第五引脚输入的高电平,stm32 微机控制器输出低电平,继电器触点的第一端与第二端不闭合,第一端与悬空端连接,电阻r5不接入,io设备的终端电阻不挂载接入can总线。

17.优选地,第二对外连接器p2的第五引脚与第六引脚短接时,stm32微机控制器采集

到第五引脚输入的低电平,stm32微机控制器输出高电平,继电器触点的第一端与第二端闭合,电阻r5接入,io设备的终端电阻挂载接入can总线。

18.与现有技术相比,本发明技术方案的有益效果是:

19.本发明提出一种can总线终端电阻的匹配挂载装置,利用第一对外连器p1、第二对外连接器p2以及中央控制器单元之间的配合,实现终端电阻的匹配挂载,将第一对外连器p1的第一引脚与第二引脚短接,can总线的高位线 can1_h与can总线的低位线can1_l之间挂载接入终端电阻,将第二对外连接器p2的第五引脚与第六引脚悬空,中央控制器单元自动采集到第五引脚的高电平输入,而输出低电平,继电器的触点在低电平的作用下,第一端与第二端不闭合,终端电阻不接入can总线,将第二对外连接器p2的第五引脚与第六引脚短接,中央控制器单元自动采集到第五引脚的低电平输入,而输出高电平,继电器的触点在高电平的作用下,第一端与第二端闭合,终端电阻接入can总线,保证了终端电阻的快捷匹配挂载,操作简单方便。

附图说明

20.图1表示本发明背景技术中提出的can总线的终端电阻配置于can_h和 can_l之间示意图;

21.图2表示本发明实施例1中提出的主机和多个io设备组网形成的can网络;

22.图3表示本发明实施例1中提出的can总线终端电阻的匹配挂载装置的电路结构图;

23.其中,1-电压源单元;2-中央控制器单元。

具体实施方式

24.附图仅用于示例性说明,不能理解为对本专利的限制;

25.为了更好说明本实施例,附图某些部件会有省略、放大或缩小,并不代表实际产品的尺寸;

26.对于本领域技术人员来说,附图中某些公知结构及其说明可能省略是可以理解的。

27.下面结合附图和实施例对本发明的技术方案做进一步的说明。

28.实施例1

29.图2所示的can网络中,框线内表示终端电阻,常规对于终端电阻的挂载接入或断开时,一般采用焊接或拆卸的方式,十分不灵活,为解决当前无法灵活处理can总线主机与io模块组网时的终端电阻匹配挂载问题,本实施例提出一种can总线终端电阻的匹配挂载装置,该装置的电路结构图如图3所示,参见图3,装置包括:第一对外连接器p1、接入can总线的主机(直观的主机接入可参见图1)、若干个接入can总线的终端电阻、第二对外连接器p2、自主机沿can总线依次接入can总线的若干个io设备(直观的io设备接入示意可参见图1)、电压源单元1、中央控制器单元2及继电器,参见图3,接入can 总线的终端电阻有r1a、r2a、r3a、r4a、r5,终端电阻的两端分别连接can 总线的高位线can1_h与低位线can1_l,但对于设置于can总线上的io设备与主机,要根据io设备与主机组网时的终端电阻匹配需求,实现r1a、r2a、 r3a、r4a、r5的合理挂载接入。

30.参见图3,第一对外连器p1设有第一引脚与第二引脚,第一引脚与第二引脚在图3的第一对外连接器p1中分别对应标记“1”和标记“2”,第一引脚连接 can总线的高位线can1_h,第二引脚连接can总线的低位线can1_l,在高位线can1_h上设置有与第一引脚连接的电阻r1a,在低位线can1_l上设置有与第二引脚连接的电阻r2a;can总线继续延伸,依次设有中间io设备与末端io设备;第二对外连接器p2设有第三引脚、第四引脚、第五引脚及第六引脚;其中,在图3中,第二对外连接器p2的第三引脚、第四引脚、第五引脚及第六引脚对应第二对外连接器p2的“1”、“2”、“3”、“4”标记,第三引脚分别连接 can总线的高位线can1_h及继电器触点的第一端,第一端用“9”标记,第四引脚分别连接can总线的低位线can1_l及继电器触点的第二端,第二端用“10”标记;第五引脚分别连接电压源单元1及中央控制器单元2的输入端,中央控制器单元2的输出端输出高或低电平,控制继电器的通断;

31.整体上:第一引脚与第二引脚短接,主机的终端电阻挂载接入,第五引脚与第六引脚悬空,io设备的终端电阻不挂载接入,第五引脚与第六引脚短接,io 设备的终端电阻挂载接入。将第一对外连器p1的第一引脚与第二引脚短接,can 总线的高位线can1_h与can总线的低位线can1_l之间挂载接入终端电阻,将第二对外连接器p2的第五引脚与第六引脚悬空,中央控制器单元自动采集到第五引脚的高电平输入,而输出低电平,继电器的触点在低电平的作用下,第一端与第二端不闭合,终端电阻不接入can总线,将第二对外连接器p2的第五引脚与第六引脚短接,中央控制器单元自动采集到第五引脚的低电平输入,而输出高电平,继电器的触点在高电平的作用下,第一端与第二端闭合,终端电阻接入can总线,保证了终端电阻的快捷匹配挂载,操作简单方便。

32.对于终端电阻r1a,接于第一引脚连接的can总线的高位线can1_h上,终端电阻r1a的最大值为128ω,最小值为116ω,标称值为120ω,在本实施例中,r1a为120ω,与第二引脚连接的can总线的低位线can1_l上接入有终端电阻r2a,阻值为0ω,第一引脚与第二引脚短接,can总线的高位线 can1_h与can总线的低位线can1_l之间接入终端电阻r1a与终端电阻r2a。即将第一对外连器p1的第一引脚与第二引脚短接,can总线的高位线can1_h 与can总线的低位线can1_l之间挂载接入终端电阻,第一对外连器p1的两个引脚采用外部布线选择,通过短接与否实现在单主机接入时的终端电阻接入与否,简单方便。

33.在本实施例中,与第三引脚连接的can总线的高位线can1_h上接入有终端电阻r3a,阻值为0ω,第三引脚与继电器触点的第一端“9”连接的线路上接入有电阻r5,电阻r5最大值为128ω,最小值为116ω,标称值为120ω,电阻r5取120ω,与第四引脚连接的can总线的低位线can1_l上接入有终端电阻r4a,阻值为0ω。

34.参见图3,电压源单元1包括电阻r6及电源vcc1,第五引脚连接电阻r6,电阻r6连接电源vcc1,第六引脚接地,电阻r6作为接入电阻使用。

35.中央控制器单元2包括与门模块、电阻r7、光耦合器、电阻r8及中央处理器cpu,与门模块上设有引脚b、引脚a、接地引脚、电源引脚及引脚y,第五引脚分别连接与门模块的引脚b与引脚a,接地引脚接地,电源引脚连接电源 vcc1,电源vcc1连接电阻r7的一端,电阻r7的另一端与引脚y分别连接光耦光耦合器的第一输入端和第二输入端,所述光耦合器的输出端为光敏三极管,光敏三极管的集电极分别连接电阻r8的一端与中央处理器cpu的输入端,光敏三极管的发射极接地,电阻r8的另一端连接3.3v电压源,中央处理器cpu的输出端连接继电器的一端,继电器的另一端连接电源vcc1。在本实施例中,所述中央处理器cpu为

stm32微机控制器,stm32微机控制器自身的芯片电路本身具有输入采集与输出功能。

36.参见图3,继电器的触点还包括悬空端,在图3中,触点用k1表示,悬空端如图3中k1“3”和“5”对应的端,第二对外连接器p2的第五引脚与第六引脚悬空时,stm32微机控制器采集到第五引脚输入的高电平,stm32微机控制器输出低电平,继电器触点的第一端与第二端不闭合,第一端与悬空端连接,电阻r5不接入,io设备的终端电阻不挂载接入can总线。这里对于stm32微机控制器高、低电平的输入以及采集、输出,是其本身的芯片电路自有的输入输出功能实现。

37.同理,第二对外连接器p2的第五引脚与第六引脚短接时,stm32微机控制器采集到第五引脚输入的低电平,stm32微机控制器输出高电平,继电器触点的第一端与第二端闭合,电阻r5接入,io设备的终端电阻挂载接入can总线。

38.实施例2

39.基于图3所示的电路结构图,下面从单主机和单个io设备组网方面进行说明,主机是can网络首端,利用第一对外连接器p1、采用外部布线选择,第一对外连接器p1的第一引脚和第二引脚短接,can总线的高位线can1_h与can 总线的低位线can1_l之间接入终端电阻r1a与终端电阻r2a,r1a为120ω,终端电阻r2a为0ω,主机挂载接入120ω终端电阻;而第一引脚和第二引脚不短接时,120ω的终端电阻将不挂载接入。

40.io设备通过第二对外连接器p2的引脚在外的布线插头选择是否挂终端电阻,将第二对外连接器p2的第五引脚和第六引脚短接,第五引脚输入低电平,中央处理器cpu采集到第五引脚输入的低电平,通过自身设置,中央处理器cpu输出高电平,继电器触点的第一端“9”与第二端“10”闭合,电阻r5接入can 总线,实现了io设备的终端电阻挂载接入can总线;

41.将第二对外连接器p2的第五引脚和第六引脚悬空,第五引脚输入高电平,中央处理器cpu采集到第五引脚输入的低电平,通过自身设置,中央处理器cpu 输出低电平,继电器触点的第一端“9”与第二端“10”断开,第一端与悬空端连接,电阻r5断开,io设备的终端电阻不挂载接入can总线。

42.以上过程不需要拆卸或者焊接,仅通过第一对外连接器p1和第二对外连接器p2的外接布线配合,即可实现终端电阻的挂载。

43.实施例3

44.基于图3所示的电路结构图,下面从单主机和多个io设备组网方面进行说明,主机是can网络首端,利用第一对外连接器p1、采用外部布线选择,第一对外连接器p1的第一引脚和第二引脚短接,can总线的高位线can1_h与can 总线的低位线can1_l之间接入终端电阻r1a与终端电阻r2a,r1a为120ω,终端电阻r2a为0ω,主机挂载接入120ω终端电阻;而第一引脚和第二引脚不短接时,120ω的终端电阻将不挂载接入。

45.中间io设备通过第二对外连接器p2的引脚在外的布线插头选择是否挂终端电阻,第二对外连接器p2的第五引脚和第六引脚悬空,第五引脚输入高电平,中央处理器cpu采集到第五引脚输入的低电平,通过自身设置,中央处理器cpu 输出低电平,继电器触点的第一端“9”与第二端“10”断开,第一端与悬空端连接,电阻r5断开,io设备的终端电阻不挂载接入can总线。

46.末端io设备通过第二对外连接器p2的第五引脚和第六引脚短接,第五引脚输入低电平,中央处理器cpu采集到第五引脚输入的低电平,通过自身设置,中央处理器cpu输出高

电平,继电器触点的第一端“9”与第二端“10”闭合,电阻r5接入can总线,实现了io设备的终端电阻挂载接入can总线;

47.以上过程不需要拆卸或者焊接,仅通过第一对外连接器p1和第二对外连接器p2的外接布线配合,即可实现终端电阻的挂载。

48.显然,本发明的上述实施例仅仅是为清楚地说明本发明所作的举例,而并非是对本发明的实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明权利要求的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1