一种基于FPGA的测控装置的制作方法

一种基于fpga的测控装置

技术领域

1.本发明属于智能变电站技术领域,具体涉及一种基于fpga的测控装置。

背景技术:

2.目前国产处理器及fpga芯片在性能指标、接口集成度以及可靠性方面与进口器件存在差距,缺少长时间运行经验,单一的处理器实现方式存在一定的性能瓶颈,通过fpga与cpu集成设计,可以提升整体处理性能,但存在相互交互传输瓶颈问题;另一方面国产fpga逻辑电路异常容易导致数据错误,如何避免国产器件性能差距对于装置动作行为的影响也是亟待解决的问题。

技术实现要素:

3.为解决现有技术中的不足,本发明提供一种基于fpga的测控装置,在fpga模块与cpu模块之间设计多种数据总线链路,对不同性质数据进行分类传输,必要时多总线可互相冗余协作运行,优化提升总线利用率。

4.为达到上述目的,本发明所采用的技术方案如下:一种基于fpga的测控装置,包括cpu模块、fpga模块和adc转换回路,fpga模块设置有第二spi接口和扩展网络接口;fpga模块通过扩展网络接口实现过程层sv数字采样值报文接收及goose报文收发、站控层mms报文收发;fpga模块通过第二spi接口与adc转换回路进行通信连接,实时采集adc模拟采样数据;cpu模块与fpga模块之间通过第一spi接口、sdio接口、高速千兆以太网通信接口通信连接,第一spi接口和/或sdio接口用于cpu模块读写fpga模块内部寄存器、irig-b时间信息,将fpga模块配置管理信息传输给fpga模块,以及获取fpga模块的状态信息;高速千兆以太网通信接口用于cpu模块与fpga模块之间的过程层sv数字采样值报文及goose报文、站控层mms报文,以及adc模拟采样数据的输入输出传递。

5.进一步地,所述扩展网络接口还支持goose报文和mms报文共网传输,支持goose报文风暴抑制及mms报文广播订阅、广播抑制功能。

6.进一步地,所述fpga模块包括多个独立的采样和插值回路,通过第二spi接口接收的adc模拟采样数据、通过网络扩展接口接收的sv数字采样数据分别采用独立的采样和插值回路进行处理,fpga模块对每个采样和插值回路的采样数据全流程增加crc校验,对插值后的数据进行完整性校验,若通过完整性校验,对整包采样值数据增加crc校验,并通过高速千兆以太网通信接口转发给cpu模块。

7.进一步地, 所述fpga模块还用于对器件内部关键ip核与寄存器状态进行自校验,若监测到fpga模块内部存在软故障,将发出告警信号并进行闭锁控制操作。

8.进一步地,所述的一种基于fpga的测控装置,还包括看门狗复位回路,所述看门狗复位回路用于对cpu模块的运行进行监视,若看门狗复位回路在设定时间内未收到cpu模块打狗信号,则看门狗复位动作,对cpu模块进行复位重启处理。

9.进一步地,所述的一种基于fpga的测控装置,还包括电压监视回路,所述电压监视回路用于对系统工作电源进行监视,采集监视数据通过ic接口传送给cpu模块,若电压超出工作限值范围,cpu模块发出告警信号。

10.进一步地,所述fpga模块还设置有can总线接口,用于与开入开出模件进行通信。

11.进一步地,所述fpga模块还设置有hcb总线接口,用于非实时多个cpu模块之间的快速通信。

12.进一步地,所述fpga模块还设置有hsb总线接口,用于多个cpu模块之间实时大数据量的交互。

13.进一步地,所述fpga模块还设置有通用的io接口,用于故障及告警接点等信号的输入输出。

14.与现有技术相比,本发明所达到的有益效果:本发明通过在fpga模块与cpu模块之间设计多种数据总线链路,支持应用针对不同性质数据进行分类传输,必要时多总线可互相冗余协作运行,解决不同性质的数据共用单一总线存在的相互干扰影响问题,降低软件设计适应的复杂度,整体上提升装置运行数据交互效率,同时通过基于fpga芯片设计端到端数据全路径逐级校验机制,保证了数据转换可靠传输。

附图说明

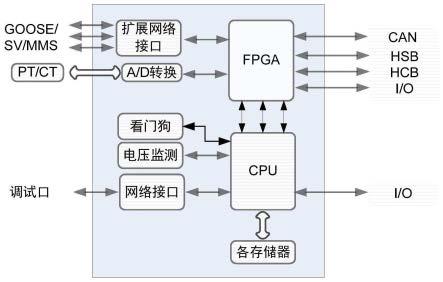

15.图1是本发明实施例提供的基于fpga的测控装置组成示意图;图2是本发明实施例提供的fpga模块与cpu模块交互校验交互流程示意图。

具体实施方式

16.下面结合具体实施例对本发明作进一步描述。以下实施例仅用于更加清楚地说明本发明的技术方案,而不能以此来限制本发明的保护范围。

17.如图1所示,一种基于fpga的测控装置,包括主处理器cpu模块、fpga模块、看门狗复位回路、存储器、电压监测回路和adc(analog-to-digital converter)转换回路。

18.其中主处理器cpu模块主要承担测控应用功能逻辑任务处理,通过fpga模块接受数据源,经过运算逻辑处理后,将处理结果数据通过内部总线传输给fpga模块发送至目标端口。adc转换回路主要用于实现模拟信号的采集及信号转换。

19.fpga模块内部资源丰富,具有高性能的 dsp (数字信号处理,digital signal processing)资源,高速 lvds 接口以及丰富的 bram 存储器资源,通过fpga逻辑可编程设计可支持实现各种应用功能的预处理,例如:模拟量采集及数据预处理功能;数字化iec61850-9-2(sv,sampled value)采样值报文及收发预处理;过程层goose报文收发功能及goose风暴抑制功能;实现can总线扩展设计,用于与开入开出模件(dio模件)的通信;实现hcb总线设计,用于非实时多cpu之间的快速通信;实现装置内部高速总线hsb设计,用于多cpu之间实时大数据量的交互;实现内部irig-b对时总线扩展设计,用于装置内部对时及守时功能;实现以太网接口扩展设计,支持站控层mms通信;完成与cpu之间通信接口spi及sdio设计;支持与cpu之间千兆以太网通信接口设计。

20.fpga通过自身逻辑可编程实现独立的spi接口及网络接口扩展。具体的,如图1和2

所示,fpga模块设置有第二spi接口(spi2)和扩展网络接口,扩展网络接口可以是例如rmi接口。

21.扩展网络接口主要实现主处理器cpu模块及fpga扩展网络输入输出电平转换,站控层mms、过程层goose、sv数据都通过网络扩展接口进行通信。更具体的,fpga模块通过扩展网络接口实现过程层sv采样值报文接收及goose报文的收发,以及站控层mms报文的收发。第二spi接口用于接入模拟采样(adc)转换数据,fpga模块通过第二spi接口与adc转换回路进行通信连接,实时采集adc转换的采样数据。

22.如图2所示,fpga与核心处理器cpu之间的通信接口包括低速总线第一spi通信接口(spi1)、低速总线sdio通信接口和高速千兆以太网通信接口(rgmii)。

23.其中,第一spi接口和/或sdio接口主要用于cpu模块读写fpga模块内部寄存器、irig-b时间信息,将fpga模块配置管理信息传输给fpga模块。cpu通过第一spi接口或sdio接口还可以获取fpga的告警、启动、呼唤等状态信息。其中,第一spi接口和sdio接口可相互冗余。

24.高速千兆以太网通信接口主要用于cpu模块与fpga模块之间数据的输入输出传递,包括过程层sv采样值报文及goose报文的收发、站控层mms通信报文收发,以及adc模拟采样数据的传输。高速千兆以太网通信接口解决了cpu接收fpga外部扩展网络接口数据转发传输的瓶颈问题。

25.其中,扩展网络接口支持goose报文和mms报文共网(共享物理端口)传输,支持goose报文风暴抑制及mms报文广播订阅、广播抑制等功能。

26.fpga模块还设置有can总线接口、hcb总线接口、hsb总线接口和io接口。其中,can总线接口用于与开入开出模件进行通信,hcb总线接口用于非实时多cpu模块之间的快速通信,hsb总线接口用于多cpu模块之间实时大数据量的交互,io接口用于故障及告警接点等信号的输入输出。

27.看门狗复位回路实现对主处理器cpu模块的运行监视,当看门狗复位回路在设定时间内未收到主处理器cpu打狗信号,看门狗复位动作,对主处理器cpu模块进行复位重启处理。

28.存储器主要包括运行内存空间、数据及程序存储flash。

29.电压监视回路实现对系统工作电源的监视,采集监视数据通过ic接口传送给主处理器cpu模块,当电压超出工作限值范围时,cpu将发出告警信号。

30.考虑到针对fpga的可靠性验证,本发明基于fpga芯片逻辑可编程内部设计了从源端fpga数据采集到cpu数据全路径逐级校验机制,以保证数据转换可靠传输。

31.如图2所示,fpga模块内部使用了多个独立的采样和插值回路,通过第二spi接口接收的adc模拟采样数据、通过网络扩展接口接收的sv数字采样数据分别采用独立的采样和插值回路进行处理,fpga模块对每个采样和插值回路的采样数据全流程增加crc校验,以在数据交互过程中实时监视采样数据在fpga内部存储和逻辑运算过程中的正确性。

32.fpga模块对插值后的数据进行完整性校验,若通过完整性校验,再对整包采样值数据增加crc校验,并通过高速千兆以太网通信接口转发给cpu模块。

33.fpga通过对采样数据附加 crc校验,可以有效监视采样值数据在fpga内部经过bram存储以及逻辑运算的正确性,当监测到数据异常时,fpga将采样数据品质设置为无效

状态标。

34.此外,fpga还基于探针技术对器件内部关键ip核与寄存器状态的自校验,当监测到fpga内部存在软故障,则发出告警信号并进行闭锁控制操作,避免了器件性能差距对于装置动作行为的影响,提高了装置整体可靠性。

35.本发明通过在fpga模块与cpu模块之间设计多种数据总线链路,支持应用针对不同性质数据进行分类传输,必要时多总线可互相冗余协作运行,解决不同性质的数据共用单一总线存在的相互干扰影响问题,降低软件设计适应的复杂度,整体上提升装置运行数据交互效率,同时通过基于fpga芯片设计端到端数据全路径逐级校验机制,保证了数据转换可靠传输。

36.以上已以较佳实施例公布了本发明,然其并非用以限制本发明,凡采取等同替换或等效变换的方案所获得的技术方案,均落在本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1