一种国产化DSP嵌入式系统及其功能载荷重构方法与流程

本发明涉及计算机和信息技术高速数字信号处理,特别是一种国产化dsp嵌入式系统及其功能载荷重构方法。

背景技术:

1、数字信号处理器(dsp)所具有的系统构成灵活、可编程、使用面广的特点,使其在通信、航空航天、医疗仪器、工业控制及信息家电中成为不可或缺的信息处理计算引擎。随着电子技术的发展和用户需求的提升,对于已投入使用的电子信息类设备dsp嵌入式系统的功能升级也越来越频繁,尤其是以信号处理为主的设备。而传统的升级方法是实地取下设备,通过jtag仿真器烧写dsp嵌入式系统外挂的flash中程序来实现功能载荷重构。这种方法简单有效,但对于某些特殊场合,如设备在密闭的箱体内、设备在远端以及其它不便触及的地方,传统的方法给功能载荷重构带来了极大的不便。并且由于烧写dsp嵌入式系统外部的flash时间很长,通常需要数分钟时间完成,该方式无法满足时敏设备的快速功能载荷重构要求。

2、国内越来越多的公司采用了国产化芯片设计相关设备。因此,研究快速、高效、便捷的针对国产化dsp嵌入式系统功能载荷技重构技术成为一种迫切的需求。

3、专利申请号为2022104877892的一种基于异构可重构的动态资源调度方法及系统,该发明是基于fpga、dsp和arm架构下提出了一种动态资源调度框架。通过主控arm能够方便地管理不同架构下的资源,实现任务的交替,具有普遍适用性。但该发明并未对国产化dsp嵌入式系统功能载荷的在线重构方法进行详细论述,并且其整个资源调度的核心是主控arm芯片并非dsp芯片嵌入式系统,其异构可重构主要体现在硬件资源的动态调度并非dsp嵌入式系统中的功能载荷重构。

4、专利申请号为2017114585387的一种基于dsp的动态加载方法,包括elf文件预处理、elf文件读取与解析、符号导出、符号重定位和运行模块。该发明主要是基于进口dsp芯片所用的ccs编译器实现dsp动态加载的方法解决了b14切换问题,提高可重定位代码执行效率。该发明主要适用于进口dsp芯片tms320c6678,并未对国产化dsp嵌入式系统功能载荷的在线重构方法进行详细论述,并且其整个动态加载方法是基于dsp芯片的仿真器在ccs编译器环境中实现,并非基于网络和dsp芯片的外围存储资源控制方法,无法实现远距离快速功能载荷重构。

技术实现思路

1、本发明公开了一种国产化dsp嵌入式系统及其功能载荷重构方法,通过以太网口、控制芯片以及dsp芯片等,实现远距离、实时在线、快速功能载荷重构方法。

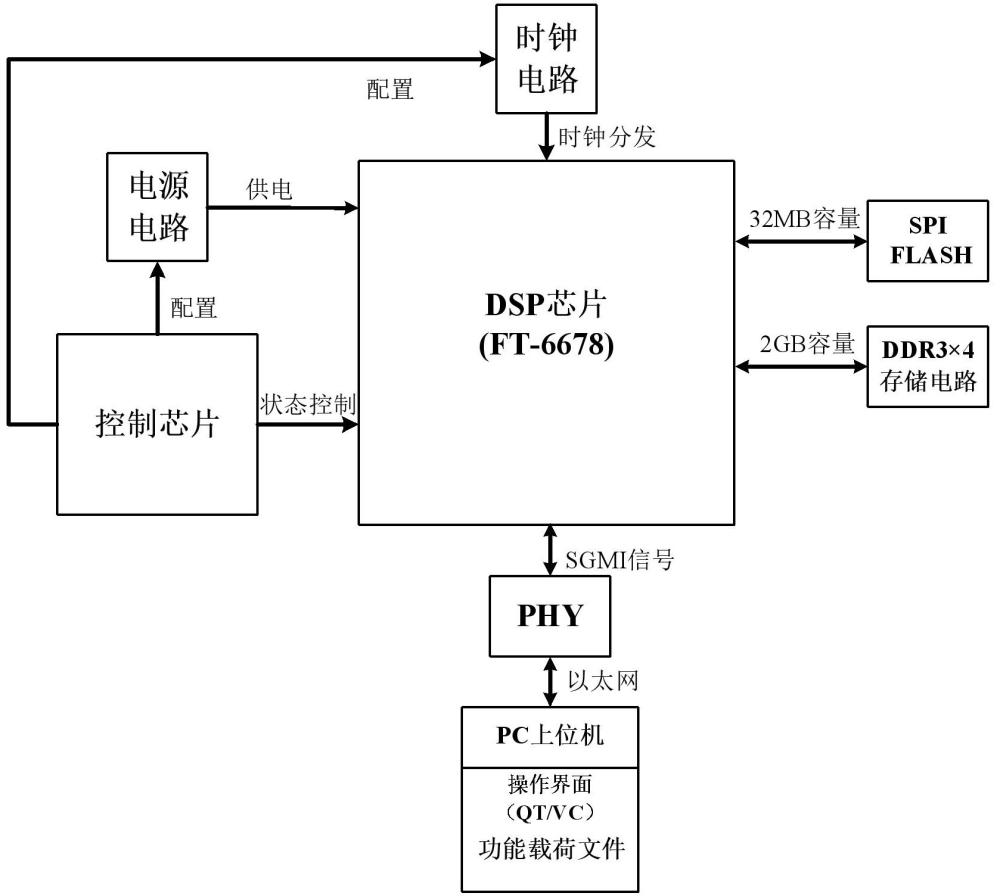

2、本发明公开了一种国产化dsp嵌入式系统,其由控制芯片、pc上位机、phy芯片、dsp芯片及其外围电路组成;

3、控制芯片主要完成对整个系统的全局复位、外围电路的配置以及dsp芯片启动模式控制,使整个系统正常运行;

4、控制芯片与dsp芯片连接,使dsp芯片正常上电并顺利启动;

5、pc上位机与phy芯片通过以太网进行互联,将存放的功能载荷文件,通过以太网络发送至dsp芯片,实现功能载荷库与dsp芯片的紧耦合和无缝连接和功能载荷重构;其中,dsp芯片为可重构功能实现的主体芯片。

6、进一步地,dsp芯片的外围电路包括时钟电路、电源电路、存储电路以及spi flash电路;

7、dsp芯片为嵌入式系统的核心芯片,分别与时钟电路、电源电路、spi flash、存储电路以及phy芯片连接;控制芯片分别连接电源电路、时钟电路和dsp芯片,通过其控制电源的启动时序、时钟以及dsp芯片的启动模式状态管脚,使dsp芯片正常上电并顺利启动。

8、进一步地,时钟电路连接dsp芯片,为dsp芯片提供内核以及高速口参考时钟;电源电路为dsp嵌入式系统提供供电电压;dsp芯片外接的spi flash用于存储烧写文件;dsp芯片外接的存储电路用于存放和读写数据以及载荷文件;dsp芯片外接的phy芯片用于实现sgmii信号传输,sgmii信号与mdi信号的转换,以实现pc上位机与dsp芯片的通信;pc上位机与phy芯片通过以太网络相连接,上位机软件将存放的功能载荷文件,通过以太网络发送至dsp芯片,通过控制芯片的控制,实现功能载荷重构。

9、本发明还公开了一种基于上述任一项所述的国产化dsp嵌入式系统的功能载荷重构方法,其包括:

10、步骤1:pc上位机将加载指令和加载文件发送到dsp芯片;dsp芯片接收到加载指令和加载文件后,将其搬移至网络协议栈缓冲区;

11、步骤2:若需加载的核为主核,将主核跳转至二级启动程序运行,若需要加载的核为从核,则通过主核将其先进行复位并重启;

12、步骤3:若加载的核为主核,需要使用跳转功能的函数使其跳转至新加载的程序处;加载成功则函数返回指示成功的值并顺利跳转运行新加载的程序,加载失败则函数返回指示失败的值并重新执行主核加载过程;

13、步骤4:dsp芯片的主核将加载结果回传至pc上位机,完成dsp芯片的功能载荷重构。

14、进一步地,所述步骤1之前,还包括:

15、启动系统后,由控制芯片给电源电路启动时序以及dsp芯片的启动状态,使dsp芯片正常上电启动,同时控制时钟电路给dsp芯片以及外围电路分配工作时钟;dsp芯片正常运行后,启动应用程序的网络指令接收线程和数据接收线程,网络指令接收线程和数据接收线程持续监听来自pc上位机的网络加载指令。

16、进一步地,所述步骤1包括:

17、pc上位机将加载指令和加载文件通过以太网发送到dsp芯片;加载指令包括需要加载的核号、载荷大小以及载荷bin文件。

18、进一步地,所述步骤1包括:

19、dsp芯片接收到加载指令和加载文件后,通过芯片内部直接存储器存取dma数据搬移器将其搬移至网络协议栈缓冲区,缓冲区首先接收pc上位机的加载指令并识别指令中的内容,提取需要加载的核号和加载文件大小,然后接收来自pc上位机的加载文件并将其通过内存拷贝memcopy的方式存放至用户事先自定义分配好的地址。

20、进一步地,所述步骤2之后,所述步骤3之前,还包括:

21、在网络数据接收线程中,dsp芯片将存放在存储电路中的加载文件数据搬移至需要加载的核对应的跳转地址,该跳转地址是在编译生成载荷文件时生成,将其从载荷文件读出并赋值即可。

22、进一步地,所述步骤3还包括:

23、若加载的核为从核时,则需要将核对应跳转的地址的值写入其在二级高速缓冲存储器上的指定地址,完成后会自动跳转至新的程序,若成功运行会向主核发送ipc中断通知其结果,若主核在规定时间内成功收到ipc中断则代表从核加载成功,若未收到ipc中断则代表从核加载失败并并重新执行从核加载过程。

24、进一步地,所述步骤4包括:

25、dsp芯片的主核将加载结果通过以太网网络回传至pc上位机,完成dsp芯片的功能载荷重构。

26、由于采用了上述技术方案,本发明具有如下的优点:

27、1.可解决目前国产化信号处理设备无法远程、实时在线、快速重构任务系统功能的难题。

28、2.本发明的嵌入式系统具备强大的数字信号处理性能,其中定点运算性能为32gmac/s@1ghz,浮点运算性能为16gflops@1ghz,并且自带能实现不同规模、不同数据格式的单精度浮点或32位定点fft运算的硬件加速器。

29、3.通过实际测试,采用该嵌入式系统及功能载荷重构方法,载荷每一个单核的加载文件长度为800kbits,单核的实时在线快速更新可在50毫秒内完成。同时由于采用pc机与dsp嵌入式系统紧耦合设计思路,需要重构的功能载荷数量不受dsp芯片外围存储资源的限制,传输距离更远,可满足更多的应用场景需求。

30、4.本发明的嵌入式系统及其功能载荷重构方法,可以应用于“平台+载荷”设计思路的各类软件无线电(sdr)、认知无线(cr)系统以及人工智能(ai)算力设备中。

- 还没有人留言评论。精彩留言会获得点赞!