FPGA平台桥接HLS技术和硬件构造的芯片设计方法

本发明涉及芯片设计自动化,具体涉及一种面向现场可编程门阵列的桥接高层次综合技术和低层次硬件构造的设计方法。

背景技术:

1、现场可编程门阵列(fpga)广泛用于原型设计和加速各种应用,包括机器学习、数据分析等。fpga最吸引人的特点是,它可以通过编程进行定制,以应对不同的应用。对fpga进行编程有两种主要方法。第一种方法是采用低层次硬件构造方法,手动编写寄存器传输级别(rtl)硬件描述语言,如verilog和vhdl,它们将硬件结构描述为寄存器和组合逻辑。第二种方法是使用hls(high level synthesis,高层次综合、高级综合工具)技术,如xilinxvitis hls,这些工具使用c/c++和opencl等高级语言描述硬件的行为,并自动合成为rtl设计。

2、这两种方法在性能和生产率方面表现出不同的权衡。rtl抽象接近硬件的本质,使用户能够完全控制硬件设计,具有良好的性能和资源利用率。由于低级抽象,rtl描述通常很冗长,并且需要很长时间才能开发。相比之下,高层次综合技术通过提高抽象级别来提高生产力。然而,由于语义差异,高层次综合技术和手动rtl设计之间仍然存在明显的性能差距。同时,hls工具提供的各种优化指令,在硬件设计实践中的复杂使用会带来额外的挑战。

3、硬件构造语言(hcl),如chisel(chisel:constructing hardware in a scalaembedded language》,jonathan bachrach等,dac 2012.),逐渐在应用专用芯片(asic)的设计中流行。虽然hcl引入高级语言功能以增加硬件设计的生产力,并且其描述硬件的完整性和通用性与rtl相同,有助于避免采用高层次综合工具生成硬件的性能不可预测问题。但用户仍然需要在硬件构造语言中手动设计和实现硬件控制逻辑,冗长的设计任务需要消耗硬件设计人员的大量精力。例如,实现嵌套循环的硬件控制器可能需要数百行代码。虽然采用硬件构造语言进行芯片设计具有诸多好处,但到目前为止还没有专门面向fpga设备的硬件构造语言。

技术实现思路

1、为了克服上述现有技术存在的不足,本发明提出了一种在fpga上桥接高层次综合技术和低层次硬件构造的芯片设计方法,基于流行的硬件构造语言、融合高层次综合技术,生成fpga专用的芯片硬件。

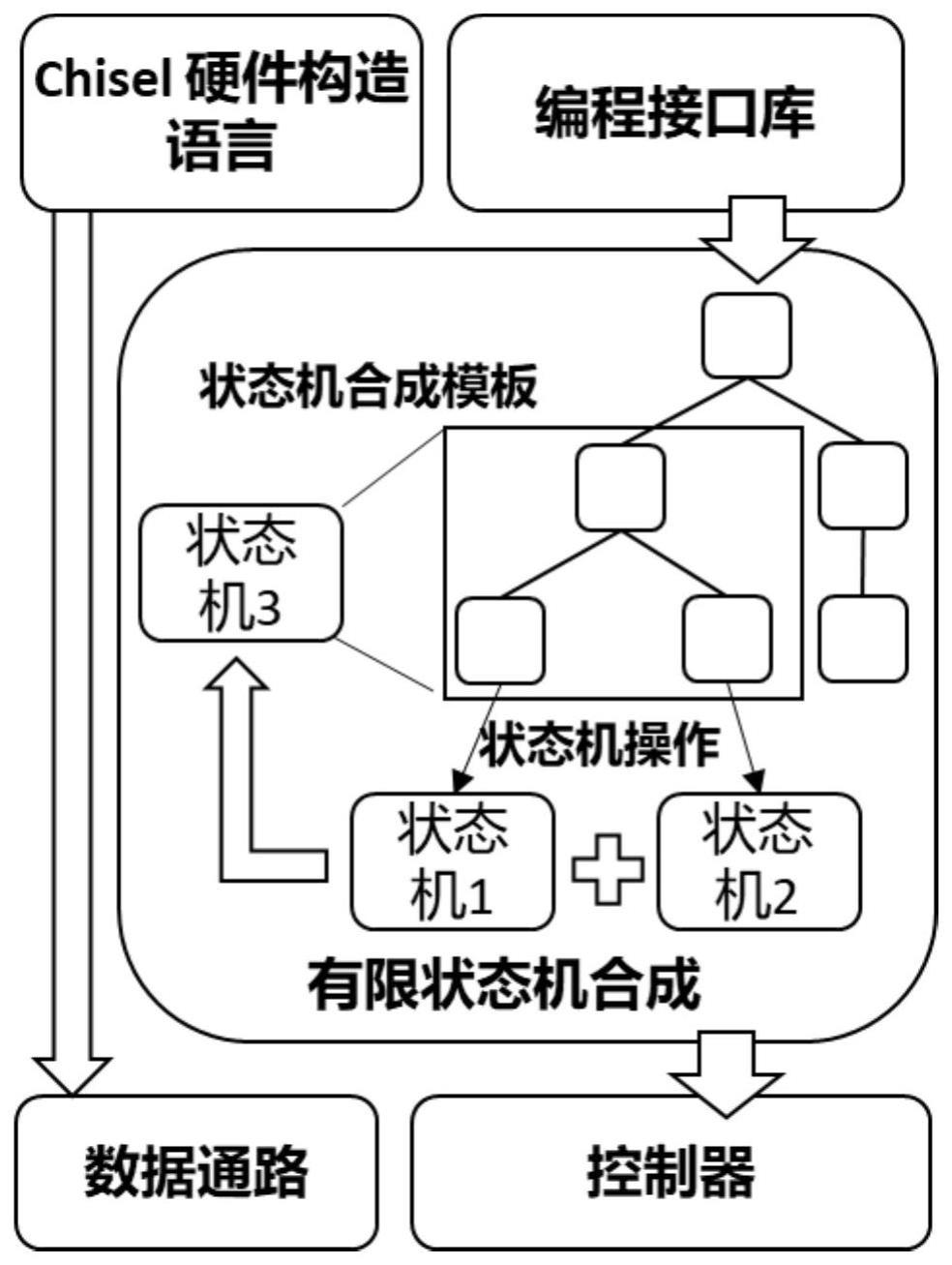

2、本发明将高层次综合技术使用的高级语言功能集成到寄存器传输rtl级别的硬件编程中,提供嵌入在chisel硬件构造语言中的编程接口库。编程接口库提供高级控制语句来描述硬件的控制行为,并与chisel支持的硬件数据通路描述紧密结合,支持完整、通用的硬件描述功能;再根据高层次控制描述实现有限状态机(fsm)的自动生成,生成技术保证fsm具有与高层次描述相同的周期精确的控制行为。

3、本发明方法首先提供基于硬件构造语言chisel的编程接口库,具体为类c的高层次命令式编程模型,支持控制语句的层次结构,并与chisel共同实现在高级编程语言scala中,实现无缝合作以提供通用的硬件描述功能。

4、本发明将编程接口库中的编程原语实现为scala语言中的高阶函数,即每个控制原语被允许作为另一个控制原语的函数参数。每个控制原语被表示为抽象语法树(ast)数据格式,并传递给生成器后端以实现有限状态机和硬件电路的构造生成。

5、然后,以编程接口库输出的抽象语法树作为输入,合成有限状态机生成硬件,并保证生成的fsm及硬件实现的周期级行为与基于编程接口库的高层次描述相同,并优化合成有限状态机的资源消耗。本发明使用状态数作为资源消耗的指标,并尝试尽可能减少状态数。有限状态机的合成过程是利用本发明面向有限状态机定义的一套操作集合和规则,在抽象语法树上完成自下而上的树遍历并递归构造有限状态自动机,保证周期行为准确性和最小的资源开销。本发明为所有前端编程接口库提供的控制原语提供构造有限状态机的合成模板。

6、具体实施时,本发明提供的一种在fpga上桥接高层次综合技术hls和低层次硬件构造的芯片设计方法包括如下步骤:

7、s1.设计基于硬件构造语言的编程接口库,编程接口库用于描述芯片硬件的控制行为;

8、编程接口库提供三类控制原语用以描述硬件控制行为:

9、11)原子性原语:即step原语,声明在一个周期内完成执行的用chisel原生语法描述的硬件逻辑,作为分割跨周期硬件时序控制行为和周期内硬件组合逻辑的编程语法;

10、12)串行原语:包括block、if、for、while四个具体原语,对应软件编程语言中的常见控制流语法,其层次化的组合使用帮助描述复杂的硬件控制行为,如循环嵌套;

11、13)并行原语:包括folk、pipeline两个具体原语,分别描述folk-join风格的硬件控制逻辑和流水线电路的硬件控制逻辑,利用并行获得硬件性能的提升;folk-join风格是一种并行编程模式,指配置并运行独立并发的子任务(fork),并在适当的时间点等待全部子任务完成并恢复后续的串行执行模式(join)(structured parallel programming:patterns for efficient computation》,michael mccool等,elsevier)。

12、s2.根据编程接口库设计有限状态机的表示及有限状态机对应的硬件;包括定义用于有限状态机合成的基本操作(合并、分割、连接、循环)和定义有限状态机的合成模板。

13、将有限状态机表示为入口、内容、出口三部分,设计有限状态机的表示形式,包括状态机的状态和转移,状态机控制的逻辑行为或输出;有限状态机对应的硬件设计相对应地包括状态寄存器、转移逻辑和输出逻辑三部分。

14、有限状态机合成的基本操作用于修改与创建有限状态机。具体实施时,用户结合chisel硬件构造语言和本发明提供的编程接口库描述硬件设计,编程接口库描述的控制行为通过有限状态机的操作和有限状态机合成模板合成符合控制行为描述的有限状态机。

15、通过编程接口库合成有限状态机生成芯片硬件,使得生成的有限状态机fsm及硬件实现的周期级行为与基于编程接口库的高层次描述相同,并优化合成有限状态机的资源消耗。

16、利用四种有限状态机合成的基本操作以及八种高层次控制原语对应的状态机合成模板实现有限状态机的合成。

17、s3.通过有限状态机和硬件构造语言统一输出为完整的硬件控制器和数据通路设计。

18、结合有限状态机合成的基本操作及状态机合成模板实现自动化、高性能、资源高效的状态机合成与硬件生成,包含硬件数据通路以及硬件控制器。其中,本发明面向fpga平台的硬件架构特点,如查找表与寄存器结合为可重构逻辑块,优化硬件控制器的寄存器传输级别(rtl)硬件描述的生成,保证生成代码的风格发挥fpga硬件的性能与功耗资源效率,基于fpga平台和公开数据集充分验证。

19、与现有技术相比,本发明的有益技术效果:

20、本发明提出了一种基于硬件构造语言的硬件设计方法及工具,融合面向现场可编程门阵列设备的高层次综合技术的优势功能,有效结合硬件构造语言的低层次通用表示能力和性能优化空间,以及高层次综合技术的生产力优势。本发明方法主要可应用于加速器敏捷设计。在针对新的加速应用设计面向现场可编程门阵列的加速器时,可以使用本发明,获得与高层次综合技术相当的生产力,同时不牺牲低层次硬件设计方法的通用表示能力和性能潜力。本发明可以应用于人工智能、大数据、科学计算等领域应用的硬件设计中,实现快速高效的硬件设计,并部署在现场可编程门阵列上,实现敏捷的硬件加速。

- 还没有人留言评论。精彩留言会获得点赞!