面向Kyber的高性能拒绝采样硬件电路

本发明涉及拒绝采样硬件电路,尤其是涉及一种面向kyber的高性能拒绝采样硬件电路。

背景技术:

1、为了应对量子计算机攻击带来的安全隐患,美国国家标准与技术研究院(nist)发起后量子密码标准全球征集竞赛,在第三轮比赛中,crystals-kyber成功通过选拔。kyber是一种基于模格的算法,计算速度较快、通信开销相对较低,安全性取决于模格上带错误学习问题的难度。

2、相较于软件实现的kyber算法,硬件实现的kyber算法速度要快很多。为了在军事和医疗等复杂应用场景中缩短加解密时间,需要采用高速的硬件实现的kyber算法。硬件实现的kyber算法通常包括控制模块、ntt(number theoretic transform,ntt)模块、随机数生成模块、采样模块、编码和解码模块以及压缩和解压缩模块,控制模块用于协调ntt模块、随机数生成模块、采样模块、编码和解码模块以及压缩和解压缩模块之间的操作和通信,控制密钥生成、加密和解密的流程,并确保数据在ntt模块、随机数生成模块、采样模块、编码和解码模块以及压缩和解压缩模块之间正确地传输和处理。ntt模块用于将来自随机数生成模块的随机数作为多项式的系数执行ntt变换以实现加密操作生成新系数向量,以及将来自于采样模块的随机数作为多项式的系数执行逆ntt变换以实现解密操作,得到原始数据。随机数生成模块用于接收来自外部的随机种子,并将随机种子采用基于哈希函数的伪随机数生成器(prng)生成随机数,确保密码系统的安全性和随机性。采样模块包括拒绝采样模块和二项分布采样模块:拒绝采样模块用于将来自随机数生成模块的随机数采用拒绝采样生成密钥生成阶段的多项式矩阵a和加密阶段的多项式矩阵at。二项分布采样模块用于将来自随机数生成模块的随机数进行二项分布采样生成密钥交换阶段和加密阶段所需的随机数。编码模块接收来自ntt模块输出的数据,并将其编码,以便在发送过程中进行传输。解码模块接收经过传输和可能受损的数据,例如来自通信信道的数据,并将其解码为原始数据,供ntt模块进行逆变换。压缩和解压缩模块用于压缩和恢复数据。压缩模块使用压缩算法对其他模块输出的数据进行压缩。解压缩模块则用于还原压缩后的数据,以供其他模块进行进一步处理或解密操作。

3、硬件实现的kyber算法中的拒绝采样模块对于随机数成成模块的随机数采用拒绝采样生成密钥生成阶段的多项式矩阵a和加密阶段的多项式矩阵at,当样本小于模数q(3329)时,接受并储存样本,硬件实现的kyber算法的安全等级如表1所示,其中k用于选择多项式矩阵的维度并调整算法安全等级。由于kyber算法的参数不同,多项式的采样个数也不一样,多项式矩阵a和at都有k×k个n阶多项式,kyber512进行设计优化时需要采样出4个256阶的多项式。

4、表1

5、

6、现有的拒绝采样硬件电路主要有以下几种架构:第一种硬件结构包括一个拒绝采样器和存储器,完成4×256个样本的采样,并且为了将拒绝采样模块的数据位宽与采样所需位数匹配,会舍弃部分输入的随机数,这样虽然采样结构简单,硬件开销小,但会造成随机数资源浪费,采样时间也大大增加,采样拒绝率仍然较高。第二种硬件结构包括分周期循环的复杂宽度转换模块、多个并行的拒绝采样器和存储器,将输入的随机数按采样所需位数的倍数分组输入和组合,这样不会有随机数的浪费,并且用了多个拒绝采样器,采样时间大大下降,但由于宽度转换模块需要多个周期来完成宽度的转换和数据的分组合并,并且相对于第一种硬件结构来说存在多个拒绝采样器,导致硬件开销大,拒绝率仍然较高。当前,为了降低拒绝率,有的方案在第二种硬件结构的基础上通过模约简降低拒绝率,但这样会使拒绝采样器结构变得复杂,大大增加硬件开销,有的采用可接受范围设置为[0,q)的拒绝采样器减少面积消耗,同时利用硬件冗余的思想降低拒绝率,但是同样加大了硬件开销。

技术实现思路

1、本发明所要解决的技术问题是提供一种既不会资源浪费随机数资源,采样时间短,采样效率高,且可以降低拒绝率,减少硬件开销的面向kyber的拒绝采样硬件电路。

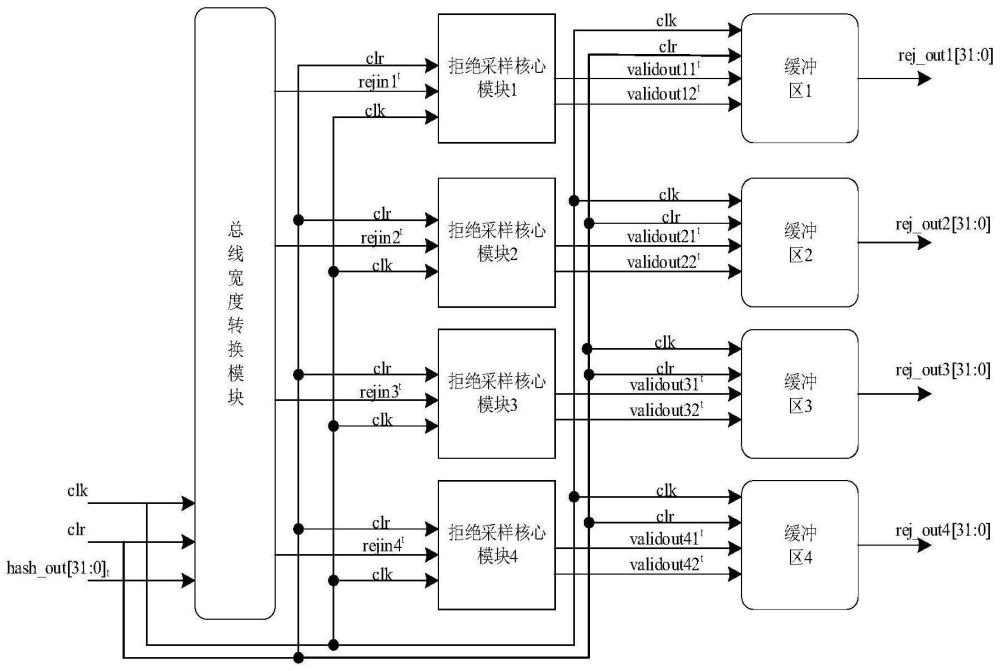

2、本发明解决上述技术问题所采用的技术方案为:一种面向kyber的拒绝采样硬件电路,包括总线宽度转换模块、四个拒绝采样核心采样模块和四个缓冲区,将四个拒绝采样核心采样模块分别称为拒绝采样核心采样模块1、拒绝采样核心采样模块2、拒绝采样核心采样模块3和拒绝采样核心采样模块4,将四个缓冲区分别称为缓冲区1、缓冲区2、缓冲区3和缓冲区4,所述的总线宽度转换模块分别与所述的拒绝采样核心采样模块1、所述的拒绝采样核心采样模块2、所述的拒绝采样核心采样模块3和所述的拒绝采样核心采样模块4连接,所述的拒绝采样核心采样模块1与所述的缓冲区1连接,所述的拒绝采样核心采样模块2与所述的缓冲区2连接,所述的拒绝采样核心采样模块3与所述的缓冲区3连接,所述的拒绝采样核心采样模块4与所述的缓冲区4连接,所述的总线宽度转换模块用于接入硬件实现的kyber算法的随机数生成模块产生的随机数,所述的总线宽度转换模块每次接入32位二进制随机数,每接入一个32位二进制随机数,就进入一个数据处理周期,在每个数据处理周期,所述的总线宽度转换模块将当前接入的32位二进制随机数按顺序分为四个8位随机数一一对应输出至所述的拒绝采样核心模块1、所述的拒绝采样核心模块2、所述的拒绝采样核心模块3和所述的拒绝采样核心模块4处,完成一个数据处理周期,然后接入下一个32位二进制随机数,进入下一个数据处理周期,周而复始,直至拒绝采样工作完成,将所述的总线宽度转换模块当前所处数据处理周期记为t,所述的总线宽度转换模块在第t个数据处理周期接入的32位二进制随机数记为hash_out[31:0]t,得到四个8位随机数分别为hash_out[7:0]t、hash_out[15:8]t、hash_out[23:16]t以及hash_out[31:24]t,将hash_out[7:0]t记为rejin1t、hash_out[15:8]t记为rejin2t、hash_out[23:16]t记为rejin3t、hash_out[31:24]t记为rejin4t;其中,随机数rejin1t输出至所述的拒绝采样核心模块1,rejin2t输出至所述的拒绝采样核心模块2,rejin3t输出至所述的拒绝采样核心模块3,rejin4t输出至所述的拒绝采样核心模块4;

3、当rejin1t输出至所述的拒绝采样核心模块1时,所述的拒绝采样核心模块1利用基于二进制数的位权值特征设计的高效率比较器对所述的随机数rejin1t进行判断,具体过程为:

4、s1、将rejin1t拆分为高4bits数据和低4bits数据,高4bits数据记为rejin1t[7:4],低4bits数据记为rejin1t[3:0],然后进入步骤s2;

5、s2、将rejin1t[7:4]和rejin1t[3:0]分别与4’b1101比较大小,如果rejin1t[7:4]和rejin1t[3:0]中至少一个大于4’b1101,则拒绝接受rejin1t,并输出低电平信号至所述的缓冲区1,控制所述的缓冲区1不从所述的拒绝采样核心模块1处采集数据,完成一次拒绝采样,然后在所述的总线宽度转换模块在第t+1个数据处理周期输出随机数rejin1t+1至所述的拒绝采样核心模块1时,所述的拒绝采样核心模块1再返回步骤s1开始进行下一次判断;如果re jin1t[7:4]和rejin1t[3:0]均小于4’b1101,则接受并保存rejin1t,然后进入步骤s3,此时rejin1t为经过拒绝判断而保存的随机数;

6、s3、所述的拒绝采样核心模块1判断其处当前是否存在被接受并保存的三个随机数,如果不存在,则输出低电平信号至所述的缓冲区1,然后在所述的总线宽度转换模块在第t+1个数据处理周期输出随机数rejin1t+1时直接接受并保存随机数rejin1t+1后再返回步骤s3开始进行下一次判断,此时rejin1t+1为直接保存的随机数;如果存在被接受并保存的三个随机数,三个随机数中会存在一个经过拒绝判断而保存的随机数以及两个直接接受并保存的随机数,将该三个随机数中经过拒绝判断而保存的随机数称为rejin1t1,直接接受并保存两个随机数按照接受先后顺序分别称为rejin1t2和rejin1t3,然后将rejin1t1的高4bits随机数作为高位与rejin1t3拼接为随机数validout11t,将rejin1t1的低4bits随机数作为高位与rejin1t2拼接为随机数validout12t,将validout11t、validout12t以及高电平输出至所述的缓冲区1,然后清空其内被接受并保存的三个随机数,完成一次拒绝采样,并在所述的总线宽度转换模块下一次输出随机数至所述的拒绝采样核心模块1时,所述的拒绝采样核心模块1再返回步骤s1开始进行下一次判断;

7、所述的缓冲区1在所述的拒绝采样核心模块1控制下进行工作,当所述的拒绝采样核心模块1输出低电平时,所述的缓冲区1不从所述的拒绝采样核心模块1处采集数据,当所述的拒绝采样核心模块1输出validout11t、validout12t以及高电平时,所述的缓冲区1采集validout11t和validout12t,并先将validout11t作为高位数据、validout12t作为低位数据进行拼接,然后在最高位前补充8位0,得到一个样本进行保存并输出,然后清空其内保存的样本,并统计其内当前已经保存过的样本总数量是否为256个,如果不是,则表明所述的拒绝采样核心模块1拒绝采样工作未完成,输出低电平给kyber算法的随机数生成模块,使kyber算法的随机数生成模块继续输出随机数至所述的总线宽度转换模块;如果是,则表明所述的拒绝采样核心模块1拒绝采样工作完成,输出高电平给kyber算法的随机数生成模块,之后所述的拒绝采样核心模块1进入非工作状态;

8、所述的拒绝采样核心采样模块2和所述的缓冲区2、所述的拒绝采样核心采样模块3和所述的缓冲区3、所述的拒绝采样核心采样模块4和所述的缓冲区4的工作过程均与所述的拒绝采样核心采样模块1和所述的缓冲区1的相同;当所述的缓冲区1、所述的缓冲区2、所述的缓冲区3和所述的缓冲区4都输出高电平给kyber算法的随机数生成模块时,所述的拒绝采样硬件电路进入非工作状态。

9、与现有技术相比,本发明的优点在于通过总线宽度转换模块、四个拒绝采样核心采样模块和四个缓冲区构建面向kyber的拒绝采样硬件电路,当随机数生成模块生成的随机数传输至拒绝采样硬件电路时,总线宽度转换模块每个数据处理周期接入一个32位二进制随机数,并将32位二进制随机数划分为4个8位二进制随机数一一对应发送至四个拒绝采样核心采样模块进行后续拒绝采样流程,随机数生成模块生成的所有随机数资源均会流入后续拒绝采样流程,充分利用了随机数生成模块生成的随机数资源,不会造成随机数的浪费,同时总线宽度转换器将每个数据处理周期接入的随机数(即32位二进制随机数)进行均等划分为四个8位随机数一一对应输出至四个拒绝采样核心模块处进行后续拒绝采样流程,不需要采用复杂的结构来按周期分配和分割总线宽度转换模块接入的随机数,采用简单的结构即可实现,减少硬件开销,另外,四个拒绝采样核心模块利用基于二进制数的位权值特征设计的高效率比较器实现拒绝采样过程,在拒绝采样过程中利用随机数的再组合和二进制数的位权值特性,只需对三个有效随机数组合而成的随机数组中其中一个随机数进行拒绝判断,其余两个随机数直接接收,同时减少了采样时间和硬件开销,并且采样的拒绝率得到降低,从(212-3329)/212=18.73%下降为[3-(0.81252+1+1)]/(1+1+1)=11.33%,由此本发明既不会资源浪费随机数资源,采样时间短,采样效率高,且可以降低拒绝率,减少硬件开销。

- 还没有人留言评论。精彩留言会获得点赞!