一种数据流与控制流分离的高速存储方法及高速存储装置与流程

本发明涉及高速存储,具体涉及一种高速存储装置和一种数据流与控制流分离的高速存储方法。

背景技术:

1、在高速存储场景下,例如,数据记录仪进行高速存储的场景下,常规的技术方案通常是将数据接收、数据存储以及文件系统都放在操作系统下进行,以对外提供网络硬盘等服务。但是,在大容量且高速写入负载占绝大多数的应用场景下,例如车辆、船舶、飞机等设施的数据记录仪,为了提供更多的数据接口,常常选择使用raid卡对存储进行管理,但是raid卡目前无法自主可控,如果对高速接口的需求变多,则常规cpu无法满足丰富的数据接口需求,只能使用fpga进行自定义实现,所以也许可以从以下方案进行改进:

2、第一,使用国产fpga用逻辑实现raid卡功能;该方案的优点是改动小,缺点是无法满足丰富的数据接口需求,且逻辑实现的raid卡性能上相比raid卡较差。

3、第二,使用fpga作为数据接口,数据存储和文件系统仍放在操作系统上;该方案和传统方案相比,存储部分的设计完全相同,这样解决了数据接口不方便扩展的问题,但是,由于高速带宽仍然通过操作系统,对内存(ddr)芯片和fpga与cpu之间的连接接口的要求比较高,同时对文件系统的压力比较大,高速持续写入过程中容易受到文件系统和固态硬盘写入放大影响,此影响是叠加的影响,文件系统的延时和固态硬盘的延时均会对性能产生影响。

4、第三,使用fpga作为数据接口,数据存储不放在操作系统,而放在fpga,使得控制流经过操作系统,而数据流经过fpga,从而,由于控制流和数据流分离,这样能够有效降低文件存储的延时,但由于存储和文件系统分离,因此,该方案无法直接使用操作系统下的文件系统,需要自行设计简单的文件系统或者移植操作系统内核的文件系统,同时设计软件中间件连接以便使用网络存储服务。自行设计文件系统时,需要针对具体情况专门设计,通用性不强,且健壮性远不如成熟的文件系统;同时自行设计的文件系统中,数据恢复和快照等高级功能无法实现。而移植操作系统内核的文件系统工作量大且复杂,并且很难做到完整移植,同时当文件系统需要更换,例如从ext4改为xfs,则需要重新移植,研发成本很高且难以预计实际效果。

5、因此,上述技术方案存在的缺陷是:在高速存储场景下,无法利用自身文件系统降低文件存储的延时。

技术实现思路

1、本发明的主要目的是提供一种高速存储装置和一种数据流与控制流分离的高速存储方法,旨在解决在高速存储场景下,无法利用自身文件系统降低文件存储的延时的弊端。

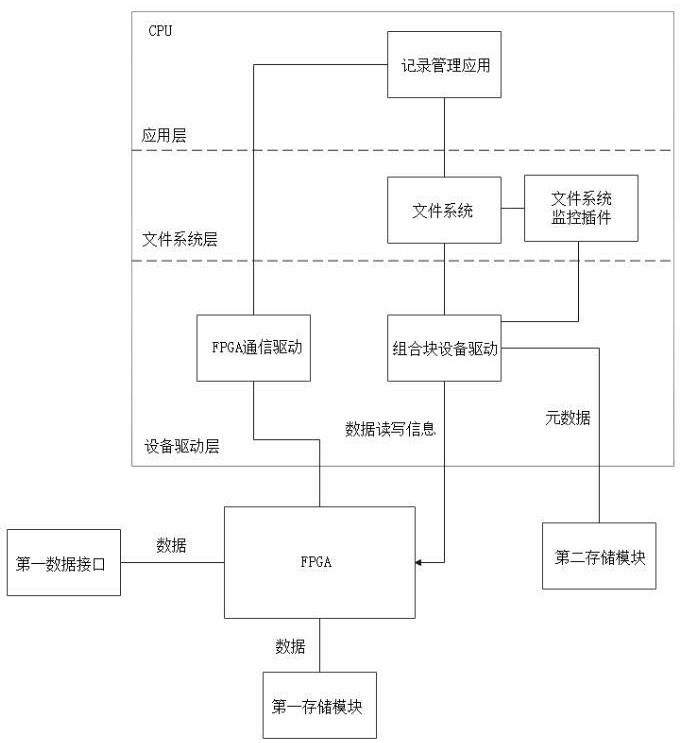

2、为实现上述目的,本发明提出一种高速存储装置,包括cpu和fpga;所述fpga设置有第一数据接口,并连接有第一存储模块;所述cpu连接有第二存储模块;所述cpu包括应用层、文件系统层和设备驱动层;

3、所述应用层包括记录管理应用;所述文件系统层包括文件系统与文件系统监控插件;所述设备驱动层包括fpga通信驱动和组合块设备驱动;

4、所述记录管理应用、所述fpga通信驱动与所述fpga依次通信连接;所述记录管理应用、所述文件系统、所述组合块设备驱动与所述fpga依次通信连接;所述文件系统监控插件分别与所述文件系统和所述组合块设备驱动通信连接;所述组合块设备驱动与所述第二存储模块通信连接;

5、所述记录管理应用用于根据所述fpga连接的所述第一数据接口接收的待存储数据生成第一文件操作请求;

6、所述文件系统用于将所述第一文件操作请求转化为第一块设备读写请求;

7、所述文件系统监控插件用于根据所述第一块设备读写请求,为数据分配第一存储地址,为元数据分配第二存储地址;

8、所述组合块设备驱动用于将所述第一存储地址重映射到第一存储模块的存储地址,将所述第二存储地址重映射到第二存储模块的存储地址,将分配到第二存储地址的元数据存储至所述第二存储模块;

9、所述fpga用于根据所述第一存储地址重映射到第一存储模块的存储地址,将缓存的所述待存储数据存储至所述第一存储模块。

10、优选地,所述记录管理应用还用于:

11、在所述fpga通过所述第一数据接口接收到外部数据时,通过所述fpga通信驱动对所述fpga进行内存空间管理,以在所述fpga对所述待存储数据进行缓存。

12、优选地,所述文件系统监控插件具体用于:

13、在接收到所述第一块设备读写请求后,判断所述第一块设备读写请求在所述文件系统中的文件系统请求类型,根据文件请求类型分配存储地址,并将分配的所述存储地址发送至所述组合块设备驱动,其中,当所述文件系统请求类型为数据时,所述文件系统监控插件分配第一存储地址,当所述文件系统请求类型为元数据时,所述文件系统监控插件分配第二存储地址。

14、优选地,所述cpu设置有第二数据接口;

15、所述记录管理应用还用于:判断待存储数据的接收接口为所述第一数据接口或所述第二数据接口,在所述待存储数据的接收接口为所述第二数据接口时,生成第二文件操作请求;

16、所述文件系统用于将所述第二文件操作请求转化为第二块设备读写请求;

17、所述文件系统监控插件用于根据所述第二块设备读写请求,为数据分配第三存储地址,为元数据分配第四存储地址;

18、所述组合块设备驱动用于将所述第三存储地址重映射到第一存储模块的存储地址,将所述第四存储地址重映射到第二存储模块的存储地址,将分配到第四存储地址的元数据存储至所述第二存储模块;

19、所述fpga用于根据所述第三存储地址重映射到第一存储模块的存储地址,将缓存的所述待存储数据存储至所述第一存储模块。

20、优选地,所述文件系统监控插件适用于多种文件系统,所述文件系统监控插件还用于:

21、从块设备读写请求中,获取数据组织逻辑、数据分配策略和数据结构,其中,块设备读写请求包括第一块设备读写请求和第二块设备读写请求;

22、根据数据组织逻辑、数据分配策略和数据结构,获取块设备读写请求对应的文件系统种类,以及在所述文件系统种类中对应的数据类型,所述数据类型包括元数据和数据。

23、此外,为实现上述目的,本发明还提出一种数据流与控制流分离的高速存储方法,应用于所述高速存储装置,所述方法包括:

24、所述记录管理应用根据所述fpga连接的所述第一数据接口接收的待存储数据生成第一文件操作请求;

25、所述文件系统将所述第一文件操作请求转化为第一块设备读写请求;

26、所述文件系统监控插件根据所述第一块设备读写请求,为数据分配第一存储地址,为元数据分配第二存储地址;

27、所述组合块设备驱动将所述第一存储地址重映射到第一存储模块的存储地址,将所述第二存储地址重映射到第二存储模块的存储地址,将分配到第二存储地址的元数据存储至所述第二存储模块;

28、所述fpga根据所述第一存储地址重映射到第一存储模块的存储地址,将缓存的所述待存储数据存储至所述第一存储模块。

29、优选地,所述cpu设置有第二数据接口;

30、所述方法,还包括:

31、所述记录管理应用判断待存储数据的接收接口为所述第一数据接口或所述第二数据接口,在所述待存储数据的接收接口为所述第二数据接口时,生成第二文件操作请求;

32、所述文件系统将所述第二文件操作请求转化为第二块设备读写请求;

33、所述文件系统监控插件根据所述第二块设备读写请求,为数据分配第三存储地址,为元数据分配第四存储地址;

34、所述组合块设备驱动将所述第三存储地址重映射到第一存储模块的存储地址,将所述第四存储地址重映射到第二存储模块的存储地址,将分配到第四存储地址的元数据存储至所述第二存储模块;

35、所述fpga根据所述第三存储地址重映射到第一存储模块的存储地址,将缓存的所述待存储数据存储至所述第一存储模块。

36、优选地,所述文件系统监控插件适用于多种文件系统,所述方法,还包括:

37、所述文件系统监控插件从块设备读写请求中,获取数据组织逻辑、数据分配策略和数据结构,其中,块设备读写请求包括第一块设备读写请求和第二块设备读写请求;

38、根据数据组织逻辑、数据分配策略和数据结构,获取块设备读写请求对应的文件系统种类,以及在所述文件系统种类中对应的数据类型,所述数据类型包括元数据和数据。

39、优选地,所述方法,还包括:

40、通过所述文件系统监控插件生成快速存储地址序列表,并通过所述组合块设备驱动将快速存储地址序列表发送至所述fpga;

41、侦测所述fpga中的内存空间占用,以及第一数据接口的传输速率;

42、判断所述内存空间占用和所述传输速率是否触发快速存储指令,并确定快速存储指令的作用时段;

43、将所述fpga在所述作用时段内接收到的待存储数据,按照快速存储地址序列表中形成的地址序列,在第一存储模块中进行存储,并将存储地址信息反馈至所述文件系统监控插件。

44、优选地,采用如下方式确定快速存储指令的作用时段:

45、当;

46、其中,代表i时刻,为i时刻fpga已用内存空间,为设定的内存空间占用临界值,小于内存空间容量;为i时刻第一数据接口的传输速率;为启动存储的时刻至i时刻的存储时长;为预设速率,为常数,;为快速存储指令的作用时段开始时间;

47、;

48、;

49、;

50、当;

51、则;

52、其中,为j时刻fpga已用内存空间,j时刻晚于时刻,为j+1时刻fpga已用内存空间,为j+2时刻fpga已用内存空间,为j+3时刻fpga已用内存空间;为j+1时刻相比j时刻fpga的已用内存空间增量,为j+2时刻相比j+1时刻fpga的已用内存空间增量,为j+3时刻相比j+2时刻fpga的已用内存空间增量;为j时刻至j+3时刻第一数据接口的传输速率均值,为启动存储的时刻至j时刻的存储时长;

53、;

54、其中,为j时刻对应的第一数据接口的传输速率,为j+1时刻对应的第一数据接口的传输速率,为j+2时刻对应的第一数据接口的传输速率,为j+3时刻对应的第一数据接口的传输速率;

55、为快速存储指令的作用时段结束时间,代表j+3时刻;

56、采用如下方式生成快速存储地址序列表中每一存储区:

57、;

58、其中,为存储至快速存储地址序列表中第y个存储区的数据所占用的存储空间大小,k为内存空间中已缓存的数据数量,,为内存空间中已缓存的第k个数据的所占用的存储空间大小,为预设的存储空间经验浮动参数,;

59、以第y-1个存储区的存储地址终点的下一地址为存储地址起点,以存储至快速存储地址序列表中第y个存储区的数据所占用的存储空间大小,确定存储空间大小,确定快速存储地址序列表中第y个存储区。

60、本发明的技术方案设计了cpu的应用层、文件系统层和设备驱动层,以使本发明在应用cpu原始文件系统的前提下,将数据流通过fpga管理,而将控制流交给cpu管理,实现数据流和控制流的分离。具体的,fpga的第一数据接口接收高速数据后,cpu的记录管理应用启动cpu这一端的控制流,具体为:在fpga连接的所述第一数据接口接收到待存储数据时,cpu的记录管理应用生成第一文件操作请求,并通过cpu的文件系统将第一文件操作请求转化为第一块设备读写请求,所述文件系统监控插件用于根据所述第一块设备读写请求,为数据分配第一存储地址,为元数据分配第二存储地址;cpu的组合块设备驱动将所述第一存储地址重映射到第一存储模块的存储地址,并将第一存储地址返回至fpga,以使fpga按照第一存储地址重映射到第一存储模块的存储地址,将待存储数据存储至与pfga连接的第一存储模块,而cpu的组合块设备驱动还按照第二存储地址重映射到第二存储模块的存储地址,将元数据存储至与cpu连接的第二存储模块。元数据相比高速数据流占用的空间非常小,因此,元数据通过cpu来管理存储时,对cpu的性能占用也很小,而占用存储空间大的高速数据则全程通过fpga来控制存储,不经过cpu,相比采用cpu来同时管理控制流和高速数据流的方式,极大的降低了cpu的占用情况;所以,避免了元数据和高速数据同时由cpu管理存储的情况下造成的写入延时现象;

61、进一步的,本发明的技术方案通过对cpu的改造,使得整个控制过程仍然通过cpu的操作系统自带的文件系统完成,不需要自行设计新的文件系统,也不需要移植cpu这一侧的操作系统,能够直接利用成熟的操作系统实现控制流走cpu,而数据流走fpga。

62、因此,本发明有利于解决在高速存储场景下,无法利用自身文件系统降低文件存储的延时的弊端。

- 还没有人留言评论。精彩留言会获得点赞!