FPGA配置FLASH芯片抗单粒子翻转电路及方法与流程

fpga配置flash芯片抗单粒子翻转电路及方法

技术领域

1.本发明涉及fpga芯片的抗辐加固领域,特别涉及一种fpga配置flash芯片抗单粒子翻转电路及方法。

背景技术:

2.随着空间平台有效载荷技术的不断发展,对可编程阵列在千万门数以上级别的sram型fpga芯片的需求越来越多,对fpga配置程序文件存储芯片的容量需求也越来越大。常规的反熔丝型prom芯片单片存储容量不超过16mb,无法满足超大规模fpga芯片的使用需求,而级联使用时不仅增加了电路的复杂度、体积和成本,而且降低了电路的抗干扰性和可靠性,只能选用容量较大的flash芯片或mram芯片等来存储配置程序文件。从成本角度考虑通常采用flash芯片作为超大规模fpga芯片的配置芯片,但flash芯片在轨工作时易受空间辐射环境的影响,发生单粒子翻转等问题,同时随着使用次数的增加会产生坏块,导致fpga芯片配置电路的可靠性极低。目前对空间应用的fpga电路的关注点主要在fpga芯片的抗辐加固领域,急需对超大规模fpga的配置flash芯片的配置电路进行研究,降低失效率,提升可靠性。

3.目前对于flash芯片抗单粒子翻转的方法主要局限于三模冗余法和分组码纠错法。三模冗余法是通过在硬件电路设计上或在软件设计中采用三个相同设计电路并行处理数据,对结果进行三取二判决的设计方法。既增加了电路或算法的复杂度,而三模冗余法也无法彻底解决长期使用过程中flash芯片出现坏块的问题,同时三取二判决电路也存在单粒子翻转或单点失效的可能性。分组码纠错法的容错率较低,一般仅能纠一检二,而且译码算法复杂,译码延时较长,不适用于存储量较大的flash芯片的数据读取。

技术实现要素:

4.为了增强空间应用的超大规模fpga配置flash芯片应对单粒子翻转事件和其他数据出错问题的能力,本发明提出了一种fpga配置flash芯片抗单粒子翻转电路及方法。

5.为了解决上述技术问题,本发明的技术方案为:

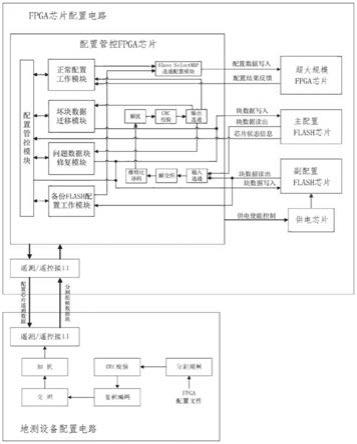

6.一种fpga配置flash芯片抗单粒子翻转电路,包括配置管控fpga芯片、超大规模fpga芯片、主配置flash芯片、副配置flash芯片、供电芯片、第一接口和地测设备配置电路;所述超大规模fpga芯片、主配置flash芯片和所述副配置flash芯片分别与所述配置管控fpga芯片连接;所述配置管控fpga芯片的使能端与所述供电芯片连接,所述供电芯片与所述副配置flash芯片连接;所述配置管控fpga芯片通过所述第一接口与所述地测设备配置电路连接。

7.优选的,所述配置管控fpga芯片包括配置管控模块、正常配置工作模块、坏块数据迁移模块、问题数据块修复模块、备份flash配置工作模块、选通配置模块、输入选通模块、解交织模块、维特比译码模块、解扰模块、第一crc校验模块和输出选通模块;所述正常配置工作模块、坏块数据迁移模块、问题数据块修复模块和所述备份flash配置工作模块分别与

所述配置管控模块通信连接;所述正常配置工作模块和所述备份flash配置工作模块分别与所述选通配置模块连接,所述选通配置模块将配置数据写入所述超大规模fpga芯片;所述超大规模fpga芯片将配置结果反馈给所述正常工作模块;所述主配置flash芯片将芯片状态信息反馈给所述配置管控模块;所述主配置flash芯片将块数据读出至所述输入选通模块,所述输入选通模块依次与所述解交织模块、维特比译码模块、解扰模块、第一crc校验模块和所述输出选通模块连接,所述输出选通模块分别与所述正常配置工作模块和所述坏块数据迁移模块连接;所述配置管控模块、坏块数据迁移模块和所述问题数据块修复模块将块数据写入所述主配置flash芯片和所述副配置flash芯片;所述副配置flash芯片将块数据读出至所述输入选通模块和所述备份flash配置工作模块。

8.优选的,所述地测设备配置电路包括分割组帧模块、第二crc校验模块、卷积编码模块、交织模块、加扰模块和第二接口模块;所述分割组帧模块依次与所述第二crc校验模块、卷积编码模块、交织模块、加扰模块和所述第二接口模块连接;所述第一接口与所述第二接口连接。

9.优选的,所述第一接口为第一遥测接口,所述第二接口为第二遥测接口;或者,所述第一接口为第一遥控接口,所述第二接口为第二遥控接口。

10.优选的,所述供电芯片为ldo低压差电压转换芯片,根据所述配置管控fpga芯片指令给所述副配置flash芯片提供供电电压。

11.优选的,所述配置管控fpga芯片为反熔丝fpga芯片,所述超大规模fpga芯片为sram型fpga芯片。

12.一种fpga配置flash芯片抗单粒子翻转方法,包括以下步骤:

13.s1,在地测设备配置电路上对fpga配置程序文件进行按块分割、组帧处理,依次对每个数据块中的每帧数据进行添加crc校验位、加扰、卷积编码、交织处理后通过遥控接口上传分割组帧数据块,配置管控fpga芯片将fpga配置程序文件存储在主配置flash芯片和副配置flash芯片中,将存储地址表映射信息存储在两片flash的备用存储区指定位置;

14.s2,正常工作时默认进入正常配置工作模式,配置管控模块按地址表映射关系从主配置flash芯片读取fpga配置程序文件数据块,依次对每帧数据进行去交织、维特比译码、解扰、crc校验处理,校验通过后配置超大规模fpga芯片;

15.s3,fpga配置程序文件数据块校验结果有错时按步骤s2对该问题数据块重新进行读取和处理,若校验结果仍然有错则中止配置过程,进入问题数据块修复模式,擦除该数据块的数据,对副配置flash芯片进行加电并读取相同地址的数据块,依次对每帧数据进行去交织、维特比译码、解扰、crc校验处理,校验通过后写入主配置flash芯片的问题数据区,完成后再读取该数据区的数据并依次对每帧数据进行交织、维特比译码、解扰、crc校验处理,若校验通过则退出问题数据块修复模式,进入正常配置工作模式,从步骤s2重新开始配置超大规模fpga芯片;

16.s4,若重新擦写后的问题数据块校验结果仍然有错,则判断该数据区存在坏块,进入坏块数据迁移模式,修改主配置flash芯片中的地址表,标示坏块地址并将数据块地址重新映射到未使用的备用存储区地址,读取副配置flash芯片中对应问题数据区的数据,写入主配置flash芯片中重新映射的备用存储区,完成后再读取该数据区的数据并依次对每帧数据进行去交织、维特比译码、解扰、crc校验处理,校验通过后退出问题数据块修复模式,

进入正常配置工作模式,从步骤s2重新开始配置超大规模fpga芯片,否则应选择下一块备用存储区地址重新写入问题数据区数据,直至备用存储区资源耗尽;

17.s5,当坏块规模超过备用存储区容量时判断主配置flash芯片功能失效,进入备份flash配置工作模式,用副配置flash芯片来配置超大规模fpga芯片。

18.与现有技术相比,本发明的有益效果是:

19.本发明通过冷备份副配置flash芯片电路的设置,降低了因单粒子事件引发配置flash芯片故障而导致fpga功能失效的概率,提升了超大规模fpga芯片配置电路的可靠性;通过在fpga程序配置过程中引入卷积编码和维特比译码进行数据纠错的方法,相对于分组码数据纠错方法既缩短了配置超大规模fpga芯片的时间,又提升了配置flash芯片抗单粒子翻转(包括seu和mbu)的能力。

附图说明

20.图1为本发明一种fpga配置flash芯片抗单粒子翻转电路的原理图;

21.图2为本发明一实施例中配置文件数据写入流程图;

22.图3为本发明一实施例中正常配置工作流程图;

23.图4为本发明一实施例中问题数据块修复流程图;

24.图5为本发明一实施例中坏块数据迁移流程图;

25.图6为本发明一实施例中纠错码处理流程图;

26.图7为本发明一实施例中冷备份flash配置工作流程图。

具体实施方式

27.下面结合附图对本发明的具体实施方式作进一步说明。在此需要说明的是,对于这些实施方式的说明用于帮助理解本发明,但并不构成对本发明的限定。此外,下面所描述的本发明各个实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互组合。

28.实施例一

29.请综合参考图1至图7,一种fpga配置flash芯片抗单粒子翻转电路,包括配置管控fpga芯片、超大规模fpga芯片、主配置flash芯片、副配置flash芯片、供电芯片、第一接口和地测设备配置电路;超大规模fpga芯片、主配置flash芯片和副配置flash芯片分别与配置管控fpga芯片连接;配置管控fpga芯片的使能端与供电芯片连接,供电芯片与副配置flash芯片连接;配置管控fpga芯片通过第一接口与地测设备配置电路连接。

30.工作原理:

31.在地测设备配置电路中按块分割处理fpga配置程序文件,进行卷积编码等处理后通过遥测/遥控接口上传;fpga配置电路接收处理后分别存储在两个配置flash芯片中;在轨工作时,顺序读取配置flash芯片中的数据块,进行维特比译码等处理并配置到fpga;发生无法纠正的单粒子翻转事件或其它问题时修复问题数据块;出现坏块时改用备用存储地址存放原数据块;主配置flash芯片功能丧失时可用副配置flash芯片替代。

32.其中,超大规模fpga芯片为sram型fpga芯片,可编程门电路在千万门级以上,fpga配置程序文件大小不小于64mb,使用大容量flash芯片存储fpga配置程序文件,应用于辐射较强的空间环境,实现电路具体功能;

33.主配置flash芯片容量不小于128mb,功能是存储fpga配置程序文件和flash芯片状态信息,根据配置管控fpga芯片指令输出存储的fpga配置程序文件数据块供超大规模fpga芯片配置使用,根据配置管控fpga芯片指令写入或更新flash芯片状态信息,根据配置管控fpga芯片指令修复发生问题的数据块,根据配置管控fpga芯片指令迁移损坏的存储区的数据到备用存储区;

34.副配置flash芯片容量不小于128mb,用于存储fpga配置程序文件,电路正常工作时处于冷备份状态,当主配置flash芯片出现可修复的问题数据块或坏块时,根据配置管控fpga芯片指令输出存储的fpga配置程序文件数据块供修复主配置flash芯片使用,当主配置flash芯片坏块规模超过备用存储区容量大小时,可根据配置管控fpga芯片指令替代主配置flash芯片配置超大规模fpga芯片;

35.配置管控fpga芯片为反熔丝fpga芯片,功能包括遥控指令接收/处理/转发、遥测信息接收/处理/发送、在地面阶段提供两片flash芯片的数据块写入通道供存储fpga配置程序文件同时在轨工作阶段也可作为写入通道供超大规模fpga芯片配置电路更新fpga配置程序文件、从主配置flash芯片读取配置程序文件进行解交织/维特比译码/解扰/crc校验等处理后以slave selectmap模式配置到超大规模fpga芯片、配置过程发现无法纠错的数据块后对该数据块进行修复、控制供电芯片工作状态、对主配置flash芯片发现的坏块进行地址表更新维护同时从副配置flash芯片读取/处理相应数据后写入替代坏块的备用存储区、在主配置flash芯片坏块规模超过备用存储区容量大小时使用副配置flash芯片进行超大规模fpga芯片配置。

36.在一个实施例中,配置管控fpga芯片包括配置管控模块、正常配置工作模块、坏块数据迁移模块、问题数据块修复模块、备份flash配置工作模块、选通配置模块、输入选通模块、解交织模块、维特比译码模块、解扰模块、第一crc校验模块和输出选通模块;正常配置工作模块、坏块数据迁移模块、问题数据块修复模块和备份flash配置工作模块分别与配置管控模块通信连接;正常配置工作模块和备份flash配置工作模块分别与选通配置模块连接,选通配置模块将配置数据写入超大规模fpga芯片;超大规模fpga芯片将配置结果反馈给正常工作模块;主配置flash芯片将芯片状态信息反馈给配置管控模块;主配置flash芯片将块数据读出至输入选通模块,输入选通模块依次与解交织模块、维特比译码模块、解扰模块、第一crc校验模块和输出选通模块连接,输出选通模块分别与正常配置工作模块和坏块数据迁移模块连接;配置管控模块、坏块数据迁移模块和问题数据块修复模块将块数据写入主配置flash芯片和副配置flash芯片;副配置flash芯片将块数据读出至输入选通模块和备份flash配置工作模块。

37.在一个实施例中,地测设备配置电路包括分割组帧模块、第二crc校验模块、卷积编码模块、交织模块、加扰模块和第二接口模块;分割组帧模块依次与第二crc校验模块、卷积编码模块、交织模块、加扰模块和第二接口模块连接;第一接口与第二接口连接。

38.本实施例中,地测设备配置电路为安装在地测设备上具备rs422接口芯片、lvds接口芯片、1553b接口芯片、fpga芯片和dsp芯片的pcie板卡或cpci板卡,功能包括遥控指令产生/发送,遥测信息接收/处理/存储,对fpga配置文件进行分割组帧处理、crc校验处理、卷积编码处理、交织和加扰处理,分割组帧数据块发送。

39.在一个实施例中,第一接口为第一遥测接口,第二接口为第二遥测接口;或者,第

一接口为第一遥控接口,第二接口为第二遥控接口。

40.在一个实施例中,供电芯片为ldo低压差电压转换芯片,根据配置管控fpga芯片指令给副配置flash芯片提供供电电压。

41.在一个实施例中,fpga配置flash芯片抗单粒子翻转电路配置文件写入流程见图2。

42.地测设备先按照spansion公司flash芯片s29jl064h的最小扇区规模8kbytes对超大规模fpga芯片的配置程序文件进行块分割,再对块数据进行预留校验位的分割组帧;对每帧进行crc校验并填充校验位,建议选用的crc校验校验生成多项式为:

43.f(x)=x

32

+x

26

+x

23

+x

22

+x

16

+x

12

+x

11

+x

10

+x8+x7+x5+x4+x2+x+1

44.因为fpga配置程序文件中存在大量的长0和长1数据,所以添加crc校验位后的块数据还需要进行循环加扰才能进行卷积编码,建议选用pn23或pn15扰码;加扰后的帧数据以块为单位进行卷积编码,建议选用(2,1,7)卷积编码,若想节省存储空间建议选用(4,3,7)删余卷积编码,块数据在尾部应预留一定的固定数据以便译码时能完全接收所有有效数据,编码后生成新的块数据;对该块数据进行交织处理,建议采用将从第二位开始的数据后移5位数据写入,写到尾地址再从未写入数据的首位开始写入的数据交织方法,循环写入直至写满数据区,该方法对块数据交织的随机性不如随机交织的方法,但可将相邻的6bit数据完全分开,结合卷积编码和维特比译码可解决多比特单粒子翻转的问题;交织后的块数据按照测控链路的数据传输帧格式进行分割,以数据块为单位按顺序编号保存成一个个独立的文件形式,通过地测设备的测控通道和配置管控fpga芯片写入到fpga配置电路的两片flash芯片中。根据flash芯片的情况记录其坏块区地址和每块数据的存储区起始地址生成数据表,并写入flash的指定区域。

45.此外,当需要对fpga配置程序进行在轨升级时可通过上述方法经星地测控链路对flash芯片存储文件进行在轨更新。

46.在一个实施例中,fpga配置flash芯片抗单粒子翻转电路的正常配置工作流程见图3。

47.配置管控fpga芯片首先接收配置文件数据块并校验正确性,若不正确则进行问题数据块修复流程甚至进入坏块数据迁移流程或备份配置工作流程,否则以slave slecetmap模式配置超大规模fpga芯片,根据超大规模fpga芯片反馈的配置结果决定是否需要重新配置,直至正常配置工作流程完成。

48.在一个实施例中,fpga配置flash芯片抗单粒子翻转电路的问题数据块修复流程见图4。

49.配置管控fpga芯片首先控制供电芯片进入工作状态;对主配置flash芯片问题数据块进行块擦除并校验是否成功;成功后再从副配置flash芯片对应的地址区读取正确的数据块,校验通过后写入配置flash芯片被擦除的数据区,最后对写入数据进行回读和校验,若正确则问题数据块的修复流程完成。问题数据块的修复过程可能需要多次进行,但一般不超过三次,否则认为该数据块存储区域已产生坏块,应更新地址表的坏块地址,指定映射的备用存储区地址并进入坏块数据迁移流程。

50.在一个实施例中,fpga配置flash芯片抗单粒子翻转电路的坏块数据迁移流程见图5。

51.配置管控fpga芯片控制副配置flash芯片进入工作状态,读取地址表中映射的备用存储区地址并进行擦除,从副配置flash芯片中读取正确数据并进行校验,校验通过后写入主配置flash芯片的备用存储区地址并进行回读校验,校验通过后坏块数据迁移流程完成。若坏块数据迁移过程中发现备用存储区存在坏块则需要对迁移数据区地址进行调整直至通过,若备用存储区资源已经用完则进入冷备份flash配置工作流程。

52.在一个实施例中,fpga配置flash芯片抗单粒子翻转电路的纠错码处理流程见图6。

53.flash芯片存储数据的增加crc校验位、数据加扰、卷积编码、块数据交织等处理己在地测设备上完成,fpga配置电路的数据纠错功能在配置管控fpga芯片中完成。数据纠错时,先在配置管控fpga芯片中进行解交织处理,将发生的突发连续比特错误打散以提高链路的纠错性能,再进行硬判决维特比译码(因数据传输不经过信道,故无需采用软判决维特比译码),译码后的块数据进行解扰处理,最后对解扰后的帧数据进行crc校验。该纠正方法可纠正单比特seu(single event upset)事件和多比特mbu(multiple bit upset)事件。

54.在一个实施例中,fpga配置flash芯片抗单粒子翻转电路的冷备份flash配置工作流程见图7。

55.当主配置flash芯片功能失效时配置管控fpga芯片控制副配置flash芯片进入工作状态,从副配置flash芯片中读取配置文件数据块并校验其正确性,若不正确则进行问题数据块修复流程,否则以slave slecetmap模式配置超大规模fpga芯片,根据超大规模fpga芯片反馈的配置结果决定是否需要重新配置,直至正常配置工作流程完成。需要指出的是因主配置flash芯片功能失效时其内部存在较多的坏块,因此副配置flash芯片的问题数据块修复可能无法成功,此时fpga配置电路的功能将失效。此时,需要指出的是若条件允许可通过星地测控通道将问题数据块数据通过地测设备发送到fpga配置电路并重新写入到副配置flash芯片的问题数据区并进行校验,若校验正确则fpga配置电路的功能将恢复。

56.实施例二

57.请综合参考图1至图7,一种fpga配置flash芯片抗单粒子翻转方法,包括以下步骤:

58.s1,在地测设备配置电路上对fpga配置程序文件进行按块分割、组帧处理,依次对每个数据块中的每帧数据进行添加crc校验位、加扰、卷积编码、交织处理后通过遥控接口上传分割组帧数据块,配置管控fpga芯片将fpga配置程序文件存储在主配置flash芯片和副配置flash芯片中,将存储地址表映射信息存储在两片flash的备用存储区指定位置;

59.s2,正常工作时默认进入正常配置工作模式,配置管控模块按地址表映射关系从主配置flash芯片读取fpga配置程序文件数据块,依次对每帧数据进行去交织、维特比译码、解扰、crc校验处理,校验通过后配置超大规模fpga芯片;

60.s3,fpga配置程序文件数据块校验结果有错时按步骤s2对该问题数据块重新进行读取和处理,若校验结果仍然有错则中止配置过程,进入问题数据块修复模式,擦除该数据块的数据,对副配置flash芯片进行加电并读取相同地址的数据块,依次对每帧数据进行去交织、维特比译码、解扰、crc校验处理,校验通过后写入主配置flash芯片的问题数据区,完成后再读取该数据区的数据并依次对每帧数据进行交织、维特比译码、解扰、crc校验处理,若校验通过则退出问题数据块修复模式,进入正常配置工作模式,从步骤s2重新开始配置

超大规模fpga芯片;

61.s4,若重新擦写后的问题数据块校验结果仍然有错,则判断该数据区存在坏块,进入坏块数据迁移模式,修改主配置flash芯片中的地址表,标示坏块地址并将数据块地址重新映射到未使用的备用存储区地址,读取副配置flash芯片中对应问题数据区的数据,写入主配置flash芯片中重新映射的备用存储区,完成后再读取该数据区的数据并依次对每帧数据进行去交织、维特比译码、解扰、crc校验处理,校验通过后退出问题数据块修复模式,进入正常配置工作模式,从步骤s2重新开始配置超大规模fpga芯片,否则应选择下一块备用存储区地址重新写入问题数据区数据,直至备用存储区资源耗尽;

62.s5,当坏块规模超过备用存储区容量时判断主配置flash芯片功能失效,进入备份flash配置工作模式,用副配置flash芯片来配置超大规模fpga芯片。

63.本发明采用交织/解交织级联卷积编码/维特比译码可纠正连续35bits内任意位置的4各错误,纠错性能优于分组码;采用硬判决维特比译码,译码延时小于分组码;可对配置flash芯片的问题数据块进行自修复或指令修复;可对主配置flash芯片的坏块地址进行标定,并将坏块上的数据迁移到备用存储区;可用副配置flash替代功能失效的主配置flash芯片进行超大规模fpga芯片配置。

64.以上结合附图对本发明的实施方式作了详细说明,但本发明不限于所描述的实施方式。对于本领域的技术人员而言,在不脱离本发明原理和精神的情况下,对这些实施方式进行多种变化、修改、替换和变型,仍落入本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1