半导体结构的测试方法及测试装置与流程

1.本技术涉及集成电路技术领域,尤其涉及一种半导体结构的测试方法及测试装置。

背景技术:

2.动态随机存储器(dynamic random access memory,dram)是计算机等电子设备中常用的半导体装置,其由多个存储单元构成,每个存储单元通常包括晶体管和电容器。所述晶体管的栅极与字线电连接、源极与位线电连接、漏极与电容器电连接,字线上的字线电压能够控制晶体管的开启和关闭,从而通过位线能够读取存储在电容器中的数据信息,或者将数据信息写入到电容器中。

3.动态随机存储器等半导体结构中包括字线和位线。当前的字线多采用埋入式字线(buried word line,bwl),位线通过位线插塞与晶体管的源极电连接。由于制程工艺的偏差,可能会造成埋入式字线与位线接触与位线接触插塞(bit line contact,blc)之间的短路,即产生缺陷(cross fail)。埋入式字线与位线接触插塞之间发生短路会导致位线的失效,严重影响半导体结构的电性能。但是,当前并没有有效的方法检测埋入式字线与位线接触插塞之间的短路缺陷,从而限制了对半导体结构的改进。

4.因此,如何有效的检测字线与位线之间的短路缺陷,改善半导体结构的电性能,是当前亟待解决的技术问题。

技术实现要素:

5.本技术一些实施例提供的半导体结构的测试方法及测试装置,用于解决不能对字线与位线之间的短路缺陷进行有效检测的问题,以改善半导体结构的电性能。

6.根据一些实施例,本技术提供了一种半导体结构的测试方法,包括如下步骤:

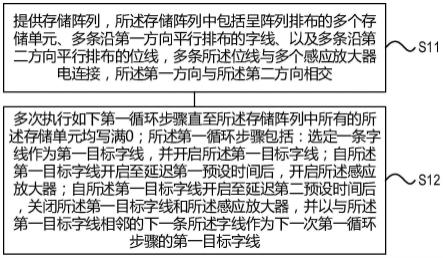

7.提供存储阵列,所述存储阵列中包括呈阵列排布的多个存储单元、多条沿第一方向平行排布的字线、以及多条沿第二方向平行排布的位线,多条所述位线与多个感应放大器电连接,所述第一方向与所述第二方向相交;

8.多次执行如下第一循环步骤,直至所述存储阵列中所有的所述存储单元均写满0;

9.所述第一循环步骤包括:

10.选定一条字线作为第一目标字线,并开启所述第一目标字线;

11.自所述第一目标字线开启至延迟第一预设时间后,开启所述感应放大器;

12.自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和所述感应放大器,并以与所述第一目标字线相邻的下一条所述字线作为下一次第一循环步骤的第一目标字线。

13.在一些实施例中,执行循环步骤之前,还包括如下步骤:

14.于所述存储阵列中所有的所述存储单元均写满0;

15.刷新所述存储阵列。

16.在一些实施例中,执行循环步骤之前,于所述存储阵列中所有的所述存储单元均写满0的具体步骤包括:

17.多次执行如下第二循环步骤,直至所述存储阵列中所有的所述存储单元均写满0,所述第二循环步骤包括:

18.选定一条字线作为第二目标字线,并开启所述第二目标字线;

19.依次写入0至与所述第二目标字线相连的所有所述存储单元中;

20.关闭所述第二目标字线,并以与所述第二目标字线相邻的下一条所述字线作为下一次第二循环步骤的第二目标字线。

21.在一些实施例中,所述第一循环步骤包括:

22.选定一条位线作为目标位线,并开启所述目标位线;

23.对多条所述字线依次执行第一子循环步骤;

24.关闭所述目标位线,并以与所述目标位线相邻的下一条所述位线作为下一次所述第一循环步骤的目标位线;

25.所述第一子循环步骤包括:

26.选定一条字线作为第一目标字线,并开启所述第一目标字线,并于写入0至与所述第一目标字线和所述目标位线均电连接的所述存储单元中;

27.自所述第一目标字线开启至延迟第一预设时间后,开启与所述目标位线电连接的所述感应放大器;

28.自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和与所述目标位线电连接的所述感应放大器,并以与所述第一目标字线相邻的下一条所述字线作为下一次第一循环步骤的第一目标字线。

29.在一些实施例中,所述第一循环步骤包括:

30.选定一条字线作为第一目标字线,并对所述第一目标字线执行第二子循环步骤;

31.对所述第一目标字线执行第二子循环步骤之后,以与所述第一目标字线相邻的下一条所述字线作为下一次第一循环步骤的第一目标字线;

32.所述第二子循环步骤包括:

33.开启所述第一目标字线;

34.开启若干条所述位线,写入0至与所述第一目标字线和若干条所述位线相连的若干个所述存储单元中;

35.自所述第一目标字线开启至延迟第一预设时间后,开启与若干条所述位线电连接的所述感应放大器;

36.自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和与若干条所述位线电连接的所述感应放大器。

37.在一些实施例中,所述第一循环步骤包括:

38.选定一条字线作为第一目标字线,并开启所述第一目标字线;

39.开启所有的所述位线,写入0至与所述第一目标字线相连的所有所述存储单元中;

40.自所述第一目标字线开启至延迟第一预设时间后,开启与所有的所述位线电连接的所述感应放大器;

41.自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和与所

有的所述位线电连接的所述感应放大器,并以与所述第一目标字线相邻的下一条所述字线作为下一次第一循环步骤的第一目标字线。

42.在一些实施例中,所述第一预设时间为10ns~400ns。

43.在一些实施例中,所述第二预设时间为100ns~1000ns。

44.在一些实施例中,所述存储阵列的数量为多个;一个所述存储阵列中所有的所述存储单元均写满0之后,还包括如下步骤:

45.刷新已写满0的所述存储阵列;

46.对下一个所述存储阵列执行所述第一循环步骤,直至下一个所述存储阵列中所有的所述存储单元均写满0。

47.在一些实施例中,所述存储阵列中所有的所述存储单元均写满0之后,还包括如下步骤:

48.读取所述存储阵列中所有的所述存储单元;

49.判断所有所述存储单元的读取值是否均为0,若否,则确认读取值不为0的所述存储单元处的所述字线与所述位线电连接。

50.在一些实施例中,读取所述存储阵列中所有的所述存储单元的具体步骤包括:

51.多次执行第三循环步骤,直至存储存储阵列中所有的所述存储单元均被读取,所述第三循环步骤包括:

52.选定一条字线作为第三目标字线,并读取与所述第三目标字线相连的所有存储单元;

53.与所述第三目标字线相连的所有存储单元均被读取之后,以与所述第三目标字线相邻的下一条所述字线作为下一次第三循环步骤的第三目标字线。

54.根据另一些实施例,本技术还提供了一种半导体结构的测试装置,包括:

55.写入模块,用于多次执行如下第一循环步骤,直至存储阵列中所有的所述存储单元均写满0;所述存储阵列中包括呈阵列排布的多个存储单元、多条沿第一方向平行排布的字线、以及多条沿第二方向平行排布的位线,多条所述位线与多个感应放大器电连接,所述第一方向与所述第二方向相交;所述第一循环步骤包括:选定一条字线作为第一目标字线,并开启所述第一目标字线;自所述第一目标字线开启至延迟第一预设时间后,开启所述感应放大器;自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和所述感应放大器,并以与所述第一目标字线相邻的下一条所述字线作为下一次第一循环步骤的第一目标字线。

56.在一些实施例中,所述半导体结构的测试装置还包括:

57.刷新模块,用于刷新已写满0的所述存储阵列。

58.在一些实施例中,还包括:

59.读取模块,用于读取所述存储阵列中所有的所述存储单元;

60.判断模块,用于判断所有所述存储单元的读取值是否均为0,若否,则确认所述存储阵列存在所述位线和所述字线短路的缺陷。

61.在一些实施例中,所述第一预设时间为10ns~400ns。

62.在一些实施例中,所述第二预设时间为100ns~1000ns。

63.本技术一些实施例提供的半导体结构的测试方法及测试装置,于存储阵列的所有

存储单元中均写满0,利用字线开启时的高电位与位线的低电位之间的产生的压差来模拟字线与位线之间短路的现象。本技术一些实施例在目标字线启动并延迟第一预设时间之后再开启感应放大器、且在所述目标字线启动并延迟第二预设时间之后再关闭所述目标字线,从而延长了从目标字线开启到感应放大器开启的时间以及所述目标字线处于激活状态的时间,从而使得一旦发生字线与位线之间的短路情况时,所述感应放大器能够充分检测到该缺陷,提高了字线与位线之间短路缺陷检测的准确度与检测效率。

附图说明

64.附图1是本技术具体实施方式中半导体结构的测试方法流程图;

65.附图2是本技术具体实施方式中存储阵列的结构示意图;

66.附图3是本技术具体实施方式中第一种半导体结构的测试方法示意图;

67.附图4是本技术具体实施方式中第二种半导体结构的测试方法示意图;

68.附图5是本技术具体实施方式中第三种半导体结构的测试方法示意图;

69.附图6是本技术具体实施方式中半导体结构的测试装置的结构框图。

具体实施方式

70.下面结合附图对本技术提供的半导体结构的测试方法及测试装置的具体实施方式做详细说明。

71.本具体实施方式提供了一种半导体结构的测试方法,附图1是本技术具体实施方式中半导体结构的测试方法流程图,附图2是本技术具体实施方式中存储阵列的结构示意图,附图3是本技术具体实施方式中第一种半导体结构的测试方法示意图。如图1、图2和图3所示,所述半导体结构的测试方法,包括如下步骤:

72.步骤s11,提供存储阵列,所述存储阵列中包括呈阵列排布的多个存储单元20、多条沿第一方向平行排布的字线wl、以及多条沿第二方向平行排布的位线bl,多条所述位线bl与多个感应放大器电连接,所述第一方向与所述第二方向相交。

73.具体来说,所述第一方向与所述第二方向可以是倾斜相交,也可以是垂直相交。所述半导体结构可以是但不限于dram,相应的,所述存储阵列可以是dram中的存储阵列。所述存储阵列位于衬底上,所述衬底内具有呈阵列排布的多个有源区,每个所述有源区中均包括位线接触区和电容接触区。所述字线wl可以为位于所述衬底内的埋入式字线。所述位线bl通过位线接触插塞与所述衬底内的所述位线接触区电连接。当制程工艺出现偏差时,可能会造成所述位线接触插塞与所述字线接触,从而造成所述位线bl与字线wl之间的短路连接。以图2所示的存储阵列的结构示意图为例,每条所述字线wl沿x轴方向延伸,多条所述字线wl沿y轴方向平行排布。每条所述位线bl沿y轴方向延伸,多条所述位线bl沿x轴方向平行排布。在图2所示的结构中,每一条所述字线wl与每一条所述位线bl交叉的位置形成一个所述存储单元20。本具体实施方式中所述的多条是指两条以上。

74.多个所述感应放大器与多条所述位线bl一一对应电连接,每个所述存储区单元20与一条所述位线bl电连接,一条所述位线bl与沿y轴方向平行排布的多个所述存储单元电连接。因此,一个所述感应放大器与多个所述存储单元20对应电连接,一个所述存储单元20仅与一个所述感应放大器对应电连接。当所述位线bl与所述字线wl电连接时,与短接的所

述位线bl电连接的所述感应放大器能够检测到由于所述位线bl与所述字线wl短接所产生的漏电流,从而实现对所述位线bl与所述字线wl短接缺陷的检测。所述感应放大器与所述位线bl的具体电连接方式,本领域技术人员可以根据实际需要进行选择,只要能实现对所述位线bl与所述字线wl短接时产生的漏电流进行检测即可。

75.步骤s12,多次执行如下第一循环步骤,直至所述存储阵列中所有的所述存储单元20均写满0;

76.所述第一循环步骤包括:

77.选定一条字线作为第一目标字线,并开启所述第一目标字线;

78.自所述第一目标字线开启至延迟第一预设时间后,开启所述感应放大器;

79.自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和所述感应放大器,并以与所述第一目标字线相邻的下一条所述字线作为下一次第一循环步骤的第一目标字线。

80.具体来说,在对所述存储阵列进行缺陷检测的过程中,在所述存储阵列的所有所述存储单元20中均写满0,利用字线开启时的高电位与位线的低电位之间的产生的压差来模拟字线与位线之间短路的现象。通过依次开启每条所述字线wl,并依次向与开启的所述字线电连接的所述存储单元20中写入0,通过检测与完成写入操作之后的所述存储单元20对应电连接的所述感应放大器检测到的漏电流情况,即可确认与完成写入操作的所述存储单元20相连的所述字线wl与所述位线bl是否发生短路连接(即短接)。举例来说,当所述感应放大器检测到的漏电流大于阈值时,则确认和该感应放大器电连接的所述位线bl与开启的所述字线wl发生短接。所述阈值的具体数值,本领域技术人员可以根据实际需要进行设置,例如根据所述存储单元20的具体结构进行设置。

81.本具体实施方式在目标字线启动并延迟第一预设时间之后再开启感应放大器、且在所述目标字线启动并延迟第二预设时间之后再关闭所述目标字线,从而延长了从目标字线开启到感应放大器开启的时间以及所述目标字线处于激活状态的时间,从而使得一旦发生字线与位线之间的短路情况时,所述感应放大器能够充分检测到该缺陷,提高了字线与位线之间短路缺陷检测的准确度与检测效率。

82.在一些实施例中,所述第一预设时间为10ns~400ns。例如,所述第一预设时间为10ns、50ns、100ns、200ns、或者400ns。

83.在一些实施例中,所述第二预设时间为100ns~1000ns。例如,所述第二预设时间为100ns、300ns、500ns、700ns、或者1000ns。

84.在一些实施例中,执行循环步骤之前,还包括如下步骤:

85.于所述存储阵列中所有的所述存储单元20均写满0,如图3中的(a)所示;

86.刷新所述存储阵列,如图3中的(b)所示。

87.在一些实施例中,执行循环步骤之前,于所述存储阵列中所有的所述存储单元20均写满0的具体步骤包括:

88.多次执行如下第二循环步骤,直至所述存储阵列中所有的所述存储单元20均写满0,所述第二循环步骤包括:

89.选定一条字线wl作为第二目标字线,并开启所述第二目标字线;

90.依次写入0至与所述第二目标字线相连的所有所述存储单元20中;

91.关闭所述第二目标字线,并以与所述第二目标字线相邻的下一条所述字线wl作为下一次第二循环步骤的第二目标字线。

92.举例来说,第一次执行所述第二循环步骤:选定位于所述存储阵列第一行的所述字线wl作为所述第二目标字线;之后,开启所述第二目标字线以及所有的所述位线bl,使得与所述第二目标字线电连接的所有所述存储单元20均写满0;接着,关闭所述第二目标字线。第二次执行所述第二循环步骤:选定位于所述存储阵列第二行的所述字线wl作为所述第二目标字线;之后,开启所述第二目标字线以及所有的所述位线bl,使得与所述第二目标字线电连接的所有所述存储单元20均写满0;接着,关闭所述第二目标字线。第三次执行所述第二循环步骤:选定位于所述存储阵列第三行的所述字线wl作为所述第二目标字线;之后,开启所述第二目标字线以及所有的所述位线bl,使得与所述第二目标字线电连接的所有所述存储单元20均写满0;接着,关闭所述第二目标字线。以此类推,通过执行多次所述第二循环步骤,使得所述存储阵列中所有的所述字线wl均完成开启和关闭操作,以于所述存储阵列中写满0。

93.本具体实施方式在进入测试模式多次执行所述第一循环步骤之前,先通过多次执行所述第二循环步骤,于所述存储阵列中写满0,避免所述存储阵列中存在其他缺陷的影响,确保所述感应放大器检测到的漏电流是有所述字线wl与所述位线bl短路引起,从而进一步提高测试结果准确度和可靠性。

94.在另一些实施例中,所述第一循环步骤包括:

95.选定一条位线作为目标位线,并开启所述目标位线;

96.对多条所述字线依次执行第一子循环步骤;

97.关闭所述目标位线,并以与所述目标位线相邻的下一条所述位线作为下一次所述第一循环步骤的目标位线;

98.所述第一子循环步骤包括:

99.选定一条字线wl作为第一目标字线,并开启所述第一目标字线,并于写入0至与所述第一目标字线和所述目标位线均电连接的所述存储单元中;

100.自所述第一目标字线开启至延迟第一预设时间后,开启与所述目标位线电连接的所述感应放大器;

101.自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和与所述目标位线电连接的所述感应放大器,并以与所述第一目标字线相邻的下一条所述字线wl作为下一次第一循环步骤的第一目标字线。

102.举例来说,进入测试模式之后,第一次执行所述第一循环步骤:选定位于所述存储阵列第一列的所述位线bl作为目标位线,并开启所述目标位线。接着,第一次执行第一子循环步骤:选定位于所述存储阵列第一行的所述字线wl作为第一目标字线,并开启所述第一目标字线,并写入0至与所述第一目标字线和所述目标位线均电连接的一个所述存储单元中;自所述第一目标字线开启至延迟第一预设时间后,开启与所述目标位线电连接的所述感应放大器;自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和与所述目标位线电连接的所述感应放大器。接着,第二次执行第一子循环步骤:选定位于所述存储阵列第二行的所述字线wl作为第一目标字线,并开启所述第一目标字线,并写入0至与所述第一目标字线和所述目标位线均电连接的一个所述存储单元中;自所述第一目标字

线开启至延迟第一预设时间后,开启与所述目标位线电连接的所述感应放大器;自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和与所述目标位线电连接的所述感应放大器。以此类推,直至多条所述字线wl均完成所述第一子循环步骤,从而使得与所述目标位线电连接的所有所述存储单元20均完成写入0的操作,如图3中的(c)所示。

103.关闭所述目标位线之后,第二次执行所述第一循环步骤:选定位于所述存储阵列第二列的所述位线bl作为目标位线,并开启所述目标位线。接着,多次执行第一子循环步骤,使得与所述目标位线电连接的所有所述存储单元20均完成写入0的操作。其中,多次执行第一子循环步骤的具体操作与第一次执行所述第一循环步骤中多次执行第一子循环步骤的操作相同。

104.以此类推,多次执行所述第一循环步骤之后,使得所述存储阵列中所有的所述位线bl均完成了依次所述第一循环步骤,所述存储阵列中写满0。

105.在另一些实施例中,所述第一循环步骤包括:

106.选定一条字线wl作为第一目标字线,并对所述第一目标字线执行第二子循环步骤;

107.对所述第一目标字线执行第二子循环步骤之后,以与所述第一目标字线相邻的下一条所述字线wl作为下一次第一循环步骤的第一目标字线;

108.所述第二子循环步骤包括:

109.开启所述第一目标字线;

110.开启若干条所述位线,写入0至与所述第一目标字线和若干条所述位线相连的若干个所述存储单元中;

111.自所述第一目标字线开启至延迟第一预设时间后,开启与若干条所述位线电连接的所述感应放大器;

112.自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和与若干条所述位线电连接的所述感应放大器。

113.附图4是本技术具体实施方式中第二种半导体结构的测试方法示意图。图4中的(a)和(b)操作与图3中的(a)和(b)操作相同,区别仅在于第一循环步骤(图4中的(c))与图3中的第一循环步骤(图3中的(c))不同。在图4所示的实施例中,进入测试模式之后,第一次执行所述第一循环步骤:选定位于所述存储阵列第一行的所述字线wl作为所述第一目标字线。接着,对所述第一目标字线第一次执行所述第二子循环步骤:第一次开启所述第一目标字线;开启预设数量的所述位线bl,写入0至与所述第一目标字线和若干条所述位线相连的预设数量的所述存储单元20中;自所述第一目标字线开启至延迟第一预设时间后,开启与若干条所述位线bl电连接的所述感应放大器;自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和与若干条所述位线bl电连接的所述感应放大器。接着,对所述第一目标字线第二次执行所述第二子循环步骤:第二次开启所述第一目标字线;开启所述存储阵列中与所述第一次执行所述第二子循环步骤中已开启过的所述位线bl相邻的下一预设数量的所述位线bl,写入0至与所述第一目标字线和下一预设数量所述位线相连的下一预设数量的所述存储单元20中;自所述第一目标字线开启至延迟第一预设时间后,开启与下一预设数量的所述位线bl电连接的所述感应放大器;自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和与下一预设数量的所述位线bl电连接的所述

感应放大器。以此类推,直至与所述第一目标字线相连的所有所述存储单元20中均写满0。

114.第二次执行所述第一循环步骤:选定位于所述存储阵列第二行的所述字线wl作为所述第一目标字线。接着,多次执行第二子循环步骤,使得与所述目标字线电连接的所有所述存储单元20均完成写入0的操作。其中,多次执行第二子循环步骤的具体操作与第一次执行所述第一循环步骤中多次执行第二子循环步骤的操作相同。

115.在另一些实施例中,所述第一循环步骤包括:

116.选定一条字线wl作为第一目标字线,并开启所述第一目标字线;

117.开启所有的所述位线,写入0至与所述第一目标字线相连的所有所述存储单元中;

118.自所述第一目标字线开启至延迟第一预设时间后,开启与所有的所述位线电连接的所述感应放大器;

119.自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和与所有的所述位线电连接的所述感应放大器,并以与所述第一目标字线相邻的下一条所述字线作为下一次第一循环步骤的第一目标字线。

120.附图5是本技术具体实施方式中第三种半导体结构的测试方法示意图。图5中的(a)和(b)操作与图3中的(a)和(b)操作相同,区别仅在于第一循环步骤(图5中的(c))与图3中的第一循环步骤(图3中的(c))不同。在图5所示的实施例中,进入测试模式之后,第一次执行所述第一循环步骤:选定位于所述存储阵列第一行的所述字线wl作为第一目标字线,并开启所述第一目标字线;开启所有的所述位线bl,写入0至与所述第一目标字线相连的所有所述存储单元20中;自所述第一目标字线开启至延迟第一预设时间后,开启与所有的所述位线bl电连接的所述感应放大器;自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和与所有的所述位线bl电连接的所述感应放大器。

121.第二次执行所述第一循环步骤:选定位于所述存储阵列第二行的所述字线wl作为第一目标字线,并开启所述第一目标字线;开启所有的所述位线bl,写入0至与所述第一目标字线相连的所有所述存储单元20中;自所述第一目标字线开启至延迟第一预设时间后,开启与所有的所述位线bl电连接的所述感应放大器;自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和与所有的所述位线bl电连接的所述感应放大器。以此类推,通过执行多次所述第一循环步骤,使得所述存储阵列中所有的所述字线wl均完成开启和关闭操作,以于所述存储阵列中写满0。

122.在一些实施例中,所述存储阵列的数量为多个;一个所述存储阵列中所有的所述存储单元均写满0之后,还包括如下步骤:

123.刷新已写满0的所述存储阵列;

124.对下一个所述存储阵列执行所述第一循环步骤,直至下一个所述存储阵列中所有的所述存储单元均写满0。

125.如图3、图4和图5所示,所述存储阵列的数量为多个,且多个所述存储阵列沿z轴方向平行排布。在一个所述存储阵列中所有的所述存储单元均写满0之后,退出测试模式(即图3中的(d)操作、图4中的(d)操作和图4中的(d)操作),并刷新已写满0的所述存储阵列(即图3中的(e)操作、图4中的(e)操作和图4中的(e)操作)。之后,再次进行所述测试模式,对下一个所述存储阵列执行所述第一循环步骤(图3中的(c)操作、图4中的(c)操作和图4中的(c)操作),直至下一个所述存储阵列中所有的所述存储单元均写满0。在下一个所述存储阵

列写满0之后,退出所述测试模式,并对于所述测试模式中写满0的所述存储阵列执行刷新操作。以此类推,直至多个所述存储阵列均通过多次所述第一循环步骤完成写满0的操作。

126.在一些实施例中,所述存储阵列中所有的所述存储单元20均写满0之后,还包括如下步骤:

127.读取所述存储阵列中所有的所述存储单元20(图3中的(f)操作、图4中的(f)操作和图4中的(f)操作);

128.判断所有所述存储单元20的读取值是否均为0,若否,则确认读取值不为0的所述存储单元20处的所述字线wl与所述位线bl电连接。

129.在一些实施例中,读取所述存储阵列中所有的所述存储单元20的具体步骤包括:

130.多次执行第三循环步骤,直至存储存储阵列中所有的所述存储单元20均被读取,所述第三循环步骤包括:

131.选定一条字线wl作为第三目标字线,并读取与所述第三目标字线相连的所有存储单元20;

132.与所述第三目标字线相连的所有存储单元20均被读取之后,以与所述第三目标字线相邻的下一条所述字线wl作为下一次第三循环步骤的第三目标字线。

133.举例来说,在所有的所述存储阵列均通过多次执行所述第一循环步骤完成写满0的操作会后,第一次执行所述第三循环步骤:选定位于一个所述存储阵列第一行的所述字线wl作为第三目标字线,并读取与所述目标字线相连的所有存储单元20。之后,第二次执行所述第三循环步骤:选定位于一个所述存储阵列第二行的所述字线wl作为第三目标字线,并读取与所述目标字线相连的所有存储单元20。依次类推,逐行读取,直至所有所述存储阵列中的所有所述存储单元20均被读取。

134.由于在写入操作中写入所述存储单元20的值为0,若所述字线wl与所述位线bl短接,则所述字线wl与所述位线bl短接产生的漏电流会传输至与所述位线bl电连接的电容器中。在读取操作时,所述电容器中的漏电流会传输至与发生短接的所述字线wl和所述位线bl均电连接的所述存储单元20中,进而使得该存储单元20的读取值变为1。因此,通过判断所有所述存储单元20的读取值是否均为0,即可确认所述存储单元20处的所述字线wl与所述位线bl是否短接。

135.根据另一些实施例,本具体实施方式还提供了一种半导体结构的测试装置。附图6是本技术具体实施方式中半导体结构的测试装置的结构框图。本具体实施方式提供的半导体结构的测试装置可以采用图1-图5所示的方法对半导体结构进行测试。如图1-图6所示,所述半导体结构的测试装置,包括:

136.写入模块61,用于多次执行如下第一循环步骤,直至存储阵列中所有的所述存储单元均写满0;所述存储阵列中包括呈阵列排布的多个存储单元、多条沿第一方向平行排布的字线、以及多条沿第二方向平行排布的位线,多条所述位线与多个感应放大器电连接,所述第一方向与所述第二方向相交;所述第一循环步骤包括:选定一条字线作为第一目标字线,并开启所述第一目标字线;自所述第一目标字线开启至延迟第一预设时间后,开启所述感应放大器;自所述第一目标字线开启至延迟第二预设时间后,关闭所述第一目标字线和所述感应放大器,并以与所述第一目标字线相邻的下一条所述字线作为下一次第一循环步骤的第一目标字线。

137.在一些实施例中,所述半导体结构的测试装置还包括:

138.刷新模块62,用于刷新已写满0的所述存储阵列。

139.在一些实施例中,还包括:

140.读取模块63,用于读取所述存储阵列中所有的所述存储单元;

141.判断模块64,用于判断所有所述存储单元的读取值是否均为0,若否,则确认所述存储阵列存在所述位线和所述字线短路的缺陷。

142.所述半导体结构的测试装置中还可以包括控制模块60,所述控制模块60连接所述写入模块61、所述刷新模块62、所述读取模块63和所述判断模块64,所述控制模块60可以为一上位机,用于接收用户的操作指令,并控制所述写入模块61、所述刷新模块62、所述读取模块63和所述判断模块64执行相应的操作。

143.本具体实施方式提供的半导体结构的测试方法及测试装置,于存储阵列的所有存储单元中均写满0,利用字线开启时的高电位与位线的低电位之间的产生的压差来模拟字线与位线之间短路的现象。本技术一些实施例在目标字线启动并延迟第一预设时间之后再开启感应放大器、且在所述目标字线启动并延迟第二预设时间之后再关闭所述目标字线,从而延长了从目标字线开启到感应放大器开启的时间以及所述目标字线处于激活状态的时间,从而使得一旦发生字线与位线之间的短路情况时,所述感应放大器能够充分检测到该缺陷,提高了字线与位线之间短路缺陷检测的准确度与检测效率。

144.以上所述仅是本技术的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本技术原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本技术的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1