测试电路及测试方法与流程

本公开涉及半导体,具体涉及一种测试电路及测试方法。

背景技术:

1、动态随机存取存储器(dynamic random access memory,dram)的作用原理是利用电容内存储电荷的多少来代表一个二进制比特是1还是0。电容的选中是通过与电容串联的晶体管控制的,而晶体管的选中则通过字线和位线来控制。

2、dram在字线的驱动过程中,由于产品缺陷,存在子字线控制信号短路的风险,将有缺陷的产品提早侦测出来,利于提高产品的可靠性。

技术实现思路

1、本公开实施例提供了一种测试电路及测试方法,能够提高存在短路风险的缺陷产品的检出率。

2、第一方面,本公开实施例提供了一种测试电路,包括:

3、第一信号端,用于接收第一电压;

4、第二信号端,用于接收第二电压,所述第二电压的电压值低于所述第一电压的电压值;

5、信号输出端,连接子字线驱动器的第一输入端;

6、控制端,用于接收测试信号;

7、基于所述测试信号的不同电平,所述信号输出端将所述第一电压或所述第二电压输出至所述第一输入端。

8、可选实施例中,所述测试电路包括:

9、第一开关电路,其具有第一控制端、第一电压输入端和第一电压输出端,所述第一电压输入端作为所述第一信号端;

10、反相器,其输入端与所述第一控制端连接,作为所述控制端;

11、第二开关电路,其具有第二控制端、第二电压输入端和第二电压输出端,所述第二控制端连接所述反相器的输出端,所述第二电压输入端作为所述第二信号端,所述第二电压输出端与所述第一电压输出端连接,作为所述信号输出端。

12、可选实施例中,所述第一开关电路包括第一nmos管,所述第一nmos管的栅极与所述反相器的输入端连接,作为控制端,所述第一nmos管的漏极作为所述第一信号端;所述第二开关电路包括第二nmos管,所述第二nmos管的栅极与所述反相器的输出端连接,所述第二nmos管的漏极作为所述第二信号端,所述第二nmos管的源极与所述第一nmos管的源极连接,作为所述信号输出端。

13、可选实施例中,所述第一开关电路包括第一pmos管,所述第一pmos管的栅极为第一控制端,漏极为第一信号端,源极为第一电压输出端;所述第二开关电路包括第二pmos管,所述第二pmos管的栅极与所述反相器的输出端连接,所述第二pmos管的漏极作为第二信号端,所述第二pmos管的源极与所述第一pmos管的源极连接,作为信号输出端。

14、可选实施例中,所述第一电压为0v,所述第二电压为-0.2~-0.5v。

15、可选实施例中,所述子字线驱动器还包括第二输入端、第三输入端、第四输入端和输出端;所述第二输入端用于接收字线驱动信号,所述第三输入端用于接收第一控制驱动信号,所述第四输入端用于接收第二控制驱动信号,所述第二控制驱动信号与所述第一控制驱动信号为互补信号,所述输出端用于连接字线。

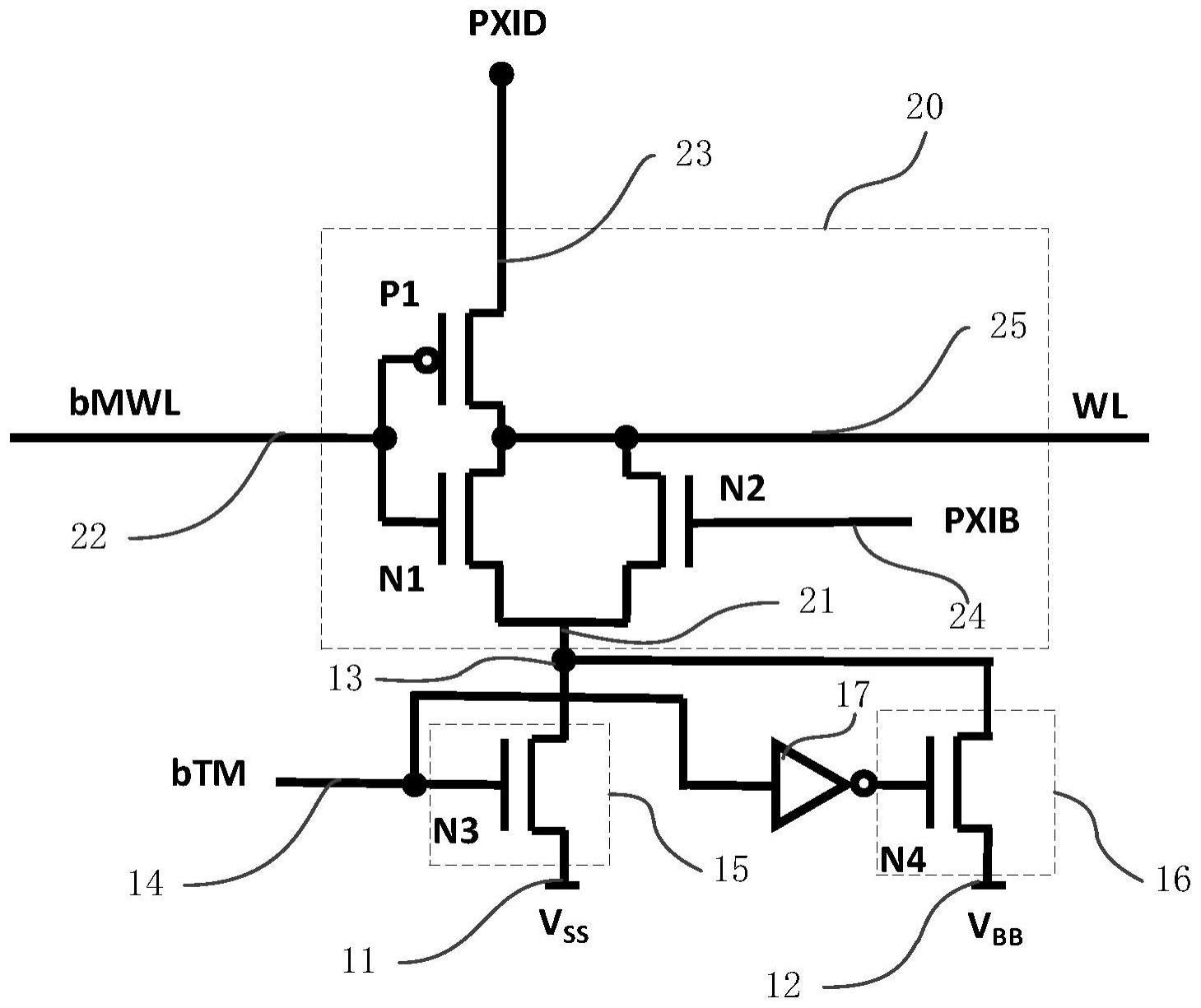

16、可选实施例中,所述子字线驱动器包括:第一驱动pmos管、第一驱动nmos管和第二驱动nmos管,所述第一驱动pmos管的栅极和第一驱动nmos管的栅极连接,作为所述第二输入端,所述第一驱动pmos管的源极作为第三输入端,所述第二驱动nmos管的栅极作为所述第三输入端,所述第一驱动nmos管的源极和所述第二驱动nmos管的源极连接,作为所述第一输入端,所述第一驱动pmos管的漏极、所述第一驱动nmos管的漏极和所述第二驱动nmos管的漏极连接,作为所述输出端。

17、可选实施例中,基于所述测试信号的不同电平,所述信号输出端将所述第一电压或所述第二电压输出至所述第一输入端,包括:

18、所述测试信号为高电平时,所述信号输出端将所述第一电压输出至所述第一输入端;

19、所述测试信号为低电平时,所述信号输出端将所述第二电压输出至所述第一输入端。

20、可选实施例中,所述测试信号基于测试模式生成,所述测试模式包括启动测试模式和未启动测试模式。

21、可选实施例中,所述第二电压的电压值基于测试条件确定。

22、第二方面,本公开实施例提供了一种测试方法,包括:

23、接收测试信号;

24、基于接收到的所述测试信号的不同电平,将第一电压或第二电压传输至子字线驱动器的第一输入端,所述第二电压的电压值低于所述第一电压的电压值。

25、可选实施例中,基于所述测试信号的不同电平,所述信号输出端将所述第一电压或所述第二电压输出至所述第一输入端,包括:

26、所述测试信号为高电平时,所述信号输出端将所述第一电压输出至所述第一输入端;

27、所述测试信号为低电平时,所述信号输出端将所述第二电压输出至所述第一输入端。

28、可选实施例中,所述测试信号基于测试模式生成,所述测试模式包括启动测试模式和未启动测试模式。

29、可选实施例中,所述第二电压的电压值基于测试条件确定。

30、可选实施例中,所述第一电压为0v,所述第二电压为-0.2~-0.5v。

31、本公开实施例提供一种测试电路,包括第一信号端、第二信号端、控制端和信号输出端,第一信号端和第二信号端分别用于接收电压值不同的第一电压和第二电压,第二电压的电压值低于第一电压的电压值;信号输出端连接子字线驱动器的第一输入端;基于控制端接收的测试信号的不同电平,信号输出端能够将第一电压或第二电压输出至所述第一输入端。通过将输入到子字线驱动器的第一输入端的电压由第一电压转换为电压值较低的第二电压,提高了子字线驱动器存在短路风险的控制信号之间的压差,更容易将有高风险短路问题的产品提前测试出来,提升产品良率。

技术特征:

1.一种测试电路,其特征在于,包括:

2.根据权利要求1所述的测试电路,其特征在于,所述测试电路包括:

3.根据权利要求2所述的测试电路,其特征在于,所述第一开关电路包括第一nmos管,所述第一nmos管的栅极与所述反相器的输入端连接,作为控制端,所述第一nmos管的漏极作为所述第一信号端;所述第二开关电路包括第二nmos管,所述第二nmos管的栅极与所述反相器的输出端连接,所述第二nmos管的漏极作为所述第二信号端,所述第二nmos管的源极与所述第一nmos管的源极连接,作为所述信号输出端。

4.根据权利要求2所述的测试电路,其特征在于,所述第一开关电路包括第一pmos管,所述第一pmos管的栅极为第一控制端,漏极为第一信号端,源极为第一电压输出端;所述第二开关电路包括第二pmos管,所述第二pmos管的栅极与所述反相器的输出端连接,所述第二pmos管的漏极作为第二信号端,所述第二pmos管的源极与所述第一pmos管的源极连接,作为信号输出端。

5.根据权利要求1所述的测试电路,其特征在于,所述第一电压为0v,所述第二电压为-0.2~-0.5v。

6.根据权利要求1所述的测试电路,其特征在于,所述子字线驱动器还包括第二输入端、第三输入端、第四输入端和输出端;所述第二输入端用于接收字线驱动信号,所述第三输入端用于接收第一控制驱动信号,所述第四输入端用于接收第二控制驱动信号,所述第二控制驱动信号与所述第一控制驱动信号为互补信号,所述输出端用于连接字线。

7.根据权利要求6所述的测试电路,其特征在于,所述子字线驱动器包括:第一驱动pmos管、第一驱动nmos管和第二驱动nmos管,所述第一驱动pmos管的栅极和第一驱动nmos管的栅极连接,作为所述第二输入端,所述第一驱动pmos管的源极作为第三输入端,所述第二驱动nmos管的栅极作为所述第三输入端,所述第一驱动nmos管的源极和所述第二驱动nmos管的源极连接,作为所述第一输入端,所述第一驱动pmos管的漏极、所述第一驱动nmos管的漏极和所述第二驱动nmos管的漏极连接,作为所述输出端。

8.根据权利要求1所述的测试电路,其特征在于,基于所述测试信号的不同电平,所述信号输出端将所述第一电压或所述第二电压输出至所述第一输入端,包括:

9.根据权利要求8所述的测试电路,其特征在于,所述测试信号基于测试模式生成,所述测试模式包括未启动测试模式和启动测试模式。

10.根据权利要求1所述的测试电路,其特征在于,所述第二电压的电压值基于测试条件确定。

11.一种测试方法,其特征在于,包括:

12.根据权利要求11所述的测试方法,其特征在于,基于所述测试信号的不同电平,信号输出端将所述第一电压或所述第二电压输出至所述第一输入端,包括:

13.根据权利要求12所述的测试方法,其特征在于,所述测试信号基于测试模式生成,所述测试模式包括启动测试模式和未启动测试模式。

14.根据权利要求11所述的测试方法,其特征在于,所述第二电压的电压值基于测试条件确定。

15.根据权利要求11所述的测试方法,其特征在于,所述第一电压为0v,所述第二电压为-0.2~-0.5v。

技术总结

本公开实施例公开了一种测试电路及测试方法。其中,测试电路包括:第一信号端,用于接收第一电压;第二信号端,用于接收第二电压,所述第二电压的电压值低于所述第一电压的电压值;信号输出端,连接子字线驱动器的第一输入端;控制端,用于接收测试信号;基于所述测试信号的不同电平,所述信号输出端将所述第一电压或所述第二电压输出至所述第一输入端。本公开实施例的测试电路能够提高存在短路风险的问题产品的检出率。

技术研发人员:杨正杰

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!