基于RRAM的EEPROM安全非易失存储器

基于rram的eeprom安全非易失存储器

技术领域

1.本发明涉及一种eeprom安全非易失存储器,尤其是涉及一种基于rram的eeprom安全非易失存储器。

背景技术:

2.eeprom是可以更改的只读存储器,它能够在高于普通电压的电压作用下擦除和重编程(即写入)。eeprom是一种特殊形式的闪存,其通常构成eeprom安全非易失存储器应用于计算机中,通过计算机的电压来擦除和重编程,由此计算机在使用的时候可频繁地反复编程。

3.当前eeprom安全非易失存储器规模较大,通常包括数量较多的eeprom单元电路。现有的单个eeprom单元电路结构图如图1所示。从图1中可以看出该eeprom单元电路通过4个nmos管n1、n2、n3和n4实现,其面积较大,由此导致采用该eeprom单元电路构成的eeprom安全非易失存储器面积较大。另外,由于eeprom的原理要求,nmos管n1为浮栅器件,其工艺很复杂,成本很高,同时eeprom的“擦除”与“写入”操作均需要高电压进行浮栅电子的注入或释放才能完成操作,由此导致配套电路结构复杂,以致eeprom安全非易失存储器工艺复杂、成本较高,整体电路结构复杂。

技术实现要素:

4.本发明所要解决的技术问题是提供一种面积较小、工艺简单、成本较低,整体电路结构简单的基于rram的eeprom安全非易失存储器。

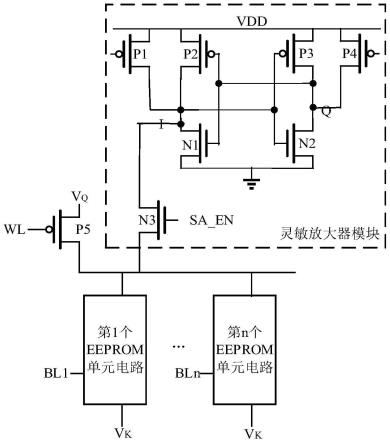

5.本发明解决上述技术问题所采用的技术方案为:一种基于rram的eeprom安全非易失存储器,包括字线wl、n个eeprom单元电路以及n条位线bl1-bln,n为大于等于2的整数,所述的eeprom安全非易失存储器还包括灵敏放大器模块和开关电路,所述的灵敏放大器模块包括第一pmos管、第二pmos管、第三pmos管、第四pmos管、第一nmos管、第二nmos管和第三nmos管,所述的第一pmos管的源极、所述的第二pmos管的源极、所述的第三pmos管的源极和所述的第四pmos管的源极均接入电源电压vdd,所述的第一pmos管的漏极、所述的第二pmos管的漏极、所述的第三pmos管的栅极、所述的第一nmos管的漏极、所述的第二nmos管的栅极和所述的第三nmos管的漏极连接,所述的第二pmos管的栅极、所述的第三pmos管的漏极、所述的第四pmos管的漏极、所述的第一nmos管的栅极和所述的第二nmos管的漏极连接,所述的第一nmos管的源极和所述的第二nmos管的源极均接地,所述的第三nmos管的栅极为所述的灵敏放大器模块的使能端,接入使能信号sa_en,所述的第三nmos管的源极为所述的灵敏放大器模块的输出端;所述的开关电路包括第五pmos管,所述的第五pmos管的栅极与所述的字线wl连接,所述的第五pmos管的源极为所述的开关电路的控制端,接入控制电压vq,所述的第五pmos管的漏极为所述的开关电路的输出端;每个所述的eeprom单元电路分别包括rram和第四nmos管,所述的rram由依次层叠的顶电极、氧化层和底电极组成,当所述的rram的顶电极和底电极之间没有加载电压时,由于所述的氧化层默认绝缘,此时所述的rram处

于高阻抗状态(hrs),当在所述的rram的顶电极和底电极之间加载电压,且该电压超过预设的阈值电压时,所述的氧化层形成导电丝,此时所述的rram处于低阻抗状态(lrs),当所述的rram处于低阻抗状态时,在所述的rram的顶电极和底电极之间加载反向电压,此时所述的rram将从lrs再次变为hrs,所述的rram的顶电极为所述的eeprom单元电路的输入端,所述的rram的底电极与所述的第四nmos管的漏极连接,所述的第四nmos管的栅极为所述的eeprom单元电路的位线端,所述的第四nmos管的源极为所述的eeprom单元电路的控制端;所述的灵敏放大器模块的输出端、所述的开关电路的输出端和n个eeprom单元电路的输入端连接,n个eeprom单元电路的控制端均接入控制电压vk,第m个eeprom单元电路的位线端和第m根位线blm连接,m=1,2,

…

,n;所述的eeprom安全非易失存储器具有编程模式和读取模式;在编程模式下,所述的eeprom安全非易失存储器通过控制字线wl和n条位线的开启与关闭,实现第五pmos管和第四nmos管的导通,进而将n位存储数据一一对应存储到n个eeprom单元电路中,其中,当第m条位线blm开启时,向第m个eeprom单元电路中存储数据,如果存储数据为“0”,控制电压vq=vdd,控制电压vk=0,第m个eeprom单元电路的rram处于lrs,如果存储数据为“1”,控制电压vq=0,控制电压vk=vdd,第m个eeprom单元电路的rram处于hrs;在读取模式下,所述的eeprom安全非易失存储器通过控制字线wl和n条位线来打开n个eeprom单元电路、关闭所述的第五pmos管以及开启所述的灵敏放大器模块,所述的灵敏放大器模块开启后,通过所述的第一pmos管和所述的第四pmos管先对节点i和节点q进行预充电,然后在n个eeprom单元电路的控制端施加为低脉冲电压的控制电压vk,当第m条位线blm开启时,从第m个eeprom单元电路中读取数据,由于存储数据是“0”还是“1”的不同,第m个eeprom单元电路中的rram的阻值会存在不同,所述的灵敏放大器模块的节点i处分到的电压也会存在不同,当第m个eeprom单元电路中存储数据为“0”时,所述的灵敏放大器模块的节点q恢复低电压,还原出存储数据“0”,当第m个eeprom单元电路中存储数据为“1”时,所述的灵敏放大器模块的节点q恢复出高电压,还原出存储数据“1”,此时对第m个eeprom单元电路的数据读取完成。

6.与现有技术相比,本发明的优点在于通过字线wl、n个eeprom单元电路n条位线bl1-bln、灵敏放大器模块以及开关电路构成基于rram的eeprom安全非易失存储器,灵敏放大器模块包括第一pmos管、第二pmos管、第三pmos管、第四pmos管、第一nmos管、第二nmos管和第三nmos管,第一pmos管的源极、第二pmos管的源极、第三pmos管的源极和第四pmos管的源极均接入电源电压vdd,第一pmos管的漏极、第二pmos管的漏极、第三pmos管的栅极、第一nmos管的漏极、第二nmos管的栅极和第三nmos管的漏极连接,第二pmos管的栅极、第三pmos管的漏极、第四pmos管的漏极、第一nmos管的栅极和第二nmos管的漏极连接,第一nmos管的源极和第二nmos管的源极均接地,第三nmos管的栅极为灵敏放大器模块的使能端,接入使能信号sa_en,第三nmos管的源极为灵敏放大器模块的输出端;开关电路包括第五pmos管,第五pmos管的栅极与字线wl连接,第五pmos管的源极为开关电路的控制端,接入控制电压vq,第五pmos管的漏极为开关电路的输出端;每个eeprom单元电路分别包括rram和第四nmos管,rram由依次层叠的顶电极、氧化层和底电极组成,当rram的顶电极和底电极之间没有加载电压时,由于氧化层默认绝缘,此时rram处于高阻抗状态(hrs),当在rram的顶电极和底电极之间加载电压,且该电压超过预设的阈值电压时,氧化层形成导电丝,此时rram处于低阻抗状态(lrs),当rram处于低阻抗状态时,在rram的顶电极和底电极之间加载反向电

压,此时rram将从lrs再次变为hrs,rram的顶电极为eeprom单元电路的输入端,rram的底电极与第四nmos管的漏极连接,第四nmos管的栅极为eeprom单元电路的位线端,第四nmos管的源极为eeprom单元电路的控制端;灵敏放大器模块的输出端、开关电路的输出端和n个eeprom单元电路的输入端连接,n个eeprom单元电路的控制端均接入控制电压vk,第m个eeprom单元电路的位线端和第m根位线blm连接,m=1,2,

…

,n;eeprom安全非易失存储器具有编程模式和读取模式;在编程模式下,eeprom安全非易失存储器通过控制字线wl和n条位线的开启与关闭,实现第五pmos管和第四nmos管的导通,进而将n位存储数据一一对应存储到n个eeprom单元电路中,其中,当第m条位线blm开启时,向第m个eeprom单元电路中存储数据,如果存储数据为“0”,控制电压vq=vdd,控制电压vk=0,第m个eeprom单元电路的rram处于lrs,如果存储数据为“1”,控制电压vq=0,控制电压vk=vdd,第m个eeprom单元电路的rram处于hrs;在读取模式下,eeprom安全非易失存储器通过控制字线wl和n条位线来打开n个eeprom单元电路、关闭第五pmos管以及开启灵敏放大器模块,灵敏放大器模块开启后,通过第一pmos管和第四pmos管先对节点i和节点q进行预充电,然后在n个eeprom单元电路的控制端施加为低脉冲电压的控制电压vk,当第m条位线blm开启时,从第m个eeprom单元电路中读取数据,由于存储数据是“0”还是“1”的不同,第m个eeprom单元电路中的rram的阻值会存在不同,灵敏放大器模块的节点i处分到的电压也会存在不同,当第m个eeprom单元电路中存储数据为“0”时,灵敏放大器模块的节点q恢复低电压,还原出存储数据“0”,当第m个eeprom单元电路中存储数据为“1”时,灵敏放大器模块的节点q恢复出高电压,还原出存储数据“1”,此时对第m个eeprom单元电路的数据读取完成,本发明中eeprom单元电路分别通过rram和一个nmos管(第四nmos管)实现,结构简单,面积较小,且采用rram实现的eeprom单元电路相对于现有的采用浮栅器件实现的eeprom单元电路,存取速度快,功耗极低,成本低,且操作简单,配套电路结构简单,由此本发明面积较小、工艺简单、成本较低,整体电路结构简单。

附图说明

7.图1为现有的eeprom单元电路的结构图;

8.图2为本发明的基于rram的eeprom安全非易失存储器的结构图;

9.图3为本发明的基于rram的eeprom安全非易失存储器的eeprom单元电路的结构图;

10.图4为为本发明的基于rram的eeprom安全非易失存储器的eeprom单元电路中rram的结构图。

具体实施方式

11.以下结合附图实施例对本发明作进一步详细描述。

12.实施例:如图2至图4所示,一种基于rram的eeprom安全非易失存储器,包括字线wl、n个eeprom单元电路以及n条位线bl1-bln,n为大于等于2的整数,eeprom安全非易失存储器还包括灵敏放大器模块和开关电路,灵敏放大器模块包括第一pmos管p1、第二pmos管p2、第三pmos管p3、第四pmos管p4、第一nmos管n1、第二nmos管n2和第三nmos管n3,第一pmos管p1的源极、第二pmos管p2的源极、第三pmos管p3的源极和第四pmos管p4的源极均接入电

源电压vdd,第一pmos管p1的漏极、第二pmos管p2的漏极、第三pmos管p3的栅极、第一nmos管n1的漏极、第二nmos管n2的栅极和第三nmos管n3的漏极连接,第二pmos管p2的栅极、第三pmos管p3的漏极、第四pmos管p4的漏极、第一nmos管n1的栅极和第二nmos管n2的漏极连接,第一nmos管n1的源极和第二nmos管n2的源极均接地,第三nmos管n3的栅极为灵敏放大器模块的使能端,接入使能信号sa_en,第三nmos管n3的源极为灵敏放大器模块的输出端;开关电路包括第五pmos管p5,第五pmos管p5的栅极与字线wl连接,第五pmos管p5的源极为开关电路的控制端,接入控制电压vq,第五pmos管p5的漏极为开关电路的输出端;每个eeprom单元电路分别包括rram r1和第四nmos管n4,rram r1由依次层叠的顶电极、氧化层和底电极组成,当rram r1的顶电极和底电极之间没有加载电压时,由于氧化层默认绝缘,此时rram r1处于高阻抗状态(hrs),当在rram r1的顶电极和底电极之间加载电压,且该电压超过预设的阈值电压时,氧化层形成导电丝,此时rram r1处于低阻抗状态(lrs),当rram r1处于低阻抗状态时,在rram r1的顶电极和底电极之间加载反向电压,此时rram r1将从lrs再次变为hrs,rram的顶电极为eeprom单元电路的输入端,rram r1的底电极与第四nmos管n4的漏极连接,第四nmos管n4的栅极为eeprom单元电路的位线端,第四nmos管n4的源极为eeprom单元电路的控制端;灵敏放大器模块的输出端、开关电路的输出端和n个eeprom单元电路的输入端连接,n个eeprom单元电路的控制端均接入控制电压vk,第m个eeprom单元电路的位线端和第m根位线blm连接,m=1,2,

…

,n;

13.eeprom安全非易失存储器具有编程模式和读取模式;在编程模式下,eeprom安全非易失存储器通过控制字线wl和n条位线的开启与关闭,实现第五pmos管p5和第四nmos管n4的导通,进而将n位存储数据一一对应存储到n个eeprom单元电路中,其中,当第m条位线blm开启时,向第m个eeprom单元电路中存储数据,如果存储数据为“0”,控制电压vq=vdd,控制电压vk=0,第m个eeprom单元电路的rram处于lrs,如果存储数据为“1”,控制电压vq=0,控制电压vk=vdd,第m个eeprom单元电路的rram处于hrs;在读取模式下,eeprom安全非易失存储器通过控制字线wl和n条位线来打开n个eeprom单元电路、关闭第五pmos管p5以及开启灵敏放大器模块,灵敏放大器模块开启后,通过第一pmos管p1和第四pmos管p4先对节点i和节点q进行预充电,然后在n个eeprom单元电路的控制端施加为低脉冲电压的控制电压vk,当第m条位线blm开启时,从第m个eeprom单元电路中读取数据,由于存储数据是“0”还是“1”的不同,第m个eeprom单元电路中的rram的阻值会存在不同,灵敏放大器模块的节点i处分到的电压也会存在不同,当第m个eeprom单元电路中存储数据为“0”时,灵敏放大器模块的节点q恢复低电压,还原出存储数据“0”,当第m个eeprom单元电路中存储数据为“1”时,灵敏放大器模块的节点q恢复出高电压,还原出存储数据“1”,此时对第m个eeprom单元电路的数据读取完成。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1