记忆体及其操作方法与流程

1.本揭示内容是关于一种记忆体及记忆体的操作方法。

背景技术:

2.记忆体通常用于储存数据。为了读取储存于记忆体中的数据,记忆体产生对应于储存在记忆体中的数据的信号。信号的电压位准对应于数据的位元值。数据的不同位元值对应于信号的不同电压位准。通过分析信号的电压位准,读取的数据的至少一部分能够是已知的。

技术实现要素:

3.本揭示内容包含一种包含记忆体装置、读取装置及反馈装置的记忆体。记忆体装置用以储存多个位元。读取装置包含第一读取电路及第二读取电路。第一读取电路耦接至记忆体装置。第二读取电路耦接至记忆体装置,且在第一节点处耦接至第一读取电路。第一读取电路及第二读取电路用以彼此协作以基于多个位元中的至少一个第一位元来在第一节点处产生第一电压信号。反馈装置用以基于第一电压信号来调整第一读取电路及第二读取电路中的至少一者。第一读取电路及第二读取电路用以在第一读取电路及第二读取电路中的至少一者由反馈装置调整之后产生对应于多个位元的第二电压信号,第二电压信号与第一电压信号不同。

4.本揭示内容包含一种包含记忆体装置、读取装置、读出装置及反馈装置的记忆体。读取装置耦接至记忆体装置,且用以读取储存于记忆体装置中的数据以产生第一电压信号,第一电压信号对应于第一电压分布曲线。读出装置用以读出第一电压信号且用以产生多个数字信号,数字信号对应于所读出的第一电压信号。反馈装置用以回应于数字信号而产生至少一个控制信号,以用于控制读取装置产生第二电压信号,第二电压信号对应于与第一电压分布曲线不同的第二电压分布曲线。

5.本揭示内容包含一种记忆体的操作方法,包含:由互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)电路产生与储存于记忆体装置中的数据相关联的第一电压信号,其中第一电压信号的电压位准对应于第一电压分布曲线;读出第一电压信号以产生与数据的至少一个第一位元相关联的数字信号;及根据数字信号控制cmos电路产生第二电压信号,其中第二电压信号对应于数据,且第二电压信号的电压位准对应于第二电压分布曲线,第二电压分布曲线具有与第一电压分布曲线的移位或具有与第一电压分布曲线不同的轮廓。

附图说明

6.在结合随附附图阅读以下详细描述时可最佳地理解本揭示内容的各个态样。应注意,根据业界的标准惯例,各种特征并未按比例绘制。实际上,各种特征的尺寸可出于讨论的清晰起见而任意地增大或减小。

7.图1为根据本揭示内容的一些实施例的记忆体的示意图;

8.图2为表示根据本揭示内容的一些实施例的电压信号的电压位准与图1中所示出的数据的位元值之间的关系的电压分布曲线的图;

9.图3a为根据本揭示内容的一些实施例的对应于图1中所示出的记忆体的记忆体的电路图;

10.图3b为根据本揭示内容的一些实施例的对应于图3a中所示出的逻辑单元的逻辑单元的电路图;

11.图4为根据本揭示内容的一些实施例的对应于图1中所示出的记忆体的记忆体的电路图;

12.图5为根据本揭示内容的一些实施例的图1、图3a及图4中所示出的记忆体产生电压信号的方法的流程图;

13.图6a及图6b为表示根据本揭示内容的一些实施例的电压信号的电压位准与图4中所示出的数据的位元值之间的关系的电压分布曲线的图;

14.图6c及图6d为表示根据本揭示内容的一些实施例的电压信号的电压位准与图4中所示出的数据的位元值之间的关系的电压分布曲线的图。

15.【符号说明】

16.100、300、400:记忆体

17.110、310、410:记忆体装置

18.120、320、420:读取装置

19.122、124、322、324、422、424:读取电路

20.130、330、430:读出装置

21.140、340、440:反馈装置

22.200、600a、600b、600c、600d:图

23.301、342、344、442、444、446、448:逻辑单元

24.500:方法

具体实施方式

25.以下揭示内容提供了用于实施所提供主题的不同特征的许多不同实施例或实例。下面描述元件、材料、值、步骤、配置或类似者的具体实例以简化本揭示内容。当然,这些仅仅为实例并且不意欲作为限制。考虑了其他元件、材料、值、步骤、配置或类似者。举例而言,在以下描述中,在第二特征上方或第二特征上形成第一特征可包含第一特征及第二特征直接接触地形成的实施例,且也可包含可在第一特征与第二特征之间形成有附加特征以使得第一特征及第二特征可不直接接触的实施例。此外,本揭示内容可在各种实例中重复附图标记及/或字母。此重复是出于简单及清晰的目的,且本身并不指示所论述的各种实施例及/或组态之间的关系。

26.另外,为易于描述,在本文中可使用诸如“在

……

之下”、“下方”、“下部”、“上方”、“上部”及类似者的空间相对术语来描述如图中所说明的一个部件或特征与另一部件或特征的关系。除了图中所描绘的定向之外,空间相对术语亦意欲涵盖装置在使用或操作中的不同定向。装置可以其他方式定向(旋转90度或处于其他定向),且本文中所使用的空间相

对描述词可同样相应地进行解译。术语遮罩、光刻遮罩、光罩及倍缩光罩用于指相同项。

27.贯穿以下描述及申请专利范围应用的术语通常具有这些术语在所属领域中或使用每一术语的具体上下文中明确建立的普通含义。熟悉此项技术者应了解,元件或工艺可由不同名称提及。本说明书中详述的许多不同实施例仅仅为说明性的,且不以任何方式限制本揭示内容或任何例示性术语的范畴及精神。

28.值得注意的是,本文中用于描述各种部件或工艺的诸如“第一”及“第二”的术语旨在将一个部件或工艺与另一部件或工艺区分开。然而,其部件、工艺及序列应受这些术语的限制。举例而言,在不脱离本揭示内容的范畴的情况下,第一部件可被称作第二部件,且第二部件可类似地被称作第一部件。

29.在以下论述及申请专利范围中,术语“包括”、“包含”、“含有”、“具有”、“涉及”及类似者应被理解为开放式的,亦即,应被解释为包含但不限于。如本文中所使用,并非相互排斥,而是术语“及/或”包含相关联的所列项中的任一者及相关联的所列项中的一者或多者的所有组合。

30.图1为根据本揭示内容的一些实施例的记忆体100的示意图。如图1中说明性地示出,记忆体100包含记忆体装置110、读取装置120、读出装置130及反馈装置140。在一些实施例中,记忆体装置110实施为相变随机存取记忆体(phase change random access memory,pcram)。在一些实施例中,读取装置120实施为互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)电路。在一些实施例中,读出装置130实施为电流读出放大器(sensing amplifier,sa)。

31.在一些实施例中,记忆体装置110用以储存包含多个位元的数据dt,且用以接收电压信号vss。数据dt在各种实施例中具有各种位元值。读取装置120用以读取数据dt以产生对应于数据dt的电压信号vs1。读出装置130用以基于电压信号vs1来产生数字信号en。反馈装置140用以基于数字信号en来产生控制信号s11及s12,以控制读取装置120产生电压信号vs2。电压信号vs2也对应于数据dt。

32.如图1中说明性地示出,读取装置120包含读取电路122及124。读取电路122用以在节点n13处接收与电压信号vss不同的电压信号vdd且耦接至节点n11。在一些实施例中,电压信号vdd具有电源电压位准,且电压信号vss具有接地电压位准。

33.如图1中说明性地示出,读取电路124在节点n11处耦接至读取电路122,且在节点n12处耦接至记忆体装置110。在一些实施例中,读取电路122及124分别对应于两种晶体管类型。举例而言,读取电路122包含p型金属氧化物半导体(p-type metal-oxide-semiconductor,pmos)晶体管,且读取电路124包含n型金属氧化物半导体(n-type metal-oxide-semiconductor,nmos)晶体管。

34.在一些实施例中,读取电路122及124用以彼此协作以基于数据dt来在节点n11处产生电压信号vs1及vs2。如图1中说明性地示出,读取电路122及124在节点n12与n13之间串联耦接。在一些实施例中,电压信号vs1及vs2取决于读取电路122及124的电阻。举例而言,当读取电路122的电阻增加及/或读取电路124的电阻减小时,电压信号vs1及vs2的电压位准减小。相比之下,当读取电路122的电阻减小及/或读取电路124的电阻增加时,电压信号vs1及vs2的电压位准增加。

35.在一些实施例中,读取电路122及124用以产生电压信号vmsb,电压信号vmsb为电

压信号vs1的实施例。电压信号vmsb对应于数据dt的至少一个位元,诸如一或多个最高有效位元(most significant bit,msb)。

36.在一些实施例中,读出装置130用以基于电压信号vmsb来产生数字信号en。在一些实施例中,反馈装置140用以基于数字信号en,调整读取电路122及124中的至少一者的电阻以产生电压信号vs2,电压信号vs2具有至少部分地与电压信号vs1的电压位准不同的电压位准。

37.举例而言,回应于电压信号vmsb具有第一位元值,反馈装置140通过控制信号s12调整读取电路122,且回应于电压信号vmsb具有与第一位元值不同的第二位元值,反馈装置140通过控制信号s11调整读取电路124。

38.在一些实施例中,在读取电路122及124中的至少一者由反馈装置140调整之后,读取电路122及124产生电压信号vs2。换言之,电压信号vs2为电压信号vs1的调整版本。

39.图2为表示根据本揭示内容的一些实施例的电压信号vs1、vs2的电压位准与图1中所示出的数据dt的位元值之间的关系的电压分布曲线的图200。如图2中说明性地示出,图200包含水平轴及垂直轴。参看图1及图2,水平轴对应于数据dt的位元值,垂直轴对应于节点n11的电压位准或电压信号vs1及vs2的电压位准。在一些实施例中,数据dt的位元值被称为数据dt的乘积累加(multiply accumulate,mac)值。

40.如图2中说明性地示出,图200进一步包含电压分布曲线c21~c23。电压分布曲线c21对应于电压信号vs1与数据dt之间的关系。举例而言,回应于数据dt具有位元值pb,电压信号vs1具有电压位准vpb1。类似地,回应于数据dt具有位元值b11~b14,电压信号vs1分别具有对应于位元值b11~b14的电压位准v11~v14。在图2中所示出的实施例中,位元值b11及b12小于位元值pb,且位元值b13及b14大于位元值pb。在一些实施例中,位元值pb为预定位元值。在一些实施例中,位元值b11及b12为两个相邻位元值,且位元值b13及b14为两个相邻位元值。举例而言,位元值b11等于位元值b12减一,且位元值b14等于位元值b13加一。

41.如上面在图1中所示出的实施例中所描述,反馈装置140回应于数据dt的不同位元值而以不同方式调整电压信号vs1,以产生电压信号vs2。参看图1及图2,回应于数据dt的位元值小于位元值pb,电压信号vs1沿着箭头a21调整,以产生对应于电压分布曲线c22的电压信号vs2。换言之,电压分布曲线c22具有从电压分布曲线c21沿着箭头a21的移位,或具有与电压分布曲线c21不同的轮廓。

42.参看图2中所示出的电压分布曲线c22,回应于数据dt具有位元值b11及b12,电压信号vs2分别具有电压位准v21及v22。如图2中说明性地示出,电压位准v21小于电压位准v11,且电压位准v22小于电压位准v12。在一些实施例中,电压位准v21与v22之间的电压位准差大于电压位准v11与v12之间的电压位准差。

43.类似地,回应于数据dt的位元值大于位元值pb,电压信号vs1单独箭头a22调整,以产生对应于电压分布曲线c23的电压信号vs2。

44.参看图2中所示出的电压分布曲线c23,回应于数据dt具有位元值b13及b14,电压信号vs2分别具有电压位准v33及v34。如图2中说明性地示出,电压位准v33大于电压位准v13,且电压位准v34大于电压位准v14。在一些实施例中,电压位准v33与v34之间的电压位准差大于电压位准v13与v14之间的电压位准差。

45.在一些实施例中,回应于数据dt具有不同位元值,读取装置120用以产生多个电压

信号vs1及多个电压信号vs2。举例而言,电压信号vs1中的一者对应于位元值pb且具有电压位准vpb1。又举例而言,电压信号vs2中的一者对应于位元值b11且具有电压位准v21。

46.参看图1及图2,箭头a21及a22分别对应于控制信号s11及s12。在一些实施例中,回应于数据dt的位元值大于位元值pb,反馈装置140用以通过控制信号s12调整读取电路122,使得调整后的读取电路122及读取电路124协作以产生对应于电压分布曲线c23的电压信号vs2。在一些实施例中,回应于数据dt的位元值小于位元值pb,反馈装置140用以通过控制信号s11调整读取电路124,使得读取电路122及调整后的读取电路124协作以产生对应于电压分布曲线c22的电压信号vs2。

47.在一些方法中,读取装置基于储存于记忆体装置中的数据的位元值来产生电压信号。然而,电压信号的电压位准接近于对应于相邻位元值的另一电压位准。因此,很难基于电压信号来将位元值与相邻位元值区分开,且无法很好地读取或识别数据。

48.与以上方法相比,在本揭示内容的一些实施例中,基于数据dt的位元值来产生电压信号vs2。电压分布曲线对应于数据dt的位元值进行最佳化,使得对应于位元值(例如位元值b11)的电压位准(例如电压位准v21)与对应于相邻位元值(例如位元值b12)的电压位准(例如电压位准v22)之间的电压位准差增加。因此,当数据dt具有位元值b11时,很容易基于电压信号vs2将位元值b11与位元值b12区分开。

49.图3a为根据本揭示内容的一些实施例的对应于图1中所示出的记忆体100的记忆体300的电路图。如图3a中说明性地示出,记忆体300包含记忆体装置310、读取装置320、读出装置330及反馈装置340。参看图1及图3a,记忆体300为记忆体100的实施例。记忆体装置310、读取装置320、读出装置330及反馈装置340分别对应于记忆体装置110、读取装置120、读出装置130及反馈装置140。因此,出于简洁起见不再重复一些描述。

50.如图3a中说明性地示出,记忆体装置110包含多个记忆体单元mu1~mun。应注意,n为正整数。记忆体单元mu1~mun的第一端在节点n32处耦接至读取装置,记忆体单元mu1~mun的第二端用以在节点n33处接收电压信号vss。换言之,记忆体单元mu1~mun并联耦接在节点n32与n33之间。在一些实施例中,记忆体单元mu1~mun中的每一者用以储存数据dt的一或多个对应位元。举例而言,记忆体单元mu1储存数据dt的至少一个msb。

51.在一些实施例中,记忆体单元mu1~mun中的每一者包含相变部件pce及开关mus。如图3a中说明性地示出,相变部件pce及开关mus串联耦接在节点n32与n33之间。

52.在一些实施例中,读取装置320包含读取电路322及324。参看图1及图3a,读取电路322及324为读取电路122及124的实施例。因此,出于简洁起见不再重复一些描述。

53.如图3a中说明性地示出,读取电路322用以在节点n34处接收电压信号vdd,且读取电路324耦接至节点n32。在一些实施例中,读取电路322及324用以彼此协作以在节点n31处产生电压信号vs1、vs2及vmsb。

54.如图3a中说明性地示出,读取电路322包含晶体管p31~p33及开关tm1。在一些实施例中,晶体管p31~p33实施为pmos晶体管,且开关tm1实施为传输门。

55.如图3a中说明性地示出,晶体管p31的一端耦接至节点n34,晶体管p31的另一端耦接至节点n31。晶体管p32的一端耦接至节点n34,晶体管p32的另一端耦接至节点n31,晶体管p32的控制端用以接收致能电压信号vp。晶体管p33的一端用以接收电压信号vdd,晶体管p33的另一端在节点n35处耦接至晶体管p31的控制端,晶体管p33的控制端用以接收控制信

号s31b。开关tm1的一端耦接至节点n35,开关tm1的另一端用以接收致能电压信号vp,开关tm1的控制端用以接收控制信号s31b,开关tm1的另一控制端用以接收控制信号s31。在一些实施例中,控制信号s31与控制信号s31b互补。

56.在一些实施例中,晶体管p33的控制端与开关tm1的接收控制信号s31b的控制端为不同的类型。因此,晶体管p33在开关tm1导通时关断,而晶体管p33在开关tm1关断时导通。

57.在一些实施例中,当控制信号s31具有第一电压位准时,开关tm1导通以将致能电压信号vp传输至节点n35,使得晶体管p31导通。在一些实施例中,第一电压位准为p型晶体管的致能电压位准,且为n型晶体管的禁用电压位准。当控制信号s31b具有第一电压位准时,晶体管p33导通以将具有禁用电压位准的电压信号vdd传输至节点n35,使得晶体管p31关断。换言之,晶体管p31由控制信号s31及s31b控制。用于控制晶体管p31的实施例不限于图3a中所示出的组态,用于基于控制信号s31及s31b来控制晶体管p31的其他组态被认为在本揭示内容的范畴内。

58.如图3a中说明性地示出,读取电路324包含晶体管m31~m33及开关tm2。在一些实施例中,晶体管m31~m33实施为nmos晶体管,且开关tm2实施为传输门。

59.如图3a中说明性地示出,晶体管m31的一端耦接至节点n32,晶体管m31的另一端耦接至节点n31。晶体管m32的一端耦接至节点n32,晶体管m32的另一端耦接至节点n31,晶体管m32的控制端用以接收致能电压信号vn。晶体管m33的一端用以接收电压信号vss,晶体管m33的另一端在节点n36处耦接至晶体管m31的控制端,晶体管m33的控制端用以接收控制信号s32。开关tm2的一端耦接至节点n36,开关tm2的另一端用以接收致能电压信号vn,开关tm2的控制端用以接收控制信号s32b,且开关tm2的另一控制端用以接收控制信号s32。

60.在一些实施例中,晶体管m33的控制端与开关tm2的接收控制信号s32的控制端为不同的类型。因此,晶体管m33在开关tm2导通时关断,而晶体管m33在开关tm2关断时导通。

61.在一些实施例中,当控制信号s32b具有第二电压位准时,开关tm2导通以将致能电压信号vn传输至节点n36,使得晶体管m31导通。在一些实施例中,第二电压位准为n型晶体管的致能电压位准,且为p型晶体管的禁用电压位准。当控制信号s32具有第二电压位准时,晶体管m33导通以将具有禁用电压位准的电压信号vss传输至节点n36,使得晶体管m31关断。换言之,晶体管m31由控制信号s32及s32b控制。用于控制晶体管m31的实施例不限于图3a中所示出的组态,用于基于控制信号s32及s32b来控制晶体管m31的其他组态被认为在本揭示内容的范畴内。

62.在一些实施例中,当晶体管p31及m31关断时,晶体管p32及m32用以基于数据dt来产生电压信号vs1。电压信号vs1的电压位准取决于晶体管p32及m32的电阻。当晶体管p31导通且晶体管m31关断时,晶体管p31、p32及m32用以基于数据dt来产生电压信号vs2。晶体管p31及p32并联耦接在节点n34与n31之间,使得节点n34与n31之间的电阻与晶体管p31关断的情况相比减小。因此,电压信号vs2的电压位准高于电压信号vs1的电压位准。参看图3a及图2,电压分布曲线c23对应于晶体管p31导通的情况。

63.类似地,当晶体管m31导通且晶体管p31关断时,晶体管m31、p32及m32用以基于数据dt来产生电压信号vs2。晶体管m31及m32并联耦接在节点n32与n31之间,使得节点n32与n31之间的电阻与晶体管m31关断的情况相比减小。因此,电压信号vs2的电压位准低于电压信号vs1的电压位准。参看图3a及图2,电压分布曲线c22对应于晶体管m31导通的情况。

64.如图3a中说明性地示出,读出装置330用以读出电压信号vmsb以产生数字信号en0及en1。在图3a中所示出的实施例中,电压信号vmsb承载数据dt的msb。msb具有位元值0或1。回应于msb具有位元值0,数字信号en0具有位元值1且数字信号en1具有位元值0。回应于msb具有位元值1,数字信号en0具有位元值0且数字信号en1具有位元值1。

65.参看图3a及图2,当msb具有位元值1时,数据dt的位元值大于位元值pb,而当msb具有位元值0时,数据dt的位元值小于位元值pb。因此,反馈装置340在msb具有位元值0时沿着箭头a21调整电压信号vs1,且在msb具有位元值1时沿着箭头a22调整电压信号vs1。

66.如图3a中说明性地示出,反馈装置340包含逻辑单元342及344。逻辑单元342用以基于数字信号en1及电压信号vss来产生控制信号s31及s31b。逻辑单元344用以基于数字信号en0及电压信号vss来产生控制信号s32及s32b。在一些实施例中,电压信号vss具有位元值0。参看图3a及图1,控制信号s31及s31b为控制信号s12的实施例,且控制信号s32及s32b为控制信号s11的实施例。

67.如图3a中说明性地示出,逻辑单元342包含或非门nr31及反相器(inverter)in31。或非门nr31的两个输入端用以分别接收数字信号en1及电压信号vss。或非门nr31的输出端用以输出控制信号s31。反相器in31的输入端用以接收控制信号s31。反相器in31的输出端用以输出控制信号s31b。因此,控制信号s31在数字信号en1具有位元值1时具有第一电压位准以导通开关tm1。

68.如图3a中说明性地示出,逻辑单元344包含或非门nr32及反相器in32。或非门nr32的两个输入端用以分别接收数字信号en0及电压信号vss。或非门nr32的输出端用以输出控制信号s32。反相器in32的输入端用以接收控制信号s32。反相器in32的输出端用以输出控制信号s31b。因此,控制信号s32在数字信号en0具有位元值1时具有第一电压位准以导通开关tm2。

69.在各种实施例中,逻辑单元342及344具有各种组态且包含各种逻辑部件。举例而言,在一些替代实施例中,逻辑单元342及/或344具有与图3b中所示出的逻辑单元301类似的组态。

70.图3b为根据本揭示内容的一些实施例的对应于图3a中所示出的逻辑单元342及344的逻辑单元301的电路图。如图3b中说明性地示出,逻辑单元301包含或门rb及反相器inb。

71.在一些实施例中,逻辑单元342具有与逻辑单元301类似的组态。在此类实施例中,或门rb的两个输入端用以分别接收数字信号en1及电压信号vss。或门rb的输出端用以输出控制信号s31b。反相器inb的输入端用以接收控制信号s31b。反相器inb的输出端用以输出控制信号s31。

72.类似地,在一些实施例中,逻辑单元344具有与逻辑单元301类似的组态。在此类实施例中,或门rb的两个输入端用以分别接收数字信号en0及电压信号vss。或门rb的输出端用以输出控制信号s32b。反相器inb的输入端用以接收控制信号s32b。反相器inb的输出端用以输出控制信号s32。

73.图4为根据本揭示内容的一些实施例的对应于图1中所示出的记忆体100的记忆体400的电路图。如图4中说明性地示出,记忆体400包含记忆体装置410、读取装置420、读出装置430及反馈装置440。参看图1、图3a及图4,记忆体400为记忆体100的实施例且为记忆体

300的替代实施例。记忆体装置410、读取装置420、读出装置430及反馈装置440分别对应于记忆体装置310、读取装置320、读出装置330及反馈装置340。因此,出于简洁起见不再重复一些描述。

74.如图4中说明性地示出,记忆体装置410用以接收电压信号vss且耦接至节点n42。读取装置420包含读取电路422及424。参看图4及图3a,读取电路422及424为读取电路322及324的替代实施例。因此,出于简洁起见不再重复一些描述。

75.如图4中说明性地示出,读取电路422用以在节点n44处接收电压信号vdd,且读取电路424耦接至节点n42。在一些实施例中,读取电路422及424用以彼此协作以在节点n41处产生电压信号vs1、vs2及vmsb。

76.如图4中说明性地示出,读取电路422包含晶体管p41~p46及开关tg1、tg2。在一些实施例中,晶体管p41~p46实施为pmos晶体管,且开关tg1、tg2实施为传输门。

77.如图4中说明性地示出,晶体管p41~p44的第一端耦接至节点n44,晶体管p41~p44的第二端耦接至节点n41。换言之,晶体管p41~p44并联耦接在节点n41与n44之间。晶体管p43~p44的控制端用以接收致能电压信号vp。

78.如图4中说明性地示出,晶体管p45的一端用以接收电压信号vdd,晶体管p45的另一端在节点n45处耦接至晶体管p41的控制端,晶体管p45的控制端用以接收控制信号s41b。开关tg1的一端耦接至节点n45,开关tg1的另一端用以接收致能电压信号vp,开关tg1的控制端用以接收控制信号s41b,且开关tg1的另一控制端用以接收控制信号s41。在一些实施例中,控制信号s41与控制信号s41b互补。

79.如图4中说明性地示出,晶体管p46的一端用以接收电压信号vdd,晶体管p46的另一端在节点n46处耦接至晶体管p42的控制端,晶体管p46的控制端用以接收控制信号s42b。开关tg2的一端耦接至节点n46,开关tg2的另一端用以接收致能电压信号vp,开关tg2的控制端用以接收控制信号s42b,且开关tg2的另一控制端用以接收控制信号s42。在一些实施例中,控制信号s42与控制信号s42b互补。

80.晶体管p41、p45及开关tg1基于控制信号s41及s41b的操作与晶体管p31、p33及开关tm1基于图3a中所示出的控制信号s31及s31b的操作类似。晶体管p42、p46及开关tg2基于控制信号s42及s42b的操作与晶体管p31、p33及开关tm1基于图3a中所示出的控制信号s31及s31b的操作类似。因此,出于简洁起见不再重复一些描述。

81.如图4中说明性地示出,读取电路424包含晶体管m41~m47及开关tg3~tg5。在一些实施例中,晶体管m41~m47实施为nmos晶体管,且开关tg3~tg5实施为传输门。

82.如图4中说明性地示出,晶体管m41~m44的第一端耦接至节点n42,晶体管m41~m44的第二端耦接至节点n41。换言之,晶体管m41~m44并联耦接在节点n41与n42之间。晶体管m44的控制端用以接收致能电压信号vn。

83.如图4中说明性地示出,晶体管m45的一端用以接收电压信号vss,晶体管m45的另一端在节点n47处耦接至晶体管m41的控制端,晶体管m45的控制端用以接收控制信号s44。开关tg3的一端耦接至节点n47,开关tg3的另一端用以接收致能电压信号vn,开关tg3的控制端用以接收控制信号s44b,且开关tg3的另一控制端用以接收控制信号s44。在一些实施例中,控制信号s44与控制信号s44b互补。

84.如图4中说明性地示出,晶体管m46的一端用以接收电压信号vss,晶体管m46的另

一端在节点n48处耦接至晶体管m42的控制端,晶体管m46的控制端用以接收控制信号s43。开关tg4的一端耦接至节点n48,开关tg4的另一端用以接收致能电压信号vn,开关tg4的控制端用以接收控制信号s43,开关tg4的另一控制端用以接收控制信号s43b。在一些实施例中,控制信号s43与控制信号s43b互补。

85.如图4中说明性地示出,晶体管m47的一端用以接收电压信号vss,晶体管m47的另一端在节点n49处耦接至晶体管m43的控制端,晶体管m47的控制端用以接收控制信号s43。开关tg5的一端耦接至节点n49,开关tg5的另一端用以接收致能电压信号vn,开关tg5的控制端用以接收控制信号s43,且开关tg5的另一控制端用以接收控制信号s43b。

86.晶体管m41、m45及开关tg3基于控制信号s44及s44b的操作与晶体管m31、m33及开关tm2基于图3a中所示出的控制信号s32及s32b的操作类似。晶体管m42、m46及开关tg4基于控制信号s43及s43b的操作与晶体管m31、m33及开关tm2基于图3a中所示出的控制信号s32及s32b的操作类似。晶体管m43、m47及开关tg5基于控制信号s43及s43b的操作与晶体管m31、m33及开关tm2基于图3a中所示出的控制信号s32及s32b的操作类似。因此,出于简洁起见不再重复一些描述。

87.在各种实施例中,读取电路422及424中的每一者根据晶体管的电特征及读取电路422及424的规格包含各种数目的晶体管。

88.如图4中说明性地示出,读出装置430用以读出电压信号vmsb以产生数字信号en00、en01、en10及en11。在图4中所示出的实施例中,电压信号vmsb承载数据dt的两个msb。两个msb中的每一者具有位元值0或1。两个msb具有位元值00、01、10或11。回应于两个msb具有位元值00,数字信号en00具有位元值1,且数字信号en01、en10及en11中的每一者具有位元值0。回应于msb具有位元值01,数字信号en01具有位元值1,且数字信号en00、en10及en11中的每一者具有位元值0。回应于msb具有位元值10,数字信号en10具有位元值1,且数字信号en00、en01及en11中的每一者具有位元值0。回应于msb具有位元值11,数字信号en11具有位元值1,且数字信号en00、en10及en01中的每一者具有位元值0。

89.参看图4及图2,当两个msb具有位元值11或10时,数据dt的位元值大于位元值pb,而当两个msb具有位元值00或01时,数据dt的位元值小于位元值pb。因此,反馈装置440在两个msb具有位元值00或01时沿着箭头a21调整电压信号vs1,且在两个msb具有位元值11或10时沿着箭头a22调整电压信号vs1。

90.如图4中说明性地示出,反馈装置440包含逻辑单元442、444、446及448。逻辑单元442用以基于数字信号en11及电压信号vss来产生控制信号s41及s41b。逻辑单元444用以基于数字信号en00及电压信号vss来产生控制信号s44及s44b。在一些实施例中,电压信号vss具有位元值0。如图4中说明性地示出,逻辑单元446用以基于数字信号en11及en10来产生控制信号s42及s42b。逻辑单元448用以基于数字信号en00及en01来产生控制信号s43及s43b。参看图4及图1,控制信号s41、s41b、s42及s42b为控制信号s12的实施例,且控制信号s43、s43b、s44及s44b为控制信号s11的实施例。

91.如图4中说明性地示出,逻辑单元442包含或非门nr41及反相器in41。或非门nr41的两个输入端用以分别接收数字信号en11及电压信号vss。或非门nr41的输出端用以输出控制信号s41。反相器in41的输入端用以接收控制信号s41。反相器in41的输出端用以输出控制信号s41b。因此,控制信号s41在数字信号en11具有位元值1时具有第一电压位准以导

通开关tg1。

92.如图4中说明性地示出,逻辑单元444包含或非门nr44及反相器in44。或非门nr44的两个输入端用以分别接收数字信号en00及电压信号vss。或非门nr44的输出端用以输出控制信号s44。反相器in44的输入端用以接收控制信号s44。反相器in44的输出端用以输出控制信号s44b。因此,控制信号s44在数字信号en00具有位元值1时具有第一电压位准以导通开关tg3。

93.如图4中说明性地示出,逻辑单元446包含或非门nr42及反相器in42。或非门nr42的两个输入端用以分别接收数字信号en11及en10。或非门nr42的输出端用以输出控制信号s42。反相器in42的输入端用以接收控制信号s42。反相器in42的输出端用以输出控制信号s42b。因此,控制信号s42在数字信号en11及en10中的一者具有位元值1时具有第一电压位准以导通开关tg2。

94.如图4中说明性地示出,逻辑单元448包含或非门nr43及反相器in43。或非门nr43的两个输入端用以分别接收数字信号en00及en01。或非门nr43的输出端用以输出控制信号s43。反相器in43的输入端用以接收控制信号s43。反相器in43的输出端用以输出控制信号s43b。因此,控制信号s43在数字信号en11及en10中的一者具有位元值1时具有第一电压位准以导通开关tg4及tg5。

95.在各种实施例中,逻辑单元442、444、446及448具有各种组态且包含各种逻辑部件。举例而言,在一些替代实施例中,逻辑单元442、444、446及/或448具有与图3b中所示出的逻辑单元301类似的组态。

96.下面利用图5、图6a、图6b、图6c及图6d中所示出的实施例描述了记忆体400的操作的其他细节。

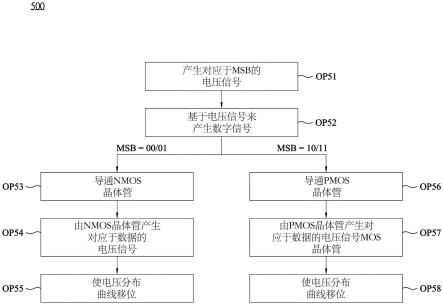

97.图5为根据本揭示内容的一些实施例的图1、图3a及图4中所示出的记忆体100、300及400产生电压信号vs2的方法500的流程图。如图5中说明性地示出,方法500包含操作op51~op58。

98.在操作op51中,产生对应于数据dt的一或多个msb的电压信号vmsb。在操作op52中,基于电压信号vmsb来产生数字信号en00、en01、en10及en1。

99.回应于电压信号vmsb具有位元值00或01,执行操作op53~op55。回应于电压信号vmsb具有位元值11或10,执行操作op56~op58。

100.在操作op53中,产生控制信号s43及s44以导通晶体管m41~m43中的至少一者。因此,读取电路424的电阻减小。

101.在操作op54中,电压信号vs2由晶体管m41~m43中的至少一者产生,电压信号vs2具有低于电压信号vs1的电压位准的电压位准。因此,在操作op55中,电压信号vs2的电压分布曲线沿着图2中所示出的箭头a21移位。

102.在操作op56中,产生控制信号s41及s42以导通晶体管p41~p42中的至少一者。因此,读取电路422的电阻减小。

103.在操作op57中,电压信号vs2由晶体管p41~p42中的至少一者产生,电压信号vs2具有高于电压信号vs1的电压位准的电压位准。因此,在操作op58中,电压信号vs2的电压分布曲线沿着图2中所示出的箭头a22移位。

104.图6a及图6b为表示根据本揭示内容的一些实施例的电压信号vs1、vs2的电压位准

与图4中所示出的数据dt的位元值之间的关系的电压分布曲线的图600a及600b。参看图5、图6a及图6b,图600a及600b描述操作op53的其他细节。

105.如图6a及图6b中说明性地示出,图600a及600b中的每一者包含对应于数据dt的位元值的水平轴及对应于电压信号vs1及vs2的电压位准的垂直轴。

106.如图6a中说明性地示出,图600a包含电压分布曲线c61及c62。电压分布曲线c61及c62分别对应于电压信号vs1及vs2。在一些实施例中,电压分布曲线c62对应于数据dt的两个msb均具有位元值11的情况。

107.在图6a中所示出的实施例中,数据dt具有大于位元值b61的位元值b6a。在一些实施例中,位元值b61为具有msb 10的最大位元值,且位元值pb为具有msb 01的最大位元值。举例而言,若数据具有四个位元,则位元值b61为1011,位元值pb为0111且位元值b6a大于1011。

108.参看图6a及图4,回应于电压信号vmsb具有位元值11,数字信号en11具有位元值1,且数字信号en00、en10及en01中的每一者具有位元值0,使得控制信号s41及s42具有第一电压位准,且控制信号s43及s44具有第二电压位准。因此,晶体管p41及p42导通,而晶体管m41~m43关断。晶体管p41~p44及m44产生对应于电压分布曲线c62的电压信号vs2。

109.如图6b中说明性地示出,图600b包含电压分布曲线c61及电压分布曲线c63。电压分布曲线c63对应于电压信号vs2。在一些实施例中,电压分布曲线c63对应于数据的两个msb均具有位元值10的情况。

110.在图6b中所示出的实施例中,数据dt具有位元值b6b,位元值b6b小于或等于位元值b61且大于位元值pb。举例而言,若数据具有四个位元,则位元值b61为1011且位元值pb为0111,位元值b6a大于0111且小于或等于1011。

111.参看图6b及图4,回应于电压信号vmsb具有位元值10,数字信号en10具有位元值1,且数字信号en00、en11及en01中的每一者具有位元值0,使得控制信号s42具有第一电压位准,且控制信号s41、s43及s44具有第二电压位准。因此,晶体管p42导通,而晶体管p41、m41~m43关断。晶体管p42~p44及m44产生对应于电压分布曲线c63的电压信号vs2。

112.参看图4、图6a及图6b,对应于图600a的读取电路422的电阻小于对应于图600b的读取电路422的电阻。因此,电压分布曲线c62的电压位准大于电压分布曲线c63的电压位准。换言之,电压分布曲线c62与电压分布曲线c61移位的程度(degree)大于电压分布曲线c63与电压分布曲线c61移位的程度。

113.图6c及图6d为表示根据本揭示内容的一些实施例的电压信号vs1、vs2的电压位准与图4中所示出的数据dt的位元值之间的关系的电压分布曲线的图600c及600d。参看图5、图6c及图6d,图600c及600d描述操作op56的其他细节。

114.如图6c及图6d中说明性地示出,图600c及600d中的每一者包含对应于数据dt的位元值的水平轴及对应于电压信号vs1及vs2的电压位准的垂直轴。

115.如图6c中说明性地示出,图600c包含电压分布曲线c61及c64。电压分布曲线c61及c64分别对应于电压信号vs1及vs2。在一些实施例中,电压分布曲线c64对应于数据的两个msb均具有位元值00的情况。

116.在图6c中所示出的实施例中,数据dt具有小于位元值b62的位元值b6c。在一些实施例中,位元值b62为具有msb 01的最小位元值,且位元值pb为具有msb 01的最大位元值。

举例而言,若数据具有四个位元,则位元值b62为0100,位元值pb为0111且位元值b6c小于0100。

117.参看图6c及图4,回应于电压信号vmsb具有位元值00,数字信号en00具有位元值1,且数字信号en11、en10及en01中的每一者具有位元值0,使得控制信号s43及s44具有第一电压位准,且控制信号s41及s42具有第二电压位准。因此,晶体管m41~m43导通,而晶体管p41~p42关断。晶体管p43~p44及m41~m44产生对应于电压分布曲线c64的电压信号vs2。

118.如图6d中说明性地示出,图600d包含电压分布曲线c61及电压分布曲线c65。电压分布曲线c65对应于电压信号vs2。在一些实施例中,电压分布曲线c65对应于数据的两个msb均具有位元值01的情况。

119.在图6d中所示出的实施例中,数据dt具有位元值b6d,位元值b6d小于或等于位元值pb且大于或等于位元值b62。举例而言,若数据具有四个位元,则位元值b62为0100且位元值pb为0111,位元值b6a大于或等于0100且小于或等于0111。

120.参看图6d及图4,回应于电压信号vmsb具有位元值01,数字信号en01具有位元值1,且数字信号en00、en11及en10中的每一者具有位元值0,使得控制信号s43具有第一电压位准,且控制信号s41、s42及s44具有第二电压位准。因此,晶体管m42及m43导通,而晶体管p41~p42及m41关断。晶体管p43~p44及m42~m43产生对应于电压分布曲线c65的电压信号vs2。

121.参看图4、图6c及图6d,对应于图600c的读取电路424的电阻小于对应于图600d的读取电路422的电阻。因此,电压分布曲线c64的电压位准小于电压分布曲线c65的电压位准。换言之,电压分布曲线c64与电压分布曲线c61移位的程度大于电压分布曲线c65与电压分布曲线c61移位的程度。

122.综上所述,电压信号vs2根据数据的msb的不同位元值进行了不同程度的调整,使得对应电压分布曲线c62~c65移位了不同程度。

123.亦揭示一种包含记忆体装置、读取装置及反馈装置的记忆体。记忆体装置用以储存多个位元。读取装置包含第一读取电路及第二读取电路。第一读取电路耦接至记忆体装置。第二读取电路耦接至记忆体装置,且在第一节点处耦接至第一读取电路。第一读取电路及第二读取电路用以彼此协作以基于多个位元中的至少一个第一位元来在第一节点处产生第一电压信号。反馈装置用以基于第一电压信号来调整第一读取电路及第二读取电路中的至少一者。第一读取电路及第二读取电路用以在第一读取电路及第二读取电路中的至少一者由反馈装置调整之后产生对应于多个位元的第二电压信号,第二电压信号与第一电压信号不同。在一些实施例中,反馈装置进一步用以回应于至少一个第一位元具有一第一位元值而调整第一读取电路,且回应于至少一个第一位元具有与第一位元值不同的一第二位元值而调整第二读取电路。在一些实施例中,反馈装置进一步用以调整第一读取电路及第二读取电路中的至少一者的一电阻以调整第一节点的一电压位准。在一些实施例中,反馈装置包括:一第一逻辑单元,用以回应于第一电压信号具有一第一位元值而产生一第一控制信号;且第一读取电路包括:一第一晶体管,耦接至第一节点,且用以被第一控制信号控制。在一些实施例中,反馈装置进一步包括:一第二逻辑单元,用以回应于第一电压信号具有与第一位元值不同的一第二位元值而产生一第二控制信号;且第二读取电路包括:一第二晶体管,耦接至第一节点,且用以被第二控制信号控制,其中第一晶体管及第二晶体管为

不同类型的晶体管。在一些实施例中,反馈装置进一步包括:一第二逻辑单元,用以回应于第一电压信号具有与第一位元值不同的一第二位元值而产生一第二控制信号;且第一读取电路进一步包括:一第二晶体管,耦接至第一节点,且用以基于第二控制信号来控制,其中第一晶体管及第二晶体管为一相同类型的晶体管。在一些实施例中,第一逻辑单元进一步用以产生与第一控制信号互补的一第二控制信号;且第一读取电路进一步包括:一传输门,其中传输门的一第一端耦接至第一晶体管的一控制端,传输门的两个控制端用以分别接收第一控制信号及第二控制信号。在一些实施例中,第一读取电路进一步包括:一第二晶体管,其中第二晶体管的一第一端耦接至第一晶体管的一控制端,第二晶体管的一第二端用以接收一禁用电压信号,第二晶体管的一控制端用以接收第二控制信号。在一些实施例中,第一逻辑单元包括:一或非门,用以接收第一电压信号且用以输出第一控制信号;及一反相器,用以接收第一控制信号且用以输出与第一控制信号互补的一第二控制信号。

124.亦揭示一种包含记忆体装置、读取装置、读出装置及反馈装置的记忆体。读取装置耦接至记忆体装置,且用以读取储存于记忆体装置中的数据以产生第一电压信号,第一电压信号对应于第一电压分布曲线。读出装置用以读出第一电压信号且用以产生数字信号,数字信号对应于所读出的第一电压信号。反馈装置用以回应于数字信号而产生至少一个控制信号,以用于控制读取装置产生第二电压信号,第二电压信号对应于与第一电压分布曲线不同的第二电压分布曲线。在一些实施例中,第一电压信号中的一第一电压信号具有一第一电压位准,第一电压位准与第二电压信号中的一第二电压信号的一第二电压位准不同,且第一电压信号及第二电压信号对应于具有一相同位元值的数据。在一些实施例中,读取装置包括:一第一类型的一第一晶体管;及一第二类型的一第二晶体管,第二类型与第一类型不同,及反馈装置进一步用以回应于相同位元值大于一第一预定位元值而导通第一晶体管,以增加第二电压位准,且回应于相同位元值小于第一预定位元值而导通第二晶体管,以减小第二电压位准。在一些实施例中,读取装置包括:第一类型的一第三晶体管,与第一晶体管并联耦接,且反馈装置进一步用以回应于相同位元值大于一第二预定位元值而导通第一晶体管及第三晶体管,第二预定位元值大于第一预定位元值,且回应于相同位元值在第二预定位元值与第一预定位元值之间而导通第一晶体管且关断第三晶体管。在一些实施例中,第二电压分布曲线的一第一电压位准与一第二电压位准之间的一第一电压位准差大于第一电压分布曲线的一第一电压位准与一第二电压位准之间的一第二电压位准差,第二电压分布曲线的第一电压位准及第一电压分布曲线的第一电压位准对应于具有一第一位元值的数据,且第二电压分布曲线的第二电压位准及第一电压分布曲线的第二电压位准对应于具有与第一位元值不同的一第二位元值的数据。在一些实施例中,反馈装置包括:多个逻辑单元,用以分别接收数字信号,以产生至少一个控制信号,其中逻辑单元的一第一部分用以控制读取装置中的一第一类型的至少一个晶体管,且逻辑单元的一第二部分用以控制读取装置中的一第二类型的至少一个晶体管。在一些实施例中,逻辑单元的第一部分包括:一第一逻辑单元,用以接收数字信号中的一第一数字信号;及一第二逻辑单元,用以接收数字信号中的第一数字信号及一第二数字信号,其中第一数字信号及第二数字信号分别对应于数据的一第一位元值及一第二位元值,且第二位元值小于第一位元值。

125.亦揭示一种记忆体的操作方法,包含:由互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)电路产生与储存于记忆体装置中的数据相关联的第一

电压信号,其中第一电压信号的电压位准对应于第一电压分布曲线;读出第一电压信号以产生与数据的至少一个第一位元相关联的数字信号;及根据数字信号控制cmos电路产生第二电压信号,其中第二电压信号对应于数据,且第二电压信号的电压位准对应于第二电压分布曲线,第二电压分布曲线具有与第一电压分布曲线的移位或具有与第一电压分布曲线不同的轮廓。在一些实施例中,控制互补金属氧化物半导体电路包括:回应于至少一个第一位元的一位元值大于一第一预定位元值,增加第二电压信号的电压位准;及回应于位元值小于第一预定位元值,减小第二电压信号的电压位准。在一些实施例中,减小第二电压信号的电压位准进一步包括:回应于位元值小于第一预定位元值,将第二电压信号的电压位准减小了一第一程度;及回应于位元值小于一第二预定位元值,将第二电压信号的电压位准减小了大于第一程度的一第二程度,第二预定位元值小于第一预定位元值。在一些实施例中,控制互补金属氧化物半导体电路包括:增加第一电压分布曲线的一第一电压位准与一第二电压位准之间的一电压位准差,以产生第二电压分布曲线,其中第一电压位准对应于数据的一第一位元值,且第二电压位准对应于与第一位元值相邻的一第二位元值。

126.前述内容概述了数个实施例的特征,使得熟悉此项技术者可更佳地理解本揭示内容的各个态样。熟悉此项技术者应了解,他们可容易地使用本揭示内容作为设计或修改用于实现本文中所引入的实施例的相同目的及/或达成相同优势的其他工艺及结构的基础。熟悉此项技术者亦应认识到,此类等效构造并不脱离本揭示内容的精神及范畴,且在不脱离本揭示内容的精神及范畴的情况下可在本文中进行各种改变、替换及变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1