一种内容可寻址存储器的制作方法

1.本发明涉及集成电路领域,尤其涉及存储器领域。

背景技术:

2.内容可寻址存储器(content addressable memory,cam)是一种不仅能存取数据,而且具有查询功能的存储器件。查询功能指将输入的查询数据与内部所有数据进行比较,判定查询数据是否已经存在于存储器中;若查询数据已经存在于存储器中,输出查询数据位于存储器的地址。内容可寻址存储器可以在单个时钟周期内并行完成数据的比较查找运算,相比其他基于硬件或软件的搜索系统,具有更高的查找效率,被广泛地应用于各个领域。

3.在现有的主流技术方案中,内容可寻址存储器使用模拟电路搭建存储单元,通过向单个sram单元添加若干晶体管的方法,实现将当前输入数据与预设数据进行比较并输出比较结果。

4.现有主流技术方案中的、使用模拟电路搭建的内容可寻址存储器的缺点在于,开发周期长,开发成本高,且在更换工艺时需要重新开发。为解决这一问题,开发了由数字电路单元构成的内容可寻址存储器。为方便叙述,称由数字电路单元构成的内容可寻址存储器为dcam(digitalcam)。

5.在现有技术方案中,dcam使用触发器作为存储单元,导致dcam的面积较大,功耗较高。

技术实现要素:

6.针对现有技术中存在的问题,本发明提供了一种内容可寻址存储器。该内容可寻址存储器包括写控制电路、存储单元阵列和寻址控制电路,所述内容可寻址存储器的各部分由数字电路单元构成,存储单元阵列中的存储单元为锁存器(latch),为方便叙述,称由数字电路单元构成的内容可寻址存储器为dcam。

7.上述的写控制电路包括写数据寄存器和写地址译码器。

8.上述的寻址控制电路包括查找数据寄存器寄存器、匹配线编码器和查找地址寄存器。

9.在本发明的又一实施例中,上述的dcam还包括读控制电路。

10.上述的读控制电路包括读数据寄存器和读地址译码器。

11.在本发明的又一实施例中,上述的写控制电路还包括数据门控电路。

12.本发明的有益效果是,本发明提供了一种内容可寻址存储器,与现有主流技术方案中主要由模拟电路构成的内容可寻址存储器相比,dcam的主要开发工作与工艺无关,降低了开发成本;与现有的dcam相比,本发明提供了一种使用锁存器作为存储单元的dcam,可以降低dcam的功耗和面积;本发明又提供了一种含有数据门控电路的dcam,进一步降低了dcam的功耗。

附图说明

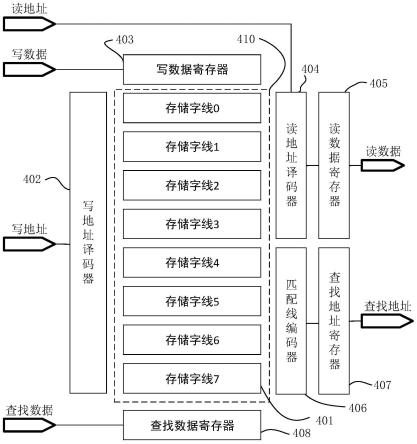

13.图1是包含触发器的dcam的存储单元的示例图

14.图2是包含锁存器的新型dcam的存储单元的示例图

15.图3是新型dcam的存储字线的示例图

16.图4是新型dcam的示例图

17.图5是包含数据门控电路的新型dcam的示例图

具体实施方式

18.针对现有技术中存在的问题,本发明一实施例提供了一种新型dcam,具体如下。

19.在本发明一实施例中,采用锁存器作为存储单元。具体的结构与连接关系如下。

20.图2为dcam中一个存储单元的示例图。写数据端口连接至锁存器的d端口;写有效端口连接至锁存器的en端口;锁存器的q端口与查找数据信号连接至异或门的两输入端口;异或门的输出端口取反后连接至数据匹配端口;锁存器的q端口连接至读数据端口。每个存储单元可以存储一个比特。

21.在数据位宽为n的dcam中,每个数据包含n个比特,其对应的n个存储单元构成一个存储单元字线。图3为dcam中一个存储单元字线的示例图。存储单元301的写数据端口连接至存储单元字线的写数据端口的不同比特;存储单元301的写有效端口连接至存储单元字线的写有效端口;存储单元301的查找数据端口连接至存储单元字线的查找数据端口的不同比特;存储单元301的读数据端口连接至存储单元字线的读数据端口的不同比特;存储单元301的数据匹配端口连接至与门的不同输入端口;与门的输出端口连接至存储单元字线的数据匹配端口。

22.图4为一个dcam的示例图。dcam由存储单元阵列410和外围控制电路组成。存储单元阵列410由多个存储单元字线401组成。

23.dcam的写控制电路包括写数据寄存器403和写地址译码器402,连接关系如下:dcam的写数据端口连接至写数据寄存器403的输入端;写数据寄存器403的输出端连接至所有存储单元字线401的写数据端口;dcam的写地址端口连接至写地址译码器402的输入端;写地址译码器402的输出端连接至所有存储单元字线401的写使能端口。向dcam写入数据时,与写地址对应的存储单元字线401被选中,被选中的存储单元字线401的写使能端口值为有效,其余的存储单元字线401的写使能端口值为无效;所有的存储单元字线401的写数据端口值为写数据的值。

24.dcam的读控制电路包括读数据寄存器405和读地址译码器404,连接关系如下:dcam的读地址端口连接至读地址译码器404的输入端;存储单元字线401的读数据端口连接至读地址译码器404的不同的输入端;读地址译码器404的输出端连接至读数据寄存器405的输入端;读数据寄存器405的输出端连接至dcam的读数据端口。从dcam读取数据时,与读地址对应的存储单元字线401被选中,读地址译码器404将被选中的存储单元字线401读数据端口的值输出至dcam读数据端口。

25.dcam的寻址控制电路包括查找数据寄存器寄存器408、匹配线编码器406和查找地址寄存器407,连接关系如下:dcam的查找数据端口连接至查找数据寄存器寄存器408的输入端;查找数据寄存器寄存器408的输出端连接至存储单元字线401的查找数据端口;存储

单元字线401的数据匹配端口连接至匹配线编码器406的输入端口;匹配线编码器406的输出端口连接至查找地址寄存器407的输入端口;查找地址寄存器407的输出端口连接至dcam的查找地址端口。从dcam查找数据时,包含查找数据的存储单元字线401被选中,匹配线编码器406计算出被选中的存储单元字线401的地址,并从dcam的查找地址端口输出结果。

26.通过使用锁存器代替触发器,对dcam进行了优化:锁存器面积较触发器低,从而降低了dcam的面积;锁存器不需要连接频繁翻转的时钟信号,从而降低了dcam的功耗。

27.在本发明又一实施例中,一个dcam的示例图如图5所示。

28.区别于图4,图5中dcam的写控制电路包括写数据寄存器403、写地址译码器402和数据门控电路409,连接关系如下:dcam的写数据端口连接至写数据寄存器403的输入端;写数据寄存器403的输出端连接至数据门控电路409的输入端;dcam的写地址端口连接至写地址译码器402的输入端;写地址译码器402的输出端连接至所有存储单元字线401的写使能端口和数据门控电路409的另一输入端;数据门控电路409的输出端分别连接至存储单元字线401的写数据端口。向dcam写入数据时,与写地址对应的存储单元字线401被选中,被选中的存储单元字线401的写使能端口值为有效,其余的存储单元字线401的写使能端口值为无效;被选中的存储单元字线401的写数据端口值为写数据的值,被选中的存储单元字线401的写数据端口值为预设的定值。

29.通过增加数据门控电路409模块使得,向dcam写入数据时,仅有被选中的存储单元字线401的写数据端口的值发生变化,减少了存储单元字线401写数据端口的值的变化次数,从而降低dcam的功耗。

30.在本发明又一实施例里中,dcam不具备读取数据的功能,可将读数据相关电路从dcam中删除:可将读数据端口从图2示例的存储单元中删除;可将读数据端口从图3示例的存储单元字线中删除;可将读地址段端口、读数据端口、读地址译码器和读数据寄存器从图4或图5示例的dcam中删除。

31.在不需要通过地址读取数据的情境下,删除读取数据相关的电路不会影响其他功能的正确工作,可以进一步降低电路的面积。

32.对于本领域的技术人员而言,阅读上述说明后,各种变化和修正无疑将显而易见。因此,所附的权利要求书应看作是涵盖本发明的真实意图和范围的全部变化和修正。在权利要求书范围内任何和所有等价的范围与内容,都应认为仍属本发明的意图和范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1