一种基于FPGA的多通道Flash存储器性能测试系统

一种基于fpga的多通道flash存储器性能测试系统

(一)技术领域:

1.本发明涉及集成电路可靠性测试领域,尤其涉及一种基于现场可编程门阵列(即fpga)的多通道flash存储器性能测试系统。

(二)

背景技术:

2.多数flash存储器的基本单元是基于浮栅工艺的mos管,它有两个栅:一个控制栅和一个位于沟道和控制栅之间的浮栅。flash存储器保存数据的方式是在浮栅中注入或移出电子,若浮栅中有电荷,浮栅管处于断开状态,产生较小的沟道电流,读出

‘0’

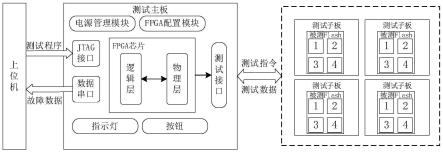

;若浮栅管中无电荷,浮栅管处于导通状态,产生较大的沟道电流,读出

‘1’

。向浮栅中注入电子的过程为flash存储器的写入过程,从浮栅中移出电子的过程为flash存储器的擦除过程,一次擦除和一次写入过程构成一个擦写循环。flash存储器最主要的两个性能指标为耐擦写性能与数据保持性能,耐擦写性能是指flash存储器可以经受的最大擦写循环次数;数据保持性能是指flash存储器在不进行其他操作时,其中的数据可以保持的时间。

3.从flash存储器的结构来看,大量的擦写循环会对其浮栅氧化层造成损伤,导致flash存储器的数据保持性能变差,导致flash存储单元中存储的数据可能发生1到0或0到1的翻转,导致数据错误、逻辑混乱、指令异常等,进而影响整个系统的稳定性和可靠性。随着flash存储器大量应用于各型号航天系统,对其性能评价至关重要。

4.目前多数flash存储器测试系统主要适用于评价flash存储器的耐擦写性能,对数据保持性能考虑较少,更缺乏将二者进行综合的考虑。本专利设计的一种基于fpga的多通道flash存储器性能测试系统,可以完成对flash存储器耐擦写性能与数据保持性能的测试,并可以对被测存储器施加擦写循环后,测试不同擦写循环次数下的数据保持性能,适用于nand flash和nor flash存储器,最多可同时对16个存储器进行测试,支撑flash存储器性能的鉴定检验。

(三)

技术实现要素:

5.1.目的:

6.本发明的目的是提供可以同时完成对16个flash存储器耐擦写性能和数据保持性能的检测,同时适用于nand flash和nor flash存储器的性能测试系统系统。

7.2.技术方案:

8.本发明提出一种基于fpga的多通道flash存储器性能测试系统,它是由控制母板和检测子板组成,包括fpga模块、电源模块、时钟电路模块、jtag接口、程序保存flash模块、usb转uart模块、复位电路、按钮与指示灯电路、测试接口模块。

9.检测系统各组成部分相互关系是:电源模块为核心fpga模块、时钟电路模块、联合测试工作组(即jtag)接口模块、程序保存flash模块、usb转uart通信模块、复位电路、按钮与指示灯电路供电,同时引出4路测试电源,每路测试电源连接一块测试子板,能为测试子板上4个被测flash存储器供电。核心fpga模块产生对被测flash存储器操作的指令、时钟信

号、输入数据以及对flash存储器存储数据进行校验。时钟模块由时钟生成芯片输入到fpga作为全局时钟。jtag模块将上位机程序下载到fpga中。通信模块完成上位机与检测系统数据传输。程序保存flash模块存储系统控制软件。usb转uart模块将故障数据由测试板向上位机传输。复位电路对系统进行软复位与硬复位。按钮与指示灯电路调控、显示系统状态。测试接口模块连接控制母板和测试子板。

10.fpga模块。检测系统采用xilinx的spartan-6fpga,主要功能是根据设计的测试功能,产生相应的功能逻辑与时序逻辑,即对flash存储器操作的指令、时钟信号、输入数据都由fpga产生,从flash存储器读取的数据也由fpga接收并进行校验,最终校验结果返回至上位机。fpga引脚分配如图1。

11.电源模块。为满足fpga及各功能模块所需的多种电压输入,使用mp1482芯片、1117芯片以及配置电路,实现5v转3.3v,5v转1.2v,5v转1.5v,5v转2.5v等。同时,考虑到需要对多个被测flash供电,对3.3v电路进行了冗余设计,提高其带载能力。此外,对所有电压转换电路增加了旁路电容,减小电压波动带来的影响,具体原理图设计如图2所示。

12.时钟电路模块。设计使用50mhz晶振作为基础的时钟源,产生的时钟信号输入fpga的全局时钟引脚(gclk)作为其内部所有逻辑电路的驱动信号,此外,fpga将以此为基准产生其余模块所需的其他频率的时钟信号,具体的原理图设计如图3所示。

13.联合测试工作组即,joint test action group(jtag)是一种国际标准测试协议,可以进行最深层的芯片测试。arm、dsp以及fpga等高级数字器件都支持该协议下的测试,由上位机设计完成的程序生成bit流文件之后可以通过此接口下载到fpga中,也可以利用此接口实时抓取fpga内部的数据。jtag协议包含四个数据线,分别是时钟(tck)、模式选择(tms)、数据输入(tdi)以及数据输出(tdo),以上数据线都与fpga对应引脚相连,具体设计原理图如图4所示。

14.程序保存flash模块。由于fpga不具备断电后保存数据的能力,所以需要配置外部的flash存储器,在测试程序设计完成后,只需将生成的mcs文件烧录到flash存储器中,就可以在系统开机之后直接配置fpga,不必再次向fpga下载bit流文件。设计选取w25q128bv型flash存储器,它的四路输入输出引脚,时钟引脚以及片选引脚直接与fpga相连,具体设计原理图如图5所示。

15.usb转uart模块。其功能是实现故障数据由测试板向上位机的传输。uart是一种异步串口通信协议在设置好波特率与校验位之后就可以实现数据的传输,设计采用cp2102芯片实现利用mini usb接口实现串口功能,具体电路原理图如图6所示。

16.复位电路。其功能是,当系统处于不正确状态时,通过复位电路可以迅速恢复到正常状态,从而维护系统运行的稳定性,避免在不确定状态下工作导致的破坏。根据fpga工作原理,设计了软复位与硬复位电路,软复位是将系统状态恢复到程序所设定的初始状态,硬复位是清空fpga中的所有数据,恢复工作需要重新下载bit流文件,具体电路原理图如图7所示。

17.按钮与指示灯电路。其功能是实现测试系统与外界的简单交互,通过指示灯显示测试系统当前状态,通过按钮输入开始测试、模式选择等输入,具体的电路原理图如图8所示。

18.测试接口模块。其功能是实现与测试子板之间的信号连接与电源供给,在测试主

板上设计了4个测试接口模块,以实现对4个测试子板16个被测flash存储器的测试需求,具体的电路原理图如图9所示。

19.测试子板。用于搭载被测flash存储器,设计子板的目的是使测试系统的结构灵活,提高测试系统的改进潜力。测试子板上设计有4个flash存储器测试座以及与上位机信号与电源接口,具体的电路原理图如图10所示。

20.3.优点及功效:

21.本发明提出一种基于fpga的flash存储器单粒子效应检测系统,该发明的优点是:

22.1)测试系统能对flash器件进行全片读写擦操作,具有对flash存储器常见性能指标,即耐擦写性能与数据保持性能进行测试的能力。

23.2)控制板上预留了足够的io,可以通过软件配置了串行接口和并行接口flash存储器相关控制信号的工作条件,可以适用于不同nand flash和nor flash存储器。

24.3)检测系统适用于常用的flash存储器擦写寿命试验、flash存储器数据保持试验以及考虑擦写次数的数据保持试验。对于脉冲激光模拟单粒子效应试验,检测子板采用直插的方式与控制母板连接,对于粒子加速器模拟单粒子效应试验,检测子板采用排线的方式与控制母板连接。

(四)附图说明:

25.图1 fpga引脚分配图

26.图2电源模块电路原理图

27.图3时钟模块电路原理图

28.图4 jtag模块电路原理图

29.图5程序保存flash模块电路原理图

30.图6 usb转uart模块电路原理图

31.图7复位电路原理图

32.图8按钮与指示灯电路原理图

33.图9测试接口模块电路原理图

34.图10测试子板电路原理图

35.图11检测步骤

36.图12 flash存储器性能测试系统结构图

37.图13 flash存储器性能测试系统实物图

(五)具体实施方式:

38.一种基于fpga的多通道flash存储器性能测试系统,其特征在于:它是由控制母板和测试子板组成,包括核心fpga模块、电源模块、时钟电路模块、联合测试工作组(即jtag)接口模块、程序保存flash模块、usb转uart通信模块、复位电路、按钮与指示灯电路、测试接口模块。测试系统可以对flash器件进行全片读写擦操作,具有对flash存储器主要性能即耐擦写性能与数据保持性能进行测试的能力。控制板上引出足够的io,配置了串行接口flash存储器相关控制信号的工作条件,被测器件电源电压供给为3.3v,故检测系统可以适用于工作电压为3.3v的串行nand flash和nor flash存储器。检测系统适用于常用的flash

存储器擦写寿命试验、flash存储器数据保持试验;测试子板采用排线的方式与控制母板连接。

39.本案例中,flash存储器采用的是国产gd25q16csig型nor flash存储器,器件采用并行接口,容量大小为16mbit,使用spi数据接口。检测步骤如图11所示。

40.本发明所述的一种基于fpga的多通道flash存储器性能测试系统,其特征在于:检测系统操作步骤如下:

41.步骤1:上电配置。当flash存储器性能测试任务开始后,按下开关,fpga读取程序存储flash中的配置文件,进入空闲待机状态,等待下一步指令。

42.步骤2:选择测试系统工作状态。测试系统具有擦写循环与数据验证两种工作状态,通过按动控制母板上对应的按钮选择进行不同的工作状态。

43.步骤3:擦写循环工作状态。在擦写循环状态下,测试系统对被测的flash存储器施加擦写循环,循环次数以及写入数据由上位设定,flash存储器擦写指令由fpga发出经测试接口传输到测试子板上的被测flash存储器,发送指令顺序为写使能06h,擦指令60h,写指令02h,写入数据为00h,达到设定的擦写循环次数后,写入测试图案55h,测试母板led亮起。

44.步骤4:数据验证工作状态。在数据验证工作状态下,测试系统读出被测flash存储器中的数据并进行验证,验证数据模板由上位机设定。fpga发送存储器读取操作指令02h,控制逻辑进入检测状态,在全片读取时产生错误时,flash控制逻辑把错误数据和产生错误位的地址写入错误数据寄存器,全部地址读取验证完成后,测试系统将错误信息通过串口发送至上位机。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1