一种基于电容耦合的乒乓式存内计算电路

1.本发明公开了一种基于电容耦合的乒乓式存内计算电路,属于专用集成电路设计技术领域。

背景技术:

2.近些年,人工智能发展迅速,在各个领域与多种应用场景深度融合,给生活的方方面面带来很大的便利。卷积神经网络(convolutional neural network,cnn)已经成为机器学习的一项重要技术,被广泛应用在人工智能领域的图像识别、语音视频识别上。在深度学习网络的实现中,庞大的数据量带来工作负载、实时性和安全性的问题。因此低功耗、高性能的ai芯片和cnn专用硬件加速器的设计成为工业界和学术界研究的热点。

3.传统的冯诺依曼计算机体系架构中,中央处理器和存储器通过总线传输大量数据,庞大的数据量造成的延时和功耗浪费,以及有限的数据传输带宽,成为传统架构中最大的瓶颈。因此存算一体结构应运而生。由于深度神经网络需要对输入数据和权重数据执行大量的乘累加运算(multiplication and accumulation,mac),其高复用率和高并行度特点适合部署在存内计算(computing-in-memory,cim)电路中进行,大大减少数据传输和能耗延时的浪费,进而提高了系统的能效和实时性,在高能效人工智能系统中有广泛的应用前景。

4.然而,随着深度神经网络模型的复杂度和数据量的增加,越来越大的参数量和有限的片上存储器容量之间的矛盾,加剧了更新权值的需求。由于传统片上存储器有限的写带宽,以及难以同时计算和更新,导致严重的权值更新开销,进而降低电路性能。同时,现行的模拟域的存内计算电路有线性度、阵列内部波动、量化开销等问题,导致有限的计算精度和并行度,限制了存内计算cim能效的提升。

技术实现要素:

5.技术问题:本发明的目的是针对上述背景技术的不足,以高能效、低功耗为木目标,提出一种基于电容耦合的乒乓式存内计算电路。

6.技术方案:本发明是一种基于电容耦合的乒乓式存内计算电路,该存内计算电路包括:电容耦合的乒乓式存内计算阵列、依赖稀疏度的精度可调量化阵列;电容耦合的乒乓式存内计算阵列中存储的是权重值,输入特征值送到阵列,该计算阵列中每列得到的乘累加模拟值通过对应的量化电路转换成数字信号,再送到外围的移位相加电路得到最终的计算值,同时,需要更新的权重值通过读写驱动电路写入该计算阵列内部的静态随机存储器中;其中,乘累加计算操作和权重更新操作通过交替使用上方乘单元ubmu和下方乘单元dbmu的方式实现乒乓操作,达到提高吞吐量的目的。

7.所述电容耦合的乒乓式存内计算阵列结构cppcim有64个计算列构成,每个计算列中包括32个cppcim块,每个cppcim块由1个上方乘单元ubmu、1个下方乘单元dbmu和1个乒乓计算单元ppcc组成;该乒乓计算单元ppcc放在上方乘单元ubmu与下方乘单元dbmu之间,上

方乘单元ubmu和下方乘单元dbmu都是由4个紧凑的6t静态随机存储器和4个用于选通的nmos晶体管m1~m4组成;其中第一nmos晶体管、第二nmos晶体管栅极接到写选通信号,第三nmos晶体管、第四nmos晶体管栅极接到计算选通信号;第一nmos晶体管、第二nmos晶体管源漏分别接到全局位线和局部位线上,第三nmos晶体管、第四nmos晶体管源漏分别接到局部位线和计算位线上;乒乓计算单元ppcc由第五nmos晶体管和pmos晶体管组成一个传输门、第七nmos晶体管以及一个金属层mom电容组成;其中第五nmos晶体管和pmos晶体管栅极接到计算位线上,源漏分别连接输入特征值对应的输入特征值信号和内部节点,第七nmos晶体管栅极接到计算位线上,源漏连接内部节点和地;金属层mom电容上下极板分别接到内部节点和乘累加位线上。

8.所述依赖稀疏度的精度可调量化阵列,包括输入感知检测器和一个单边逐次逼近型量化电路;输入感知检测器得到每个周期32个输入特征值信号中0的个数,通过和提前设定的阈值相比较,产生对应的精度配置控制信号,送到量化器中;单边逐次逼近型量化电路包括一个电容式dac阵列、sar逻辑控制量化电路、动态锁存放大器的和移位寄存器;其中电容式dac阵列采用金属层mom电容,电容容值分别为1c、1c、2c、4c、8c、16c,电容上级板共同接到放大器的差分输入端n极,电容下级板通过开关电路分别接到参考电压vref1和vref2上,动态锁存放大器的差分输入端p极连接计算阵列中得到的乘累加位线mbl,放大器的输出接到移位寄存器,通过控制信号控制移位,完成多比特的量化操作;移位寄存器的输出送到外围的移位相加电路,实现单比特乘累加到多比特乘累加的计算。

9.所述的乒乓式存内计算电路支持读、写、计算、同时计算和更新权重四种工作模式,在实现计算操作时,一个周期有32个单比特输入特征值同时送到每列的计算单元中,所述的每个计算列的乘累加位线和输入特征值信号在计算周期之初,通过自定时的异步复位信号拉到地,将计算单元内部的计算电容上的电荷量清零,随即进行计算,最后进行量化。

10.所述输入感知检测器,其阈值是通过外部软件对特定的神经网络进行训练,统计网络中每层的输入特征值的稀疏度,得到用于配置量化精度的阈值,在降低量化功耗和延时开销的同时,保证准确度。

11.所述输入感知检测器,通过和阈值比较,产生对应的精度配置控制信号,根据该精度配置控制信号,量化器电路量化不同比特位数的值;如果精度配置为全精度5bit,则sar逻辑控制量化电路进行传统的全精度的二进制逼近式量化操作;如果精度配置为非全精度3bit,则sar逻辑控制量化电路跳过高2bit的量化,即高2bit直接为0,直接进行低3bit的量化;如果精度配置为无需量化,则不开启量化器,量化结果直接为0。

12.所述依赖稀疏度的精度可调量化阵列,采用的是异步sar逻辑,即无论量化多少比特,量化操作都会在同一时钟周期内完成,量化精度配置的不同会影响工作频率,输入特征值的稀疏度越高,量化的功耗和延时开销越小。

13.有益效果:本发明设计了可以同时进行计算和权重值更新的乒乓式存算单元,为了提高模拟域存内计算的线性度和面积效率,存算单元采用金属层电容作为计算媒介,使用基于电容耦合的分压方式在乘累加位线上得到分压后的计算值。为了进一步降低量化阵列间的波动影响,本发明采用单边逐次逼近型量化电路sar adc,其中dac阵列同样采用金属层电容,使得比较器差分输入端p/n极所连接的电路波动匹配。为了降低量化开销,提高能效,本发明采用依赖稀疏度的精度可调量化电路,对乘累加位线上的电压值进行量化,最

后通过外围的移位相加电路得到最终的多比特卷积计算结果。具有以下优点:

14.(1)采用乒乓式的存内计算电路,可以实现在计算的同时写入权重值,降低权重更新开销,提高吞吐率。

15.(2)采用金属层mom电容分压实现累加操作,配合电容式的单端逐次逼近型量化电路,降低芯片面积,有效对抗pvt波动,提高计算裕度和精度。

16.(3)采用依赖稀疏度的量化策略和软硬协同的方式,通过可调的量化精度配置,有效降低量化电路的功耗和延时,提高能效。

附图说明

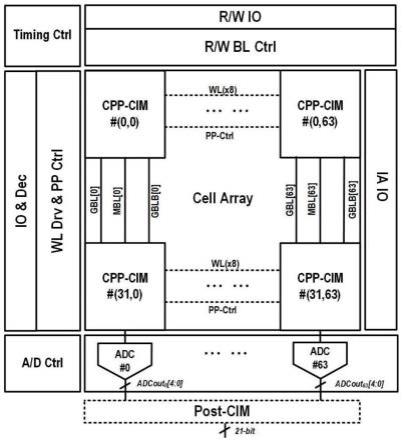

17.图1为本发明基于电容耦合的乒乓式存内计算电路的结构框图。

18.图2为本发明基于电容耦合的乒乓式存内计算电路的工作模式。

19.图3为本发明乒乓式存算单元。

20.图4为本发明乒乓式存算单元的功能波形图。

21.图5为本发明依赖稀疏度的精度可调量化电路。

22.图中有:第一nmos晶体管m1、第二nmos晶体管m2、第三nmos晶体管m3、第四nmos晶体管m4、第五nmos晶体管m5、pmos晶体管m6、第七nmos晶体管m7、写选通usel、计算选通csel;全局位线gbl、gblb、局部位线lbl、lblb、计算位线cbl、cblb、金属层mom电容cc、输入特征值信号ia、内部节点vc、乘累加位线mbl。

具体实施方式

23.本发明设计了可以同时进行计算和权重值更新的基于电容耦合的乒乓式存内计算电路,为了提高模拟域存内计算的线性度和面积效率,存算单元采用金属层电容作为计算媒介,使用基于电容耦合的分压方式在乘累加位线上得到分压后的计算值。为了进一步降低量化阵列间的波动影响,本发明采用单边逐次逼近型量化电路saradc,其中dac阵列同样采用金属层电容,使得比较器差分输入端p/n极所连接的电路波动匹配。为了降低量化开销,提高能效,本发明采用依赖稀疏度的精度可调量化电路,对乘累加位线上的电压值进行量化,最后通过外围的移位相加电路得到最终的多比特卷积计算结果。

24.本发明基于电容耦合的乒乓式存内计算电路核心设计包括:乒乓式存内计算单元、依赖稀疏度的精度可调量化电路。

25.乒乓式存算单元由1个上方乘单元ubmu、1个下方乘单元dbmu和1个乒乓式存内计算ppcc组成。乒乓式存内计算ppcc放在上方乘单元ubmu与下方乘单元dbmu之间。两个乘单元都是由4个紧凑的6t静态随机存储器和4个用于选通的nmos晶体管m1~m4组成。其中第一nmos晶体管m1、第二nmos晶体管m2栅极接到写选通usel信号,第三nmos晶体管m3、第四nmos晶体管m4栅极接到计算选通csel信号。写选通usel、计算选通csel是由外部的译码电路和时序控制电路产生,用于控制上方乘单元ubmu与下方乘单元dbmu是否进行计算或更新操作。两个乘单元共享乒乓式存内计算ppcc和写驱动电路。同一时钟周期内,上方乘单元ubmu与下方乘单元dbmu可以分别同时执行计算和更新权重值的操作,不同周期可以互换操作,从而实现乒乓式的操作,提高吞吐率。乒乓式存内计算ppcc由一个传输门(第五nmos晶体管m5和pmos晶体管m6组成)、一个第七nmos晶体管m7以及一个金属层mom电容cc组成。其中第

五nmos晶体管m5、pmos晶体管m6栅极接到计算位线cbl、cblb,源漏分别连接输入特征值信号ia和内部节点vc,第七nmos晶体管m7栅极接到计算位线cbl、cblb,源漏连接vc和gnd。cc是金属层mom电容,上下极板分别接到内部节点vc和乘累加位线mbl上。当计算之前复位时,输入特征值信号ia处于低电平,乘累加位线mbl也被拉到低电平,此时无论上一次的计算位线cbl、cblb的高低电平状态,内部节点vc和乘累加位线mbl都为低电平,计算金属层mom电容cc上电荷量清空。复位后开始计算,此时计算模式下的乘单元bmu读出对应存储单元的权重值到计算位线cbl、cblb上,此时输入特征值信号ia为输入特征值所对应电平,对应的点乘结果反应在内部节点vc上,乘累加位线mbl处于浮空状态,根据电荷守恒原理,乘累加位线mbl上得到的分压反映了同一列上32个cppcim块的乘累加结果。相比于电流域、时域和电荷共享的计算方案,本发明采用的电容耦合的计算方案,计算线性度较高,受到pvt波动影响较小。采用金属层电容,在提高面积效率的同时进一步降低了波动。

26.依赖稀疏度的精度可调量化电路,主要包括输入感知检测器和一个单边量化器。输入感知检测器的阈值,是通过外部软件对特定的神经网络进行训练,统计网络中每层的输入特征值的稀疏度,得到用于配置量化精度的阈值,在降低量化功耗和延时开销的同时,保证准确度。

27.输入感知检测器得到每个周期送入存算阵列的32个输入特征值信号ia中0的个数,通过和提前设定的阈值相比较,产生对应的精度配置控制信号,送到量化器。根据该精度配置信号,量化电路量化不同比特位数的值。如果精度配置为全精度5bit,则sar逻辑控制量化电路进行传统的全精度的二进制逼近式量化操作;如果精度配置为非全精度3bit,则sar逻辑控制量化器跳过高2bit的量化(即高2bit直接为0),直接进行低3bit的量化;如果精度配置为无需量化,则不开启量化,量化结果直接为0。

28.单边逐次逼近型量化电路saradc包括一个电容式的dac阵列、异步sar逻辑控制电路、动态锁存放大器和移位寄存器。其中电容式dac阵列采用金属层mom电容,电容容值分别为1c、1c、2c、4c、8c、16c,电容上级板共同接到放大器的n极,电容下级板通过开关电路分别接到参考电压vref1和vref2上。动态锁存放大器的p极连接计算阵列中得到的乘累加位线mbl,放大器的输出接到移位寄存器,通过控制信号控制移位,完成多比特的量化操作。移位寄存器的输出送到外围的移位相加电路,实现单比特乘累加到多比特乘累加的计算。

29.图1展示的式基于电容耦合的乒乓式存内计算电路的整体结构图。整个电路包括了32行64列的cppcim块、按列量化的量化阵列、读写驱动电路、译码电路、输入缓冲电路、时序控制电路、io电路以及移位相加电路。io电路得到锁存后的控制信号;输入特征值通过输入缓冲电路送到存算阵列;译码电路根据地址信号和模式信号产生对应的控制信号;时序电路产生复位、读写、计算、量化等自定时脉冲,从而控制各个操作的执行。本发明支持四种工作模式,分别是读模式、写模式、计算模式、计算同时更新权重值模式。同时支持软硬协同的精度可调配置,以及不同位数的数据的计算。

30.下面结合附图对发明的技术方案进行详细说明。

31.本发明基于电容耦合的乒乓式存内计算电路的结构框图如图1所示,在乒乓工作模式时,输入特征值经过右侧的输入缓冲iabuffer电路,通过缓冲并行送入计算阵列。左侧的译码电路处理地址信号和控制信号,打开对应的字线,将存储器内部的权重值读出到每个存算单元的ppcc,通过电容耦合分压,在乘累加位线mbl上得到对应的乘累加值,送入下

方的按列量化阵列进行量化,再通过外围的移位相加电路得到最终的计算值。

32.图2展示的是基于电容耦合的乒乓式存内计算电路的工作模式。本发明支持四种工作模式,分别是读模式、写模式、计算模式、计算同时更新权重值模式。同时支持软硬协同的精度可调配置,以及不同位数的数据的计算。io电路得到锁存后的控制信号;输入特征值通过输入缓冲电路送到存算阵列;要存入阵列的权重值通过写驱动电路进行更新;译码电路根据地址信号和模式信号产生对应的控制信号;时序电路产生复位、读写、计算、量化等自定时脉冲,从而控制各个操作的执行。

33.乒乓式存算单元如图3所示,是由1个上方乘单元ubmu、1个下方乘单元dbmu和1个乒乓计算单元ppcc组成。计算单元ppcc放在上方乘单元ubmu和下方乘单元dbmu之间。两个乘单元都是由4个紧凑的6t静态随机存储器和4个用于选通的nmos晶体管m1~m4组成。其中第一nmos晶体管m1、第二nmos晶体管m2栅极接到写选通usel信号,第三nmos晶体管m3、第四nmos晶体管m4栅极接到计算选通csel信号。上方乘单元ubmu、下方乘单元dbmu是由外部的译码电路和时序控制电路产生,用于控制上方乘单元ubmu、下方乘单元dbmu是否进行计算或更新操作。上方乘单元ubmu、下方乘单元dbmu共享乒乓式存内计算ppcc和写驱动电路。同一时钟周期内,上方乘单元ubmu、下方乘单元dbmu可以分别同时执行计算和更新权重值的操作,不同周期可以互换操作,从而实现乒乓式的操作,提高吞吐率。乒乓式存内计算ppcc由一个传输门(第五nmos晶体管m5和pmos晶体管m6组成)、一个第七nmos晶体管m7以及一个金属层mom电容cc组成。其中第五nmos晶体管m5和pmos晶体管m6栅极接到计算位线cbl、cblb,源漏分别连接输入特征值对应信号ia和内部节点vc,第七nmos晶体管m7栅极接到计算位线,源漏连接内部节点vc和地gnd。金属层mom电容cc上下极板分别接到内部节点vc和乘累加位线mbl上。当计算之前复位时,输入输入特征值对应信号ia处于低电平,乘累加位线mbl也被拉到低电平,此时无论上一次的计算位线cbl、cblb的高低电平状态,内部节点vc和乘累加位线mbl都为低电平,计算金属层mom电容cc上电荷量清空。复位后开始计算,此时计算模式下的上方乘单元bmum读出对应存储单元的权重值到计算位线cbl、cblb上,此时输入特征值对应信号ia为输入特征值所对应电平,对应的点乘结果反应在内部节点vc上,乘累加位线mbl处于浮空状态,根据电荷守恒原理,计算位线上得到的分压反映了同一列上32个cppcim块的乘累加结果。

34.图4展示的是乒乓式存算单元的功能波形图。前8个时钟周期展示的是上方乘单元ubmu进行计算,下方乘单元dbmu进行权重值更新的操作;后8个时钟周期展示的是上方乘单元ubmu进行权重值更新,下方乘单元dbmu进行计算的操作。输入特征值对应信号ia是经过缓冲后的带复位的输入特征值信号,内部节点vc是存算单元的点乘结果,乘累加位线mbl则是一列32行存算单元并行计算得到的乘累加值,adcout是该列量化电路的量化值,pdccout是经过移位相加电路后的值。8个时钟周期可以完成int8乘int8的近全精度的计算。

35.图5所示是依赖稀疏度的精度可调量化电路,主要包括输入感知检测器和一个单边逐次逼近型量化器。输入感知检测器的阈值,是通过外部软件对特定的神经网络进行训练,统计网络中每层的输入特征值的稀疏度,得到用于配置量化精度的阈值。输入感知检测器得到每个周期送入存算阵列的32个输入特征值对应信号ia中0的个数,通过和提前设定的阈值相比较,产生对应的精度配置控制信号,送到量化电路。根据该精度配置信号,量化电路量化不同比特位数的值。单边逐次逼近型量化器包括一个电容式的dac阵列、异步sar

逻辑控制电路、动态锁存放大器和移位寄存器。其中电容式dac阵列采用金属层mom电容,电容容值分别为1c、1c、2c、4c、8c、16c,电容上级板共同接到放大器的差分输入端n极,电容下级板通过开关电路分别接到参考电压vref1和vref2上。动态锁存放大器的差分输入端p极连接计算阵列中得到的乘累加位线mbl,放大器的输出接到移位寄存器,通过控制信号控制移位,完成多比特的量化操作。移位寄存器的输出送到外围的移位相加电路,实现单比特乘累加到多比特乘累加的计算。

36.以上所述仅是本发明的优选实施方式,应当指出:对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1