半导体存储装置及其写入方法与流程

本发明是关于一种半导体存储装置,特别是关于具有真存储单元以及互补存储单元的半导体存储装置及其写入验证方法。

背景技术:

1、在可变电阻式存储器中,通过对可变电阻元件施加脉冲电压,以可逆且非挥发地存储数据。可变电阻元件例如包括氧化铪等金属氧化物的薄膜,并通过所施加的脉冲电压的大小及极性,而成为高电阻状态或低电阻状态。例如,将可变电阻元件写入为低电阻状态称为“设定”,将可变电阻元件写入为高电阻状态称为“重置”。可变电阻式存储器分为“单极性”与“双极性”。单极性是在设定和重设时,对可变电阻元件施加极性相同的写入电压。双极性则是在设定和重设时,对可变电阻元件施加极性相反的写入电压。

2、图1表示现有的可变电阻式存储器的1t1r存储单元阵列的示意图。存储单元mc包含:连接于源极线与位线之间的1个可变电阻元件以及1个存取用晶体管,能够逐位地进行选择。例如,在写入时,通过字线wl1选择列方向的存取用晶体管,并于位线bl1、源极线sl1之间施加写入脉冲电压,以设定或重置所选择的可变电阻元件。在读取时,通过字线wl1选择列方向的存取用晶体管,并于位线bl1、源极线sl1之间施加读取用电压,以感测流入所选择的可变电阻元件的电流或电压。

3、图2表示现有的可变电阻式存储器的2t2r存储单元阵列的示意图。2t2r存储单元使用一对可变电阻元件和一对存取晶体管来存储互补数据。例如,真存储单元mc11包含:连接于源极线sl1与位线bl1之间的可变电阻元件以及存取用晶体管,此可变电阻元件储存真数据(例如低电阻状态);互补存储单元包含:连接于源极线与位线之间的可变电阻元件以及存取用晶体管,此可变电阻元件储存真存储单元mc11的互补数据(例如高电阻状态)。

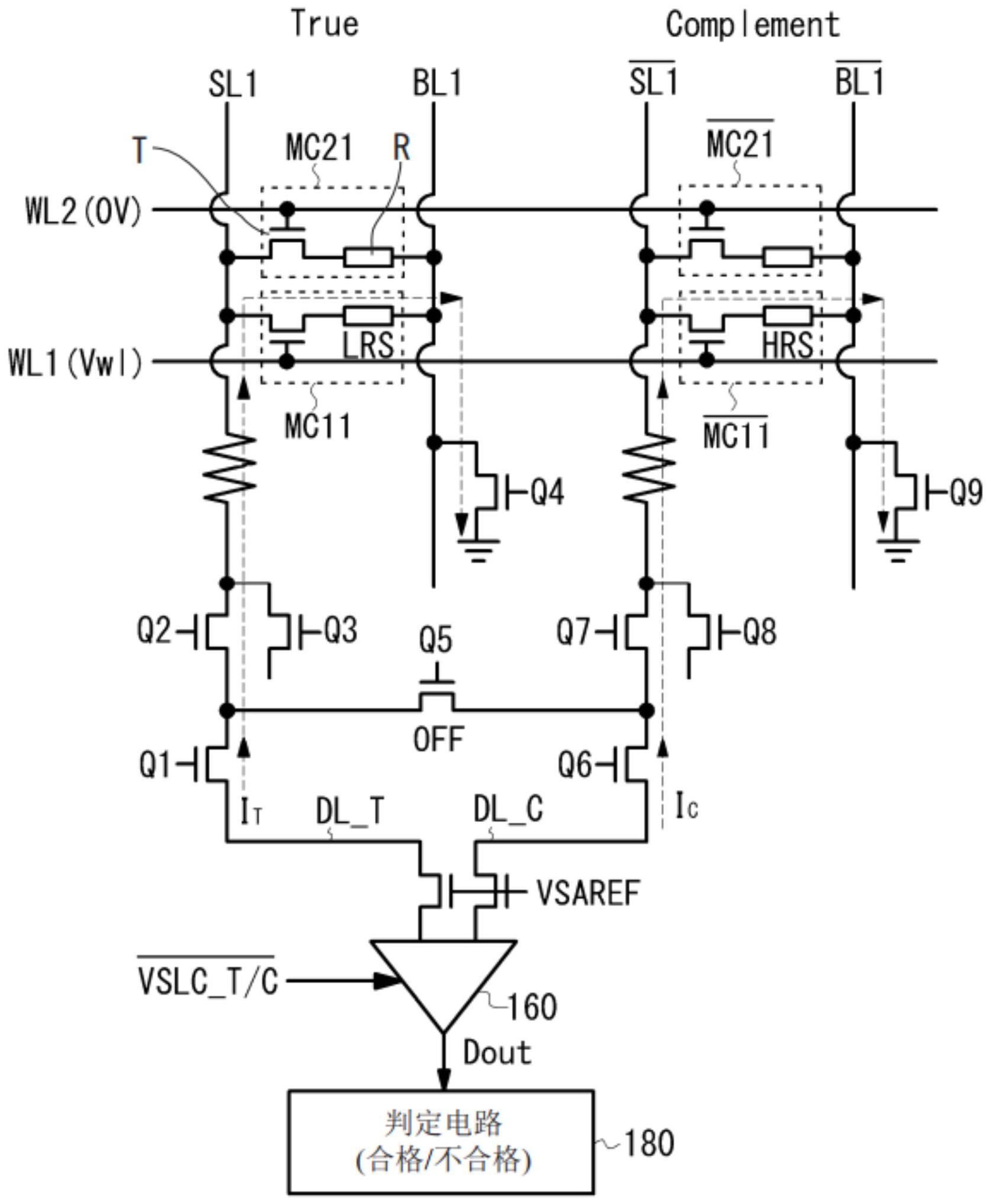

4、在现有的可变电阻式存储器(如日本特许5748877号公报所示)中,2t2r存储单元的读取,是通过检测真存储单元流通的电流以及互补存储单元流通的电流之间的电流差来进行。图3表示一对存储单元mc11、的读取范例。假定真存储单元mc11的可变电阻元件为低电阻状态(lrs),且互补存储单元的可变电阻元件为高电阻状态(hrs)。

5、详细来说,对选择字线wl1施加读取电压vw1,使得存储单元mc11、的存取用晶体管导通;对非选择字线wl2施加0v,使得非选择存储单元mc21、的存取用晶体管断开。存储单元mc11的源极线sl1通过晶体管q1、q2与感测放大器10的其中一个输入结合,位线bl1通过晶体管q4与接地电位gnd连接。另外,存储单元的源极线通过晶体管q6、q7与感测放大器10的另外一个输入结合,位线通过晶体管q9与gnd连接。连接于源极线sl1与源极线之间的晶体管q5断开,连接于源极线与基准电流产生单元30之间的晶体管q10断开。

6、为了活化感测放大器10,利用vsaref信号将晶体管导通,使源极线sl1、与感测放大器10电连接,感测放大器10会检测从源极线sl1通过存储单元mc11流入位线bl1的读取电流it、以及从源极线通过存储单元流入位线的读取电流ic之间的电流差δi(=|it-ic|),并根据这个检测结果输出“1”或“0”的数据dout。

7、图4是设定/重置时流入可变电阻元件的电流分布的一个范例。在初始阶段,流入hrs的可变电阻元件的电流hrs_initial、以及流入lrs的可变电阻元件的电流lrs_initial之间,有比较大的裕度,但随着写入可变电阻元件的次数增加,形成于可变电阻元件的电极间的纤维状电流路径将老化,使得保存特性或耐久特性恶化,如电流hrs_drift、电流lrs_drift所示,电流分布的幅度就会变宽,并产生所谓的尾位(tail bit)位移,使得电流hrs_drift与电流lrs_drift之间的裕度变窄。如此一来,感测放大器10就有可能无法正确地检测电流差δi,而无法输出正确的数据。

8、例如,假设初始状态的电流分布hrs_initial的上限值为3μa,且电流分布lrs_initial的下限值为16μa。在存储数据“0”时(hrs):流入真存储单元mc11的读取电流为3μa,流入互补存储单元的读取电流为16μa。电流差δi=13μa,由于裕度充足,因此感测放大器10能够正确地检测电流差,并输出数据“0”。此外,在存储数据“1”时(lrs):流入真存储单元mc11的读取电流为16μa,流入互补存储单元的读取电流为3μa。电流差δi=13μa,由于裕度充足,因此感测放大器10能够正确地检测电流差,并输出数据“1”。

9、此处,假设发生尾位位移,电流分布hrs_drift的上限值变为6μa(位移+3μa),电流分布lrs_drift的下限值变为10μa(位移-6μa)。在存储数据“0”时:流入真存储单元mc11的读取电流为6μa,流入互补存储单元的读取电流为10μa。电流差δi=4μa,由于裕度太小,因此感测放大器10可能无法正确地检测电流差,而无法输出数据“0”。此外,在存储数据“1”时:流入真存储单元mc11的读取电流为10μa,流入互补存储单元的读取电流为6μa。电流差δi=4μa,由于裕度太小,因此感测放大器10可能无法正确地检测电流差,而无法输出数据“1”。

10、为了正确地检测电流差δi,在设定/重置写入时的验证阶段,会进行所需裕度的设定。图5表示现有的重置写入时的验证操作的流程。未图示的控制电路一旦接受写入数据“0”(s10),就对真存储单元施加重置脉冲(s20)。例如,若对真存储单元mc11进行重置写入,则通过晶体管q3对源极线sl1施加重置写入脉冲。

11、接着,对真存储单元进行重置验证(s30)。若验证不合格,则再次施加重置写入脉冲,并不断重复验证,直到最终重置验证合格为止,接着,对互补存储单元施加设定脉冲(s40)。例如,若对互补存储单元进行设定写入,则通过晶体管q9对位线施加设定写入脉冲。接着,对互补存储单元进行设定验证(s50)。若验证不合格,则再次施加设定写入脉冲,并不断重复验证,直到最终设定验证合格为止,然后结束重置写入。另外,设定写入时,同样也是对真存储单元施加设定写入脉冲,然后进行设定验证,若设定验证合格,就接着对互补存储单元施加重置写入脉冲,然后进行重置验证。例如,若欲对真存储单元mc11进行设定写入,则通过晶体管q4对位线bl1施加设定写入脉冲。

12、图6表示真存储单元mc11的设定验证的操作。图7表示互补存储单元的重置验证的操作。于设定验证中,感测放大器10检测真存储单元mc11流通的电流iset以及基准电流产生单元30产生的设定验证用的基准电流iref之间的电流差,判定电路20基于检测的电流差,来判定设定验证是否合格。进行设定验证时,晶体管q6断开,感测放大器10与源极线分离;晶体管q10导通,感测放大器10与基准电流产生单元30结合。

13、在重置验证中,如图7所示,感测放大器10检测互补存储单元流通的电流ireset、以及基准电流产生单元30产生的重置验证用的基准电流iref之间的电流差,判定电路20基于检测的电流差,来判定重置验证是否合格。进行重置验证时,晶体管q2断开,晶体管q5导通,由源极线来取代源极线sl1,与感测放大器10结合。

14、这种现有的可变电阻式存储器的验证方式有以下问题:如图5所示,若是执行重置写入,则需要分别进行真存储单元的重置验证、以及互补存储单元的设定验证;若是执行设定写入,则需要分别进行真存储单元的设定验证、以及互补存储单元的重置验证。换言之,每进行1次设定或重置写入时,就需要至少验证2次,使得写入所需的时间拉长。

15、另外,由于源极线的配线电阻或负载电容,会随着选择存储单元的位置不同而改变,因此,读取电流iset/电流ireset也会随着选择存储单元的位置而改变。例如,若距离感测放大器10最远的存储单元的读取电流变得太小,则难以检测与基准电流iref之间的电流差,使得验证的判定有可能产生错误。因此,就需要根据选择存储单元的位置,来调整读取的偏压条件(wl/sl/bl的准位)或基准电流,而产生电路复杂化或增加面积的问题。

技术实现思路

1、本发明是为了解决上述的现有技术的问题,而提供一种半导体存储装置,能够避免电路复杂化或增加面积,同时保障验证精准度,并缩短写入时间。

2、本发明相关的半导体存储装置,包含:存储单元阵列,写入驱动器以及读取偏压电路,控制电路,以及感测放大器。存储单元阵列,包含多个存储单元。写入驱动器以及读取偏压电路,被配置为将对应写入数据及其互补数据的写入脉冲与互补写入脉冲,分别施加到该存储单元阵列之中选择的一对存储单元。控制电路,被配置为输出基于该写入数据而产生的验证感测负载控制信号。感测放大器,被配置为在施加该写入脉冲与该互补写入脉冲后,接收该验证感测负载控制信号,且检测该选择的一对存储单元中,真存储单元所连接的第1数据线流通的电流、以及互补存储单元所连接的第2数据线流通的电流的电流差,其中该控制电路经由该验证感测负载控制信号控制对该第1数据线及该第2数据线的至少一个提供追加电流,使得该电流差至少为所需裕度。

3、本发明相关的半导体存储装置的写入方法,用以对半导体存储装置的存储单元阵列中选择的一对存储单元进行写入,该写入方法包含:接受写入数据;对该选择的一对存储单元中的真存储单元施加写入脉冲;对该选择的一对存储单元中的互补存储单元施加与该写入脉冲互补的互补写入脉冲;基于该写入数据产生验证感测负载控制信号;在施加该写入脉冲与该互补写入脉冲后,通过该半导体存储装置的感测放大器接收该验证感测负载控制信号,且检测该选择的一对存储单元中,该真存储单元所连接的第1数据线流通的电流、以及该互补存储单元所连接的第2数据线流通的电流的电流差。其中,在检测出该电流差前,基于该验证感测负载控制信号对该第1数据线及该第2数据线的至少一个提供追加电流,使得该电流差至少为所需裕度。

4、根据本发明,在写入时的验证中,会检测其中一个存储单元连接的第1数据线流通的电流、以及另外一个存储单元连接的第2数据线流通的电流的电流差,因此,即使数据线的配线电阻或负载电容,因为选择的存储单元的位置而有所改变,也可以通过电流差,来抵销配线电阻或负载电容。另外,基于写入数据,对第1数据线或第2数据线追加电流,使得电流差变大,因此,能够保障验证精确度,就算高电阻状态以及低电阻状态的电流分布产生偏移,也能够在正确进行读取的电流差确保之前,来进行设定以及重置写入。另外,由于并不需要根据选择存储单元的位置,来调整读取的偏压条件(wl/sl/bl的准位)或基准电流,因此能够避免电路复杂化或增加面积。

- 还没有人留言评论。精彩留言会获得点赞!