非易失性存储器件的制作方法

本公开涉及存储器件,并且更具体地涉及通过以接合(bonding)方式将其中布置有存储单元的第一芯片连接到其中布置有外围电路的第二芯片而获得的三维(3d)非易失性存储器件。

背景技术:

1、相关存储器件可以用于存储数据并且可以包括易失性存储器件和非易失性存储器件。由于要求非易失性存储器件的高电容和微型化,已经开发出在垂直于外围电路的方向上布置存储单元阵列的相关3d存储器件。3d存储器件的示例可以包括其中布置有存储单元的第一半导体芯片和其中布置有外围电路的第二半导体芯片以接合方式彼此连接的芯片到芯片(c2c)存储器件。在c2c存储器件的情况下,随着布置在第一半导体芯片上的字线的数目增加,对应于字线的通道晶体管(pass transistor)的数目也会增加。因而,用于字线和通道晶体管之间的连接的金属层的数目或者布线复杂度会增加,这会导致c2c存储器件的尺寸及其制造成本增加。

技术实现思路

1、本公开提供一种非易失性存储器件,在该非易失性存储器件中,用于芯片到芯片(c2c)存储器件内的布线连接的金属层的数目以及布线复杂度降低,使得c2c存储器件的尺寸及其制造成本可以减少。

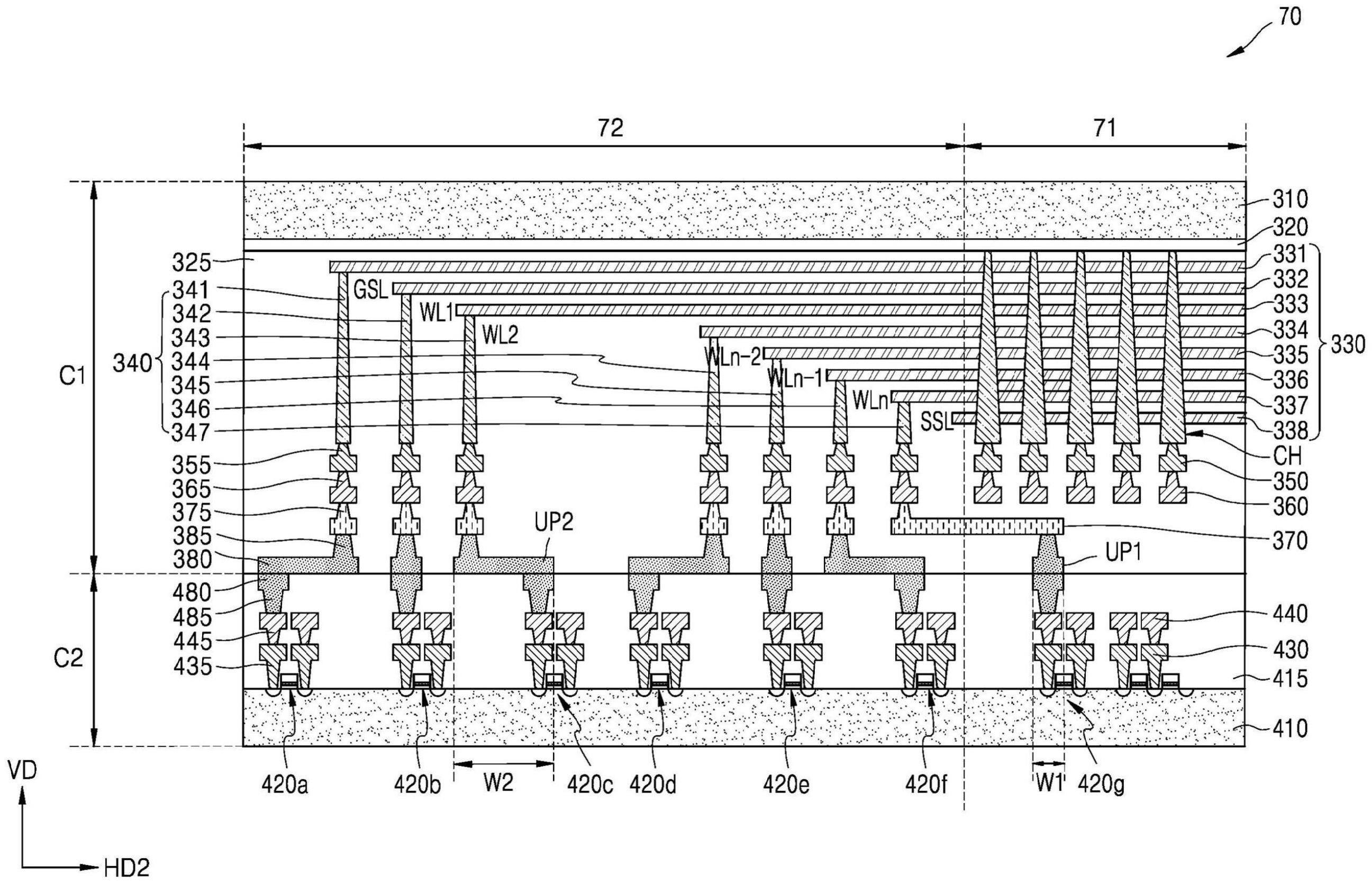

2、根据本公开的一方面,提供一种非易失性存储器件。所述非易失性存储器件包括第一半导体芯片和第二半导体芯片。所述第一半导体芯片包括:多个栅电极,每个所述栅电极在第一方向上延伸并且在第二方向上堆叠;沟道结构,所述沟道结构在第一区域中沿所述第二方向延伸;多个单元接触插塞;线性金属图案,所述线性金属图案在所述第一方向上延伸;以及多个上接合焊盘,所述多个上接合焊盘包括第一上接合焊盘、第二上接合焊盘和第三上接合焊盘。所述多个单元接触插塞包括第一单元接触插塞、第二单元接触插塞和第三单元接触插塞。所述多个单元接触插塞中的每个单元接触插塞在第二区域中耦接到所述多个栅电极中的对应栅电极。所述第二半导体芯片包括:多个下接合焊盘、与所述沟道结构交叠的第一外围电路元件、与所述多个单元接触插塞交叠的第二外围电路元件以及与所述多个单元接触插塞交叠的第三外围电路元件。所述多个下接合焊盘包括第一下接合焊盘、第二下接合焊盘和第三下接合焊盘。所述第一单元接触插塞通过所述线性金属图案、所述第一上接合焊盘和所述第一下接合焊盘耦接到所述第一外围电路元件。所述第二单元接触插塞通过所述第二上接合焊盘和所述第二下接合焊盘耦接到所述第二外围电路元件。所述第三单元接触插塞通过所述第三上接合焊盘和所述第三下接合焊盘耦接到所述第三外围电路元件。所述第二上接合焊盘在所述第一方向上的宽度不同于所述第三上接合焊盘在所述第一方向上的宽度。所述第二下接合焊盘在所述第一方向上的宽度不同于所述第三下接合焊盘在所述第一方向上的宽度。

3、根据本公开的一方面,提供一种非易失性存储器件。所述非易失性存储器件包括第一半导体芯片和第二半导体芯片。所述第一半导体芯片包括:多个栅电极,每个所述栅电极在第一方向上延伸并且在第二方向上堆叠;沟道结构,所述沟道结构在第一区域中沿所述第二方向延伸;单元接触插塞,每个所述单元接触插塞在第二区域中耦接到所述多个栅电极中的对应栅电极;第一上接合焊盘;以及第二上接合焊盘。所述第二半导体芯片包括:第一下接合焊盘、第二下接合焊盘、与所述沟道结构交叠的第一外围电路元件以及与所述单元接触插塞交叠的第二外围电路元件。所述单元接触插塞中的第一单元接触插塞通过所述第一上接合焊盘和所述第一下接合焊盘耦接到所述第一外围电路元件。所述单元接触插塞中的第二单元接触插塞通过所述第二上接合焊盘和所述第二下接合焊盘耦接到所述第二外围电路元件。所述第二上接合焊盘和所述第二下接合焊盘在所述第一方向上具有第一宽度。所述第一上接合焊盘和所述第一下接合焊盘中的至少一者在所述第一方向上具有大于所述第一宽度的第二宽度。

4、根据本公开的一方面,提供一种非易失性存储器件。所述非易失性存储器件包括第一半导体芯片和第二半导体芯片。所述第一半导体芯片包括存储单元阵列、在第一方向上具有第一宽度的第一上接合焊盘以及在所述第一方向上具有大于所述第一宽度的第二宽度的第二上接合焊盘。所述第二半导体芯片包括第一下接合焊盘,并且通过所述第一上接合焊盘和所述第一下接合焊盘在垂直方向上耦接到所述第一半导体芯片。所述第二半导体芯片还包括:第二下接合焊盘,所述第二下接合焊盘耦接到所述第二上接合焊盘;第三下接合焊盘,所述第三下接合焊盘耦接到所述第二上接合焊盘;第一外围电路元件,所述第一外围电路元件耦接到所述第二下接合焊盘;以及第二外围电路元件,所述第二外围电路元件耦接到所述第三下接合焊盘。所述第一外围电路元件通过所述第二下接合焊盘、所述第二上接合焊盘和所述第三下接合焊盘耦接到所述第二外围电路元件。

技术特征:

1.一种非易失性存储器件,包括:

2.根据权利要求1所述的非易失性存储器件,其中,所述第二上接合焊盘在所述第一方向上的宽度大于所述第一上接合焊盘在所述第一方向上的宽度。

3.根据权利要求1所述的非易失性存储器件,其中,所述第二下接合焊盘在所述第一方向上的宽度大于所述第一下接合焊盘在所述第一方向上的宽度。

4.根据权利要求1所述的非易失性存储器件,其中,所述第一上接合焊盘和所述第一下接合焊盘在所述第一方向上具有第一宽度,

5.根据权利要求1所述的非易失性存储器件,其中,所述栅电极包括串选择线、多条字线和接地选择线,

6.根据权利要求1所述的非易失性存储器件,其中,所述第一外围电路元件、所述第二外围电路元件和所述第三外围电路元件提供行译码器。

7.根据权利要求1所述的非易失性存储器件,其中,所述第一半导体芯片还包括:

8.根据权利要求7所述的非易失性存储器件,其中,所述第四外围电路元件和所述第五外围电路元件提供页缓冲器电路。

9.根据权利要求1所述的非易失性存储器件,其中,所述第一半导体芯片还包括:

10.根据权利要求9所述的非易失性存储器件,其中,所述第四外围电路元件提供公共源极线驱动器。

11.一种非易失性存储器件,包括:

12.根据权利要求11所述的非易失性存储器件,其中,所述栅电极包括串选择线、多条字线和接地选择线,

13.根据权利要求11所述的非易失性存储器件,其中,所述第一半导体芯片还包括第三上接合焊盘,所述第三上接合焊盘在所述第一方向上具有所述第二宽度,

14.根据权利要求11所述的非易失性存储器件,其中,所述第一半导体芯片还包括:

15.根据权利要求11所述的非易失性存储器件,其中,所述第一半导体芯片还包括:

16.一种非易失性存储器件,包括:

17.根据权利要求16所述的非易失性存储器件,其中,所述第二半导体芯片还包括:

18.根据权利要求16所述的非易失性存储器件,其中,所述第二半导体芯片还包括:

19.根据权利要求18所述的非易失性存储器件,其中,所述第一半导体芯片还包括第三上接合焊盘,所述第三上接合焊盘在所述第一方向上具有所述第三宽度,并且

20.根据权利要求16所述的非易失性存储器件,其中,所述存储单元阵列包括第一存储单元阵列和第二存储单元阵列,

技术总结

在一些实施例中,一种非易失性存储器件包括第一半导体芯片和第二半导体芯片。所述第一半导体芯片包括栅电极、沟道结构、多个单元接触插塞、线性金属图案和多个上接合焊盘。所述第二半导体芯片包括多个下接合焊盘、与所述沟道结构交叠的第一外围电路元件、与所述多个单元接触插塞交叠的第二外围电路元件以及与所述多个单元接触插塞交叠的第三外围电路元件。所述外围电路元件耦接到对应的单元接触插塞。所述第二上接合焊盘和所述第三上接合焊盘在所述第一方向上的宽度彼此不同,并且所述第二下接合焊盘和所述第三下接合焊盘在所述第一方向上的宽度彼此不同。

技术研发人员:赵栢衡,边大锡

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!