用于存储器单元的方法及其电路结构与流程

本公开涉及将非易失性存储器转换成只读存储器(“rom”)的领域,并且特别地涉及使用单个掩模来将编程到非易失性存储器阵列中的代码转换成rom代码。

背景技术:

1、存在很多电路应用,其中产品要求在产品开发的初始阶段期间以及在测试的第一部分期间并且甚至在现场使用期间使用诸如eeprom等非易失性存储器。例如,汽车、电梯、微控制器和各种其他任务专用asic芯片具有控制程序操作的一部分存储存储器。在操作开发的初始阶段,该存储器必须被写入,进行算法测试,并且然后进行多次修改。一旦代码被确认为准确且最终,则非易失性存储器被替换为只读存储器(“rom”)。这确保了编程中不会出错并且代码不会被进一步修改。这在诸如汽车、建筑物控制、飞机等高生产机器中使用的微控制器中特别有益。因此,广泛使用其中微控制器具有如下部分的电路:该部分最初是可写存储器,通常存储为诸如eeprom等非易失性存储器,并且然后,一旦代码在现场已经被测试并且证明是准确之后完成,它必须存储在rom中,因此不能被改变或不会发生编程错误。

2、在现有技术中,当非易失性存储器替换为rom时,这需要完全改变针对微处理器的全掩模集合。由于大多数rom具有与eeprom或其他非易失性存储器明显不同的布局和单元设计,因此对整个半导体管芯的整个布局和平面图有显著影响。这引起设计结构、整个管芯中信号传输的定时(例如,由于线路长度和接口的变化)以及管芯的不同部分之间的进一步集成的变化。因此,仅将非易失性存储器电路改变为标准rom有时需要完整的集成电路芯片重新设计和布局,这具有非常高的费用,可能花费几个月,并且可能不幸地在重新设计中传播错误,因为随着时钟信号对电路的每个部分的新的定时和其他变化而需要新的布局。

技术实现思路

1、根据本文中讨论的原理,使用完全相同的架构、晶体管、存储器单元和布局来将非易失性存储器转换成只读存储器(“rom”)。这种转换是在完全相同的集成电路管芯上使用相同的布局、设计和定时来完成的,其中只需对存储器阵列中的上部层级掩模进行单次改变。这允许灵活地将编程代码存储为非易失性存储器代码,并且然后在由客户选择的定时可以将来自可以写入的代码中的一些或全部代码转换成存储在rom中的只读代码。

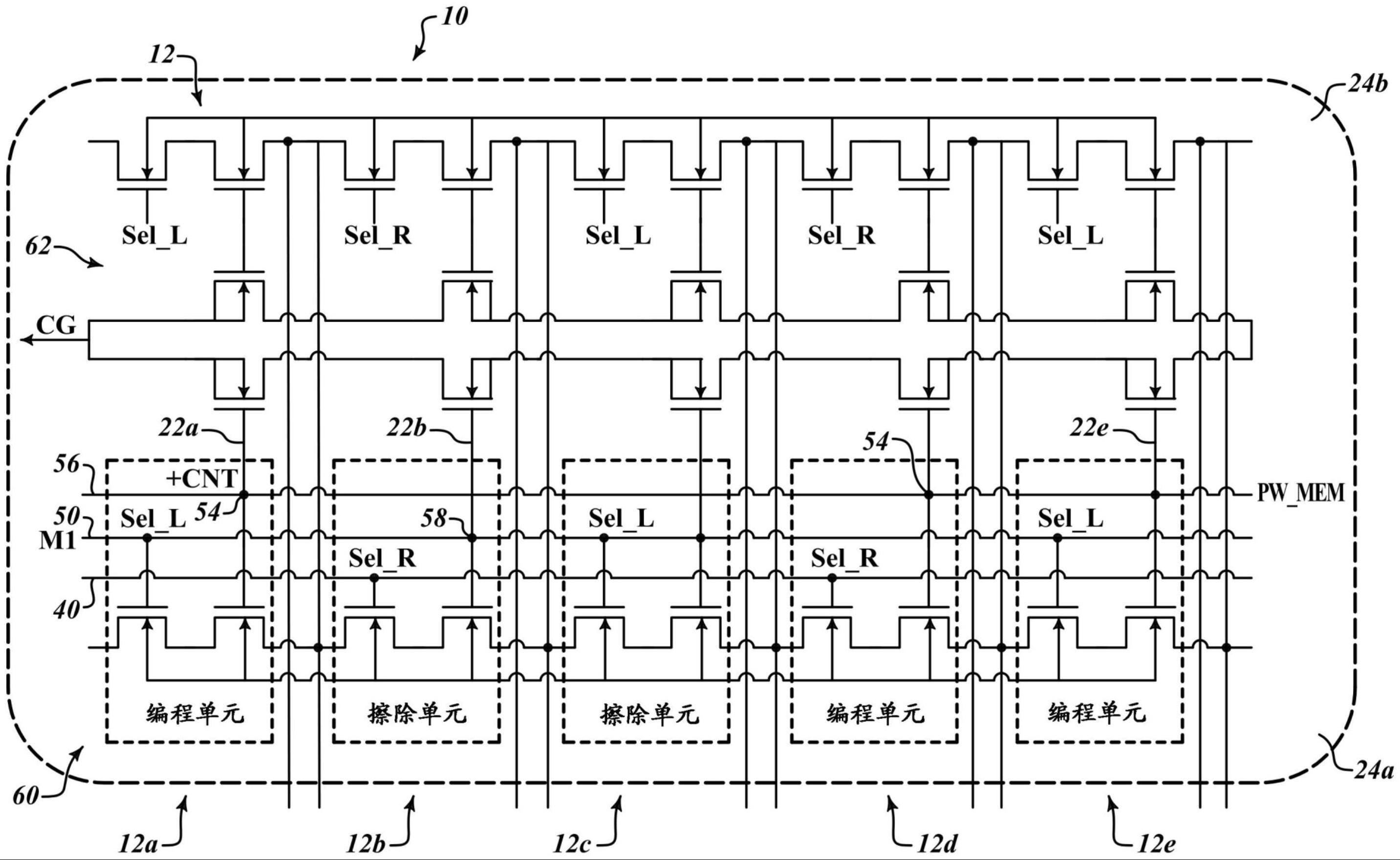

2、根据本文中教导的本公开的原理,提供了用于提供非易失性存储器的eeprom结构的布局。编程代码可以写入eeprom结构的存储器单元以生成逻辑“1”或逻辑“0”,并且根据期望的软件代码将其存储在各个存储器单元中,该软件代码控制微控制器的操作。针对微控制器编写期望的代码,并且在产品生成的开发和早期阶段期间对其进行多种潜在的操作模式测试。管芯的制造商以及客户能够将期望的代码编程到eeprom结构中并且根据不同的场景来操作它,以便确保代码在产品在微控制器的控制下在使用期间可能遇到的所有可能条件下正确运行。在代码已被确认为所有条件下正确和准确之后,该代码的数据存储在完全相同的结构中以作为只读存储器代码。特别地,以前是eeprom、浮置栅极结构的结构被转换为变成rom结构,并且代码被永久地写入结构中作为固件。存储器的该部分从eeprom改变为rom,其中最终代码存储在该rom中作为只能读取但永远不能改变的硬连线代码“1”和“0”,因为数据以各个存储器单元内部的实际物理连接的形式被存储。

3、根据一个提出的解决方案,存储器阵列可以分成两个或更多个部分,第一部分可以是可修改的以使得阵列的该部分不被转换成rom版本,而是保持为eeprom。存储器阵列的该部分具有应用仍然可以被修改的优点和灵活性,并且代码可以被改变。因此,可以在存储器的该部分中进一步改变控制系统操作的代码,并且允许在产品在现场使用时可以进一步调节微控制器操作。存储器的第二部分可以使代码完全冻结在其中。即,eeprom存储器的一部分被转换成存储器的rom版本,其具有存储在存储器内的硬件中的代码并且永远不能被改变。eeprom可以具有被保持为可写存储器的两个或更多个部分以及其中存储器的结构被转换成rom的两个或更多个部分,在该rom中,代码被冻结并且只能被读取而不能进行进一步的修改。

4、根据本文中教导的原理,通过改变位于上部金属层的金属掩模将非易失性存储器转换成rom。特别地,在硅管芯上构建标准eeprom阵列。期望测试的代码被编程到eeprom中,其中单元被编程为“1”或“0”。在代码已被确认准确之后,改变单个金属掩模以将eeprom的浮置栅极硬连线到不同的电压水平以创建rom,这取决于单元被编程为“1”还是“0”。如果特定存储器单元被编程为“1”,则针对该特定单元修改金属掩模以将浮置晶体管的栅极硬连线连接到选择晶体管的栅极。这种金属耦合确保特定位始终存储逻辑电平“1”。另一方面,如果期望在作为擦除单元的单元中存储逻辑电平“0”,则相同的金属掩模具有用于将浮置栅极连接到p阱的接触件,浮置栅极的本体连接到该p阱。这将浮置栅极连接到作为存储晶体管的本体的p阱,并且因此在该特定存储器单元中永久地存储“0”。这允许存储在eeprom中的代码永久地存储在完全相同的存储器单元中,这些存储器单元从eeprom单元转换成rom单元。

技术特征:

1.一种存储器单元,包括:

2.根据权利要求1所述的存储器单元,

3.根据权利要求2所述的存储器单元,其中所述浮置栅极是多晶硅。

4.根据权利要求1所述的存储器单元,还包括在所述衬底中位于所述第一阱与所述第二阱之间的隔离区,所述隔离区域与所述第一阱和所述第二阱间隔开。

5.根据权利要求4所述的存储器单元,其中所述隔离区是n掺杂阱。

6.根据权利要求1所述的存储器单元,其中所述第一阱和所述第二阱是p掺杂阱。

7.根据权利要求1所述的存储器单元,还包括耦合到所述第一阱的第一位线。

8.根据权利要求1所述的存储器单元,还包括在所述衬底中的第三阱,其中所述第一阱和所述第二阱中的每一者延伸到所述第三阱中并且具有与所述第三阱的导电类型相反的导电类型。

9.根据权利要求8所述的存储器单元,其中所述第一阱与所述第二阱通过所述第三阱的一部分而彼此间隔开。

10.根据权利要求8所述的存储器单元,还包括在所述第三阱下方的掩埋层,以及延伸通过所述第一阱和所述第二阱之间的所述第三阱到所述掩埋层中的隔离区。

11.根据权利要求1所述的存储器单元,还包括

12.一种器件,

13.根据权利要求12所述的器件,其中所述存储器单元中的每个存储器单元包括:

14.根据权利要求12所述的器件,其中所述第二阱是针对浮置栅极晶体管的控制栅极,并且控制栅极电极被耦合到所述第二阱。

15.根据权利要求12所述的器件,其中所述存储器单元中的每个存储器单元还包括掩埋层,并且所述隔离区域在所述第一阱与所述第二阱之间延伸到所述掩埋层中。

16.根据权利要求12所述的器件,其中所述第一阱和所述第二阱是p掺杂阱。

17.一种器件,包括:

18.根据权利要求17所述的器件,其中所述存储器阵列中的每个存储器阵列包括:

19.根据权利要求18所述的器件,其中所述第二阱是针对浮置栅极晶体管的控制栅极,其中控制栅极电极被耦合到所述第二阱。

技术总结

本文公开了用于存储器单元的方法及其电路结构。根据本文中讨论的原理,提供EEPROM单元,并且然后在测试代码之后,使用完全相同的架构、晶体管、存储器单元和布局来将EEPROM单元转换成只读存储器(“ROM”)单元。这种转换是在完全相同的集成电路管芯上使用相同的布局、设计和定时来完成的,其中只需对存储器阵列中的上部层级掩模进行单次改变。在一个实施例中,掩模改变是将金属1连接到多晶硅的过孔掩模。这允许灵活地将编程代码存储为非易失性存储器代码,并且然后在由客户选择时在测试之后,来自可以写入只读代码的代码的一些或全部代码存储在由相同的晶体管组成并且具有相同的布局的ROM单元中。

技术研发人员:F·德桑蒂斯,V·拉纳

受保护的技术使用者:意法半导体股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!