编程电压控制电路和存储芯片的制作方法

本公开涉及存储芯片,尤其涉及一种program(编程)电压控制电路和存储芯片。

背景技术:

1、对于存储芯片,特别是基于etox(eprom with tunnel oxide或者erasableprogrammable read only memory with tunnel oxide,可擦除可编程只读寄存器隧道氧化层)技术的产品如nand flash(一种非易失闪存)或者nor flash(一种非易失闪存)中,通常会利用hci(hot carrier injection,热载流子注入)效应给memory array(存储阵列)编程来提高阈值电压。具体说就是gate(门)端加一个高压,漏端加一个高压,源端和体接地,利用hci效应使得电子进入浮栅中来提高阈值电压。

2、在此过程中漏端和源端的电压差(program电压)会直接影响编程效率,如果电压差太低,则电子不容易进入浮栅中,而如果电压差太高,则会引起潜在的可靠性问题。所以需要编程电压精确可控。

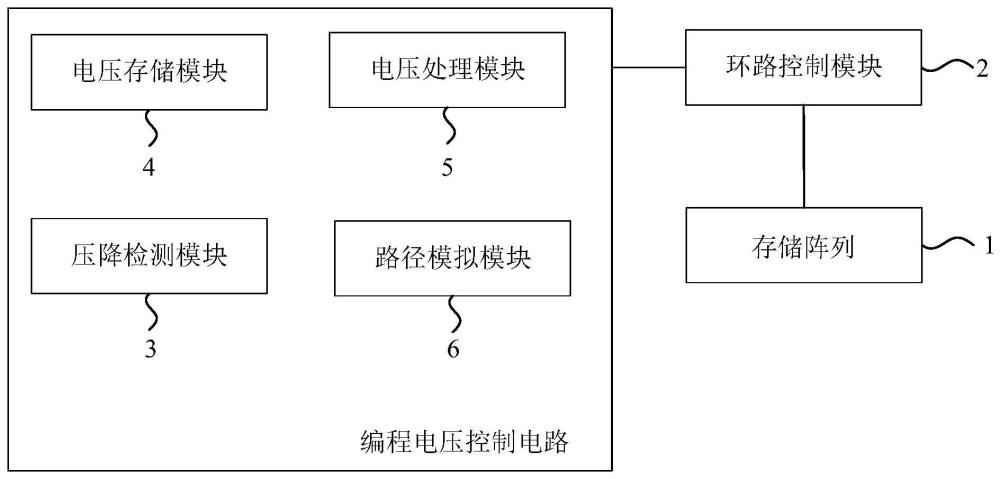

3、图1为flash现有的存储结构示意图,包括了环路控制器(也称为环路控制模块)。其中环路控制器包括第一输入端、第二输入端和电压输出端,其中第一输入端接预设参考电压vref,电压输出端与第二输入端以及存储阵列的输入端电连接,program时第二输入端的电压值v(n2)与vref成预设比例关系。现有memory array会包括若干选通开关和memorycell(存储单元),预先设定的编程电压(program voltage)到对应的memory cell的路径上会经过对应的选通开关(ysc,ysb,ysa)来译码出相应地址的memory cell,这些选通开关会因有编程电流流过而产生电压降irdrop。此电压降会随着工艺和温度变化而变化,导致真正到达被编程memory cell漏端的实际编程电压v(n2)-irdrop与预先设定的编程电压v(n2)不相符,存在电压差irdrop,且此电压差由于工艺、温度的影响变化,导致电压不确定,导致编程时间加长,直接影响了编程效率,同时降低了存储芯片的可靠性。

技术实现思路

1、本公开要解决的技术问题是为了克服现有技术中由于到达被编程cell端的实际编程电压与预先设定的编程电压不相符,过高影响可靠性,过低存在电压差导致编程时间加长,直接影响了编程效率,降低了存储芯片的可靠性的缺陷,提供一种编程电压控制电路和存储芯片。

2、本公开是通过下述技术方案来解决上述技术问题:

3、第一方面,提供一种编程电压控制电路,所述编程电压控制电路设于存储芯片中,所述存储芯片中包括与存储阵列的输入端连接的环路控制模块;

4、所述编程电压控制电路包括压降检测模块、电压存储模块、电压处理模块和路径模拟模块;

5、其中,所述路径模拟模块用于模拟所述存储阵列中任一选通电路和对应的存储单元;

6、在压降检测过程中,所述存储阵列处于待编程状态,所述环路控制模块和所述路径模拟模块电连接,所述压降检测模块分别与所述路径模拟模块、所述电压存储模块电连接;

7、所述压降检测模块用于检测所述存储阵列的输入端对应的初始编程电压,和所述环路控制模块输出的初始输出电压,基于所述初始输出电压和所述初始编程电压的差值,得到目标压降值,并将所述目标压降值存储至所述电压存储模块;

8、其中,所述目标压降值用于表征所述路径模拟模块模拟所述初始编程电压经所述选通电路时产生的压降值;

9、在电压补偿过程中,所述存储阵列处于编程状态,所述电压存储模块、所述电压处理模块、所述环路控制模块依次电连接;

10、所述电压处理模块用于将接收的预设参考电压,以及从所述电压存储模块中获取的所述目标压降值,输入至所述环路控制模块;

11、所述环路控制模块用于输出目标编程电压,以使所述存储阵列的输入端对应的电压等于所述目标编程电压,且到达所述存储阵列中对应的所述存储单元的实际编程电压等于所述初始编程电压;

12、其中,所述目标编程电压等于所述初始编程电压和所述目标压降值之和,所述预设参考电压与所述初始编程电压成预期比例关系。

13、本公开的编程电压控制电路,能够自动检测和补偿存储芯片工艺和温度的变化引起的编程时的电压降,实现了自动对目标压降值的精准检测,保证了目标编程电压的准确性;进而在存储阵列处于编程状态时,对存储阵列输入端对应的电压进行补偿,使得存储阵列的输入端对应的电压等于目标编程电压,且到达存储阵列中对应的存储单元的实际编程电压等于初始编程电压,消除了初始编程电压与实际编程电压之间的电压差,缩短了编程时长进而提高了编程效率,同时也提高了存储芯片的可靠性。

14、较佳地,所述环路控制模块包括第一输入端、第二输入端和电压输出端;所述路径模拟模块包括第一端和第二端;所述压降检测模块包括第一检测端、第二检测端和检测输出端;

15、在压降检测过程中,所述电压输出端分别与所述第一检测端及所述路径模拟模块的第一端电连接;

16、所述第二检测端及所述路径模拟模块的第二端分别与所述第二输入端及所述存储阵列的输入端电连接;

17、所述检测输出端与所述电压存储模块的输入端电连接;

18、在电压补偿过程中,所述电压存储模块的输出端与所述电压处理模块的第一端电连接,所述电压处理模块的第一端用于接收所述目标压降值,所述电压处理模块的第二端用于接收所述预设参考电压,所述电压处理模块的第三端与所述环路控制模块的所述第一输入端电连接;

19、所述环路控制模块的所述第二输入端和所述电压输出端电连接。

20、较佳地,所述路径模拟模块包括选通电路模拟单元和编程电流模拟单元;

21、所述选通电路模拟单元、所述压降检测模块的两端均分别与所述环路控制模块的两端电连接,所述选通电路模拟单元、所述压降检测模块和所述编程电流模拟单元均与所述存储阵列的输入端电连接;

22、其中,所述选通电路模拟单元用于模拟所述存储阵列中与任意一个存储单元的输入端连接的一个所述选通电路;

23、所述编程电流模拟单元用于模拟与所述选通电路模拟单元模拟的所述选通电路对应的所述存储单元。

24、较佳地,所述选通电路模拟单元包括开关模拟器件,所述开关模拟器件与所述选通电路中的选通开关的数量和器件规格相同;

25、和/或,所述编程电流模拟单元包括电流模拟器件;

26、所述电流模拟器件与所述存储单元的器件规格相同,或所述编程电流模拟器件为电流源,所述电流源提供的电流与所述存储单元对应的实际编程电流相同。

27、本公开的编程电压控制电路,由于的开关模拟器件与选通开关的数量和器件规格相同,电流模拟器件与存储单元的器件规格相同,所以能够实现自动精准检测和补偿由于工艺和温度的变化引起的电压降,准确控制到达memory cell的编程电压,进而提高了编程效率和可靠性。

28、较佳地,所述存储阵列包括n个所述存储单元、及与每个所述存储单元对应的所述选通电路,每个所述选通电路包括m个选通开关;

29、其中,n、m均为正整数;所述开关模拟器件包括m个所述选通开关;所述选通电路对应的电路结构与所述开关模拟器件对应的电路结构相同。

30、较佳地,所述选通电路对应3个依次连接的所述选通开关;

31、所述开关模拟器件包括3个依次连接的所述选通开关。

32、较佳地,所述编程电流模拟单元包括第一开关,所述编程电压控制电路还包括第二开关和第三开关;

33、所述第一开关连接在所述电流模拟器件和所述存储阵列的输入端之间;

34、所述第二开关连接在所述选通电路模拟单元的两端;

35、所述第三开关连接在所述电压处理模块和所述电压存储模块之间;

36、在压降检测过程中,所述第一开关处于闭合状态、所述第二开关处于断开状态且所述第三开关处于断开状态,所述环路控制模块用于接收所述初始编程电压,所述路径模拟模块用于模拟所述目标压降值,所述压降检测模块用于检测所述目标压降值,并将所述目标压降值存储至所述电压存储模块。

37、较佳地,在电压补偿过程中,所述第一开关处于断开状态、所述第二开关处于闭合状态且所述第三开关处于闭合状态;

38、所述电压处理模块用于叠加计算所述预设参考电压和所述目标压降值之和,以得到目标输入电压,并将所述目标输入电压输入至所述环路控制模块,以使所述环路控制模块输出所述目标编程电压。

39、较佳地,所述压降检测模块为电压传感器;

40、和/或,所述电压处理模块为加法器;

41、和/或,所述电压存储模块为电压保持器。

42、第二方面,还提供一种存储芯片,所述存储芯片包括上述的编程电压控制电路。

43、在符合本领域常识的基础上,上述各优选条件,可任意组合,即得本公开各较佳实例。

44、本公开的积极进步效果在于:

45、本公开的编程电压控制电路和存储芯片,能够自动检测和补偿存储芯片工艺和温度的变化引起的编程时的电压降,实现了自动对目标压降值的精准检测,保证了目标编程电压的准确性;进而在存储阵列处于编程状态时,对存储阵列输入端对应的电压进行补偿,使得存储阵列的输入端对应的电压等于目标编程电压,且到达存储阵列中对应的存储单元的实际编程电压等于初始编程电压,消除了初始编程电压与实际编程电压之间的电压差,缩短了编程时长进而提高了编程效率,同时也提高了存储芯片的可靠性。

- 还没有人留言评论。精彩留言会获得点赞!