一种具有HVBN结构的RESURFLDMOS器件的制作方法

一种具有hvbn结构的resurf ldmos器件

技术领域

[0001]

本发明属于功率半导体器件技术领域,更加具体地说,涉及一种具有hvbn结构的resurf ldmos器件。

背景技术:

[0002]

ldmos(laterally diffused metal oxide semiconductor)是一种横向双扩散结构功率器件,其源、漏、栅极都在芯片表面,易于与其它电路相集成,且耐压可以做的较高,因而在高压功率集成电路中较为常用。高压ldmos因兼容cmos与bcd工艺,具有工作电压高、工艺相对简单等优点,使其在汽车电子,电源管理,工业控制,电机驱动,家用电器等高压电路中有广泛的应用。但是高压ldmos的比导通电阻随着击穿电压的增加而以2.5次方的速度增加,导致其在超高压领域的应用受到极大的限制。目前对于高耐压功率ldmos的优化目标有两个:提高击穿电压和降低导通电阻。

[0003]

hvbn区的形成需要在注入深p阱之后,用离子注入技术注入杂质磷,注入能量为1.0mev,然后同深p阱一块退火后得到。漂移区的浓度对器件击穿电压非常敏感,正常在漏端施加电压使之击穿时,漂移区应完全耗尽才是最想要的结果。若漂移区注入剂量过高,会导致漂移区不能完全耗尽,随着器件漏端电压不断增加,电力线会在靠近沟道一侧聚集,导致器件栅场板下方的硅表面处发生击穿;若漂移区注入剂量过低,漂移区会过早完全耗尽,虽然在靠近沟道一侧得到保护,但电力线会随着漏端电压持续升高而在漏端附近聚集,导致漏端附近硅表面处发生击穿。为了避免这两种不良现象的发生,hvbn区很好的优化了漂移区的杂质分布,在漏端处较少的掺杂,漏端与沟道位置电场分布得到优化,使器件击穿发生在器件内部。

技术实现要素:

[0004]

本发明的目的在于克服现有技术中存在的击穿电压与导通电阻难以平衡的问题,提供一种具有hvbn结构的resurf ldmos器件,增加的hvbn区很好的优化了漂移区的杂质分布以及电场分布,使漂移区杂质浓度增大,导通电阻降低。

[0005]

本发明通过如下技术方案予以实现:

[0006]

一种具有hvbn结构的resurf ldmos器件,包括p型半导体衬底,在p型半导体衬底上设置深n阱和深p阱,在深p阱中设置p阱,源端n+区和源端p+区设置在p阱中且位于器件的表面;深n阱的上端面设置场氧化层,场氧化层的一端与漏端n+区相连,场氧化层的另一端设置栅氧化层和多晶硅栅;多晶硅栅设置在栅氧化层之上,两者共同延伸至器件表面的源端n+区;在深n阱中设置hvbn区、n阱、n top区和p top区,漏端n+区设置在n阱中且位于器件的表面;n top区设置在p top区之上,n top区由n型条和n型场限环组成,n型场限环设置在hvbn区内,n型条部分在hvbn区内,部分在深n阱中;p top区由p型条和p型场限环组成,p型场限环设置在hvbn区内,p型条部分在hvbn区内,部分在深n阱中。

[0007]

而且,在p阱的下面设置pb埋层,位于深p阱内,在pb埋层注入硼离子,注入宽度为

5-10μm,pb掺杂浓度为18

×

10

12-18.5

×

10

12

cm-2

。

[0008]

而且,器件表面采用二氧化硅层隔离。

[0009]

而且,n型场限环的数量为1-5;p型场限环的数量为1-5。

[0010]

而且,1/4-3/4的n型条在hvbn区内,1/4-3/4的n型条在深n阱中;1/4-3/4的p型条在hvbn区内,1/4-3/4的p型条在深n阱中。

[0011]

而且,n型条设置在p型条或者p型场限环之上,n型场限环设置在p型条或者p型场限环之上。

[0012]

而且,hvbn区注入磷离子,注入能量为0.5-1.5mev,掺杂浓度为7.5

×

10

11

cm-2

–

1.5

×

10

12

cm-2

。

[0013]

而且,p top区注入硼离子,n top区注入磷离子。

[0014]

而且,深n阱为漂移区,杂质浓度为3.0

×

10

12

cm-2

–

4.0

×

10

12

cm-2

,结深10-20um,漂移区长度为35μm-45μm。

[0015]

本发明的有益效果是:

[0016]

本发明采用工艺上十分容易实现的一种新型resurf技术,该resurf技术的漂移区顶部由p top区与n top区两部分组成。该技术致力于缓解横向功率器件,比如高压ldmos器件的导通电阻和击穿电压的矛盾关系,使得击穿不发生器件的表面而发生在器件内部。hvbn区的加入使漂移区杂质浓度更大,导通电阻更低,hvbn区分成两个区域也是为了形成一个浓度梯度,优化电场曲线,更好的辅助耗尽漂移区。hvbn区很好的优化了漂移区的杂质分布,即在漏端处较少的掺杂,漏端与沟道位置电场分布得到优化,使器件击穿发生在器件内部。增加n top区与p top区形成pn结辅助耗尽漂移区,使器件表面电场分布更平坦,从而提高了漂移区杂质浓度,降低了器件的导通电阻。除此之外,由于电子多从器件表面移动,n top区位于表面增加器件的导电通路,还巧妙的增加了漂移区浓度,使导通电阻在不牺牲击穿电压的前提下进一步下降,达到了优化器件的目的。

附图说明

[0017]

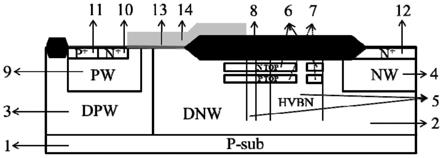

图1是本发明提供的具有hvbn结构的resurf ldmos器件结构示意图。

[0018]

图中:1是p型半导体衬底;2是深n阱(dnw);3是深p阱(dpw);4是n阱(nw);5是hvbn区;6是n top;7是p top;8是场氧化层;9是p阱(pw);10是源端n+;11是源端p+;12是漏端n+;13是栅氧化层;14是多晶硅栅。

[0019]

图2是实例1中具有hvbn结构的resurf ldmos器件的漏极电流随漏极电压变化的仿真结果图。

[0020]

图3是实例2中具有hvbn结构的resurf ldmos器件的漏极电流随漏极电压变化的仿真结果图。

[0021]

图4是实施例3所述的具有hvbn结构的resurf ldmos器件结构示意图。

[0022]

图中:1是p型半导体衬底;2是深n阱(dnw);3是深p阱(dpw);4是n阱(nw);5是hvbn区;6是n top;7是p top;8是场氧化层;9是pb埋层;10是p阱(pw);11是源端n+;13是源端p+;14是漏端n+;14是栅氧化层;15是多晶硅栅。

[0023]

图5是实施例3和实施例4所述resurf ldmos器件的不同pb长度与掺杂剂量对器件导通电阻的影响。

[0024]

图6是实施例3和实施例4所述resurf ldmos器件的不同pb长度与掺杂剂量对器件击穿电压的影响。

具体实施方式

[0025]

下面结合附图对本发明作进一步详细说明。

[0026]

实施例1

[0027]

如图1所示,本发明的一种具有hvbn结构的resurf ldmos器件,包括p型半导体衬底1,通过在单晶硅中注入杂质硼离子实现;在p型半导体衬底1上设置有深n阱2和深p阱3,也就是n型漂移区主体,采用离子注入技术注入磷离子实现;在深n阱2上设置有n阱4、hvbn区5、n top6(包含n型条和n型场限环,从器件结构示意图即截面图来看,n型条为矩形,整体相当于长方体;n型场限环为矩形环,整体相当于截面为矩形环的筒状结构)、p top7(包含p型条和p型场限环,从器件结构示意图即截面图来看,p型条为矩形,整体相当于长方体;p型场限环为矩形环,整体相当于截面为矩形环的筒状结构)和场氧化层8,其中不同的阱均为采用离子注入技术,注入不同浓度和能量实现的;在深p阱3上设有p阱9,p阱9的注入是为了降低寄生电阻,从而降低导通电阻,p阱9又包含形成欧姆接触的源端n+10和源端p+11;n阱4包含漏端n+12;上述深n阱2的上端面由下至上分别为栅氧化层13、多晶硅栅14。

[0028]

本发明具体工艺实现流程如下所述:

[0029]

(1)在单晶硅中注入硼离子,得到p型半导体衬底。

[0030]

(2)接下来是深n阱与深p阱的制备,深n阱是通过离子注入的方式在轻掺杂的p型半导体衬底上注入磷实现的,深p阱是注入硼实现的。

[0031]

(3)hvbn区的形成在注入深p阱之后,用离子注入技术注入杂质磷,注入能量为1.0mev,注入剂量为5.0

×

10

11

cm-2

,然后同深p阱一块退火后得到。

[0032]

(4)有源区场氧的形成是通过淀积氮化硅,然后用掩膜版在器件的表面刻蚀出氮化硅的窗口,该窗口即为有源区,再生长厚的场氧化层来实现的。

[0033]

(5)n阱与p阱的注入需要分别用三次离子注入技术来实现n阱区与p阱区。

[0034]

(6)p top区的形成也是通过离子注入技术注入硼离子实现,注入剂量为2.6

×

10

12

cm-2

。n top区的形成通过注入磷离子实现,注入的剂量为1.0

×

10

12

cm-2

。

[0035]

(7)下面是栅氧和多晶硅的形成,其中栅氧是结合干氧与湿氧两种工艺来形成的,保证了快速生长出高质量的栅氧。然后在器件表面淀积多晶硅,并刻蚀掉不需要的部分。

[0036]

(8)接下来是源端n+与源端p+的注入来形成欧姆接触,要求源端n+与源端p+具有很重的掺杂浓度才能使其具有小的电阻。源端n+与源端p+的形成分别需要两次离子注入来实现,注入的能量和剂量都不同,目的是为了降低源/漏与well之间的浓度梯度,减小漏电流的产生。

[0037]

(9)最后是接触孔的制备,金属化以及钝化工艺的形成。

[0038]

本实例所涉及的一种具有hvbn结构的resurf ldmos器件,图2为本实例器件的漏极电流随漏极电压变化的仿真结果图,此条件下器件的击穿电压值为617v,导通电阻值为8.69ω

·

mm2。

[0039]

实施例2

[0040]

本实施例与实施例1的不同之处在于:步骤(3)中hvbn区的注入的剂量改为7.5

×

10

11

cm-2

。图3为本实例器件的漏极电流随漏极电压变化的仿真结果图,增加hvbn区磷离子的注入后,器件的漂移区掺杂浓度变大,其导通电阻值降为8.05ω

·

mm2,但是器件的击穿电压值也发生降低,降为518v。

[0041]

实施例3

[0042]

本实施例与实施例1的不同之处在于:在p阱10的下面设置pb埋层9,如图4所示,pb埋层的实现通过注入硼离子实现,pb埋层的注入宽度为pb=8.3μm,pb掺杂浓度为18

×

10

12

cm-2

,此条件下器件的击穿电压值为593v,导通电阻值为7.1ω

·

mm2,如图5和图6。

[0043]

实施例4

[0044]

本实施例与实施例3的不同之处在于:pb埋层的注入宽度为pb=8μm,pb掺杂浓度取6

×

10

12

cm-2

,此条件下器件的击穿电压值为602v,导通电阻值为10ω

·

mm2,如图5和图6。此条件下虽然击穿电压有略微改善,但其极大损耗了导通电阻值,并不能达到良好的效果。

[0045]

以上对本发明做了示例性的描述,应该说明的是,在不脱离本发明的核心的情况下,任何简单的变形、修改或者其他本领域技术人员能够不花费创造性劳动的等同替换均落入本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1