一种IGBT器件的制作方法

本发明属于igbt器件技术领域,特别是涉及一种反向恢复速度可调的igbt器件。

背景技术:

igbt(绝缘栅双极型晶体管)器件是由mos晶体管和双极型晶体管复合而成的一种器件,其输入极为mos晶体管,输出极为pnp晶体管。现有技术的igbt器件的导通和关断由栅极-发射极电压控制,当栅极-发射极电压大于mos晶体管的阈值电压vth时,mos晶体管内部形成电流沟道并为双极性晶体管提供基极电流,使得igbt器件导通。当栅极-发射极电压小于mos晶体管的阈值电压vth时,mos晶体管内的电流沟道会被关断,双极性晶体管的基极电流被切断,从而igbt器件被关断。现有技术的igbt器件在关断时,当集电极-发射极电压小于0v时,igbt器件中寄生的体二极管处于正偏压状态,反向电流从发射极经体二极管流至集电极,此时体二极管的电流存在注入少子载流子现象,而这些少子载流子在igbt器件再一次开启时进行反向恢复,导致较大的反向恢复电流,反向恢复时间长。

技术实现要素:

有鉴于此,本发明的目的是提供一种反向恢复速度可调的igbt器件,以解决现有技术中的igbt器件因少子载流子注入问题造成的反向恢复时间长的技术问题。

本发明实施例提供的一种igbt器件,包括:

n型集电极区和p型集电极区,位于所述n型集电极区和所述p型集电极区之上的n型漂移区,以及由多个mosfet单元组成的mosfet单元阵列,所述mosfet单元包括:

位于所述n型漂移区顶部的p型体区,位于所述p型体区内的n型发射极区,位于所述p型体区之上的栅极结构,所述栅极结构包括栅介质层、栅极和n型浮栅,所述栅极和所述n型浮栅位于所述栅介质层之上,且所述栅极位于靠近所述n型发射极区的一侧,所述n型浮栅位于靠近所述n型漂移区的一侧,所述栅极通过电容耦合作用于所述n型浮栅;

在所述mosfet单元阵列中,至少有一个所述mosfet单元的所述n型浮栅通过所述栅介质层与所述p型体区隔离,且至少有一个所述mosfet单元的所述n型浮栅通过一个位于该n型浮栅下方的栅介质层中的开口与所述p型体区接触形成p-n结二极管。

可选的,本发明的igbt器件,还包括位于所述n型集电极区和所述p型集电极区之上的n型场截止区,所述n型场截止区位于所述n型漂移区下方。

可选的,本发明的igbt器件,所述栅极延伸至所述n型浮栅之上。

可选的,本发明的igbt器件,所述栅极伸至所述n型浮栅之上且覆盖所述n型浮栅靠近所述n型漂移区一侧的侧壁。

可选的,本发明的igbt器件,所述开口位于所述n型浮栅下方且靠近所述n型漂移区的一侧。

可选的,本发明的igbt器件,至少有一个所述mosfet单元的栅极与所述n型发射极区电性连接。

本发明实施例提供的一种igbt器件,通过控制形成有p-n结二极管的mosfet单元的数量,可以方便且准确的调整igbt器件的反向恢复速度,使得igbt器件具有更广泛的应用;同时,在调整形成有p-n结二极管的mosfet单元的数量时,只需要通过修改用于形成栅介质层中的开口的一块掩膜版即可,这可以有效控制igbt器件的制造成本。

附图说明

为了更加清楚地说明本发明示例性实施例的技术方案,下面对描述实施例中所需要用到的附图做一简单介绍。

图1是本发明提供的一种igbt器件的第一个实施例的剖面结构示意图;

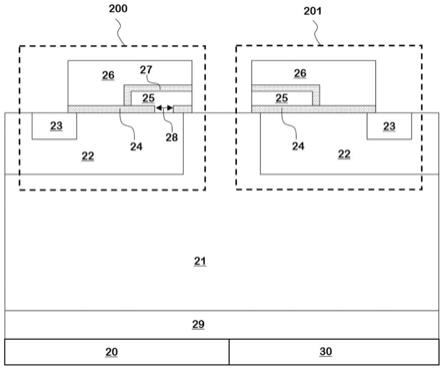

图2是本发明提供的一种igbt器件的第二个实施例的剖面结构示意图。

具体实施方式

以下将结合本发明实施例中的附图,通过具体实施方式,完整地描述本发明的技术方案。同时,为清楚地说明本发明的具体实施方式,说明书附图中所列示意图,放大了本发明所述的层和区域的尺寸,且所列图形大小并不代表实际尺寸。说明书中所列实施例不应仅限于说明书附图中所示区域的特定形状,而是包括所得到的形状如制备引起的偏差等。

图1是本发明提供的一种igbt器件的第一个实施例的剖面结构示意图,如图1所示,本发明实施例提供的一种igbt器件包括n型集电极区20和p型集电极区30,位于n型集电极区20和p型集电极区30之上的n型场截止区29,位于n型场截止区29之上的n型漂移区21,以及由多个mosfet单元组成的mosfet单元阵列,图1中示例性的示出了两个mosfet单元(mosfet单元200和mosfet单元201)。

本发明实施例的mosfet单元包括:位于n型漂移区21顶部的p型体区22,位于p型体区22内的n型发射极区23;位于p型体区22之上的栅极结构,该栅极结构包括栅介质层24、n型浮栅25和栅极26,栅极26位于栅介质层24之上且靠近n型发射极区23的一侧且栅极26向n型漂移区21的一侧延伸至n型浮栅25之上,n型浮栅25位于栅介质层24之上且靠近n型漂移区21的一侧,栅极26和n型浮栅25由绝缘介质层27隔离,栅极26通过电容耦合作用于n型浮栅25。绝缘介质层27通常为二氧化硅。

本发明实施例的mosfet单元阵列中,至少有一个mosfet单元的n型浮栅25通过栅介质层24与p型体区22隔离(如图1中的mosfet单元201),且至少有一个mosfet单元的n型浮栅25通过一个位于该n型浮栅25下方的栅介质层24中的开口28与p型体区22接触形成p-n结二极管(如图1中的mosfet单元200)。

本发明实施例中的mosfet单元的栅极26可以仅位于靠近n型发射极区23的一侧,即在横向上,栅极26和n型浮栅25左右设置(本发明实施例中未展示),也可以是栅极26位于靠近n型发射极区23的一侧并向n型漂移区21的一侧延伸至n型浮栅25之上(如图2所示),栅极26延伸至n型浮栅25之上,可以增大栅极26覆盖n型浮栅25的面积,增大栅极26对n型浮栅25的电容耦合率。

本发明实施例的一种igbt器件,在正向阻断状态时,n型集电极区20和p型集电极区30被施加高电压,mosfet单元200中的由n型浮栅25与p型体区22形成的p-n结二极管被正向偏置,mosfet单元200中的n型浮栅25被充入正电荷,这使得mosfet单元200中的n型浮栅25下面的电流沟道的阈值电压vht1降低。mosfet单元200中的n型浮栅25的电压与位于栅介质层24中的开口28的位置有关,可选的,位于栅介质层24中的开口28位于n型浮栅25下方且靠近n型漂移区21的一侧,由此可以使n型浮栅25更容易的被充入正电荷。

本发明实施例的igbt器件在正向阻断状态和正向开启状态时,集电极-发射极电压vce大于0v,mosfet单元200中的n型浮栅25下面的电流沟道的阈值电压vht1对整个mosfet单元200的阈值电压vth的影响很低,mosfet单元200仍具有高阈值电压vth。本发明实施例的igbt器件在关断时,当发射极-集电极电压vec大于0v时,mosfet单元200中的n型浮栅25下面的电流沟道的阈值电压vht1对整个mosfet单元200的阈值电压vth的影响很大,使得mosfet单元200具有低阈值电压vth,从而使mosfet单元200的电流沟道在低栅极电压(或0v电压)下开启,从而能够增加流过mosfet单元200的反向电流,减少流过igbt器件中寄生的体二极管的电流,提高整个igbt器件的反向恢复速度。

本发明实施例提供的一种igbt器件,通过控制mosfet单元阵列中形成有p-n结二极管的mosfet单元的数量,可以方便且准确的调整igbt器件的反向恢复速度,使得igbt器件具有更广泛的应用;同时,在调整形成有p-n结二极管的mosfet单元的数量时,只需要通过修改用于形成栅介质层中的开口的一块掩膜版即可,这可以有效控制igbt器件的制造成本。

本发明实施例的igbt器件的mosfet单元阵列中,可以使得至少一个mosfet单元的栅极26与n型发射极区23电性连接,即该部分栅极26接发射极电压,这可以降低igbt器件的栅电荷。

图2是本发明提供的一种igbt器件的第二个实施例的剖面结构示意图,与图1所示的本发明实施例的igbt器件结构不同的是,本实施例中的igbt器件中,mosfet单元的栅极26向n型漂移区21的一侧延伸至n型浮栅25之上且覆盖n型浮栅25靠近n型漂移区21一侧的侧壁,由此可以进一步增大栅极26覆盖n型浮栅25的面积,进而能够增大栅极26对n型浮栅25的电容耦合率。

以上具体实施方式及实施例是对本发明技术思想的具体支持,不能以此限定本发明的保护范围,凡是按照本发明提出的技术思想,在本技术方案基础上所做的任何等同变化或等效的改动,均仍属于本发明技术方案保护的范围。

- 还没有人留言评论。精彩留言会获得点赞!